- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- MCUXpresso Software and Tools

- :

- Kinetis Software Development Kit

- :

- I2S KSDK driver is working?

I2S KSDK driver is working?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

I2S KSDK driver is working?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

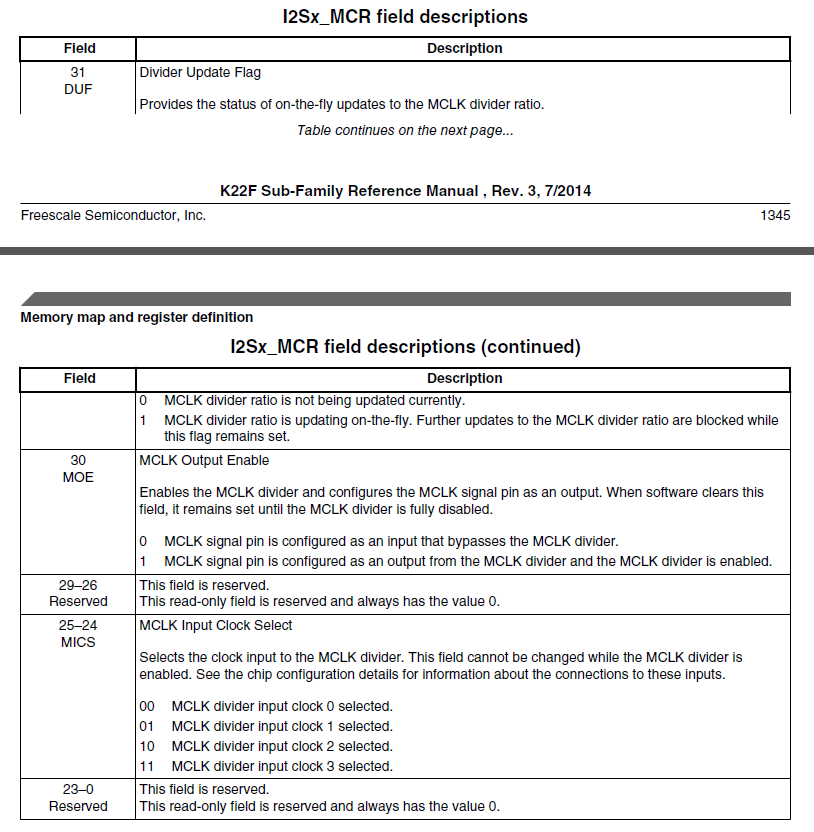

I'm trying to use I2S module from MK22FN512 in FRDM-K22F board, with the KSDK + Processor expert.

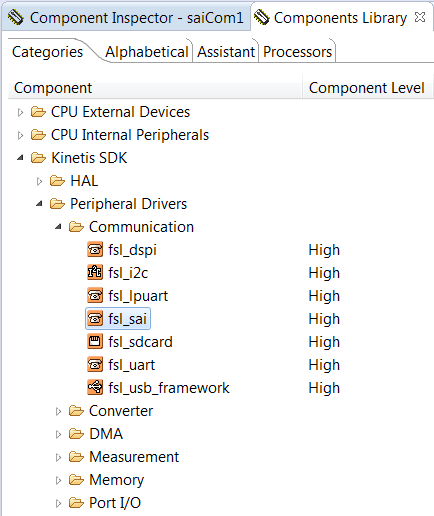

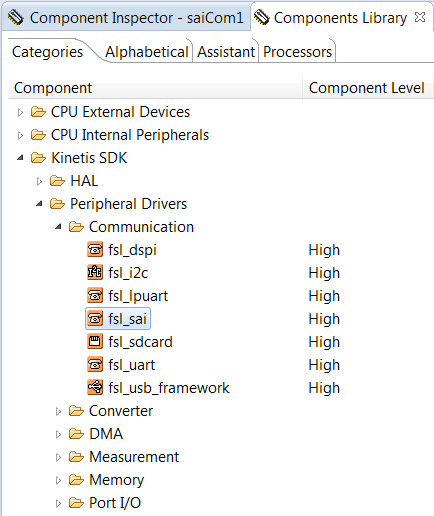

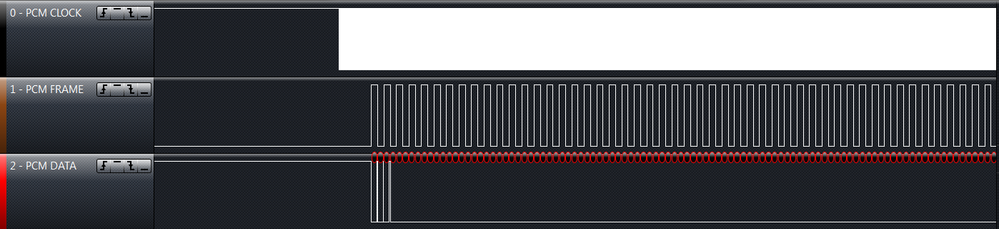

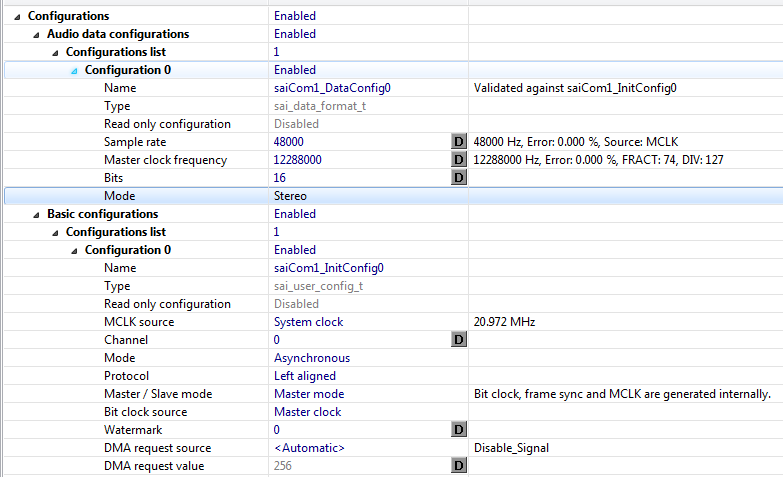

I used the fsl_sai component as shown in the figure below:

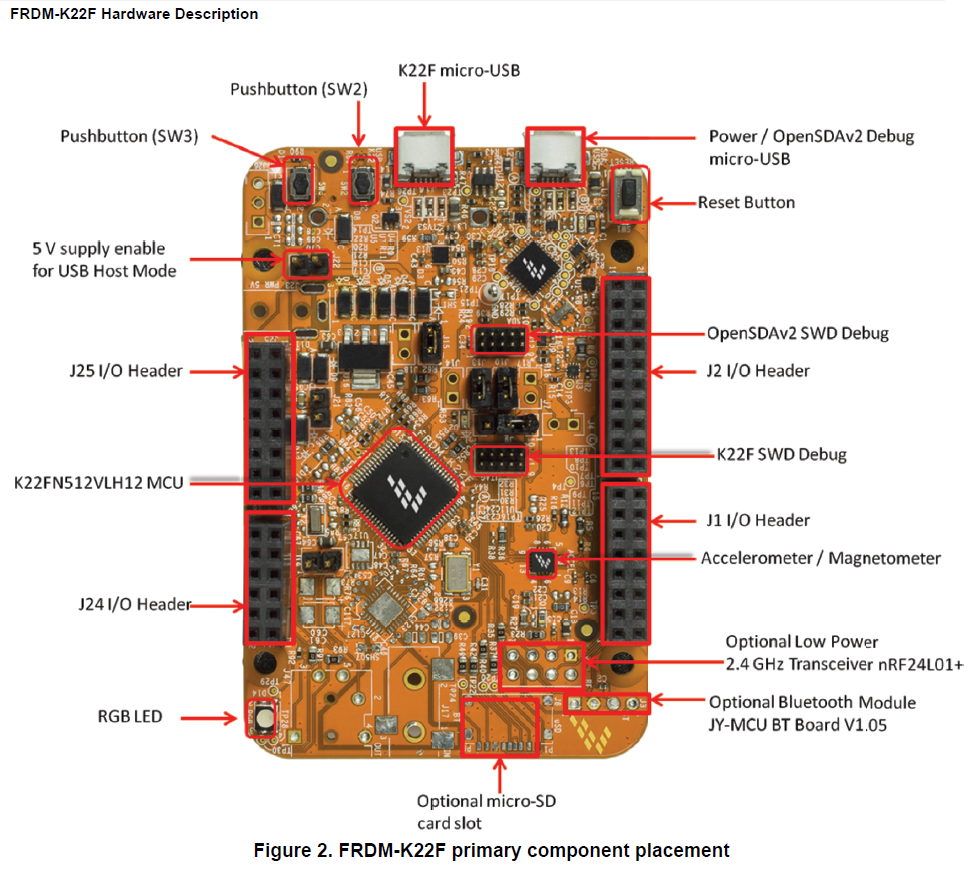

Basically I used the bean's default settings. However, the program is stuck in a line code generated by the PE.

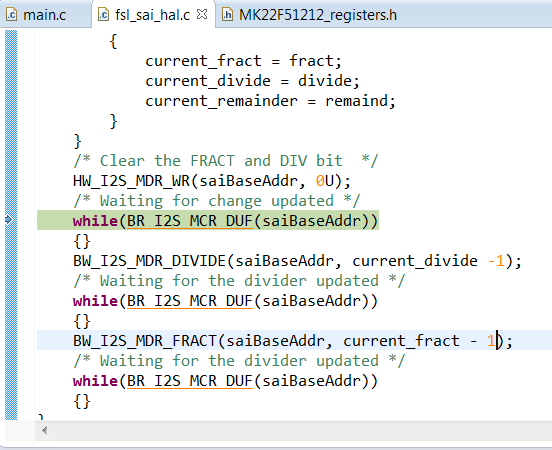

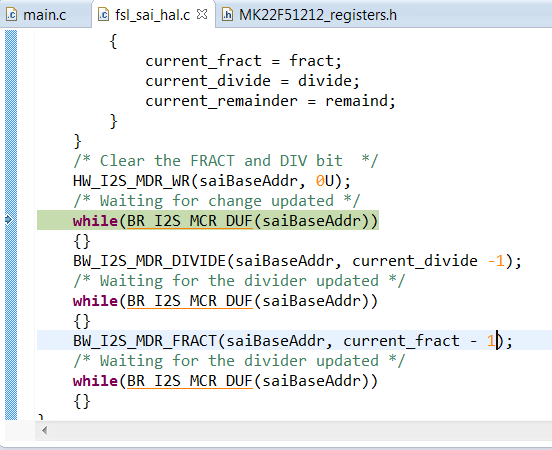

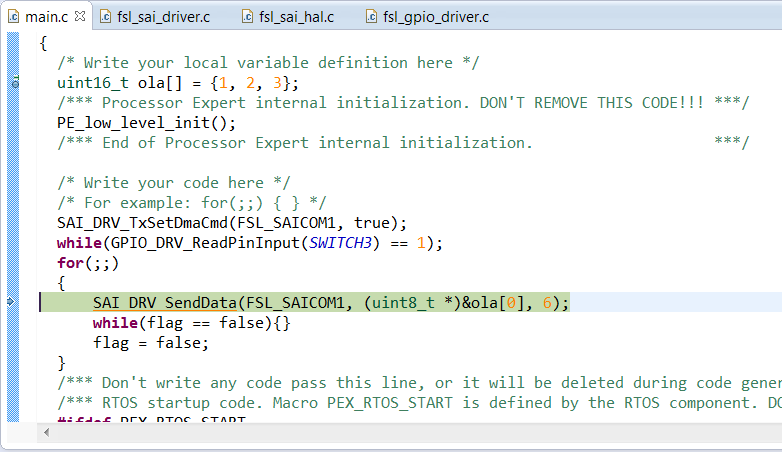

The line of code are highlighted in the figure below.

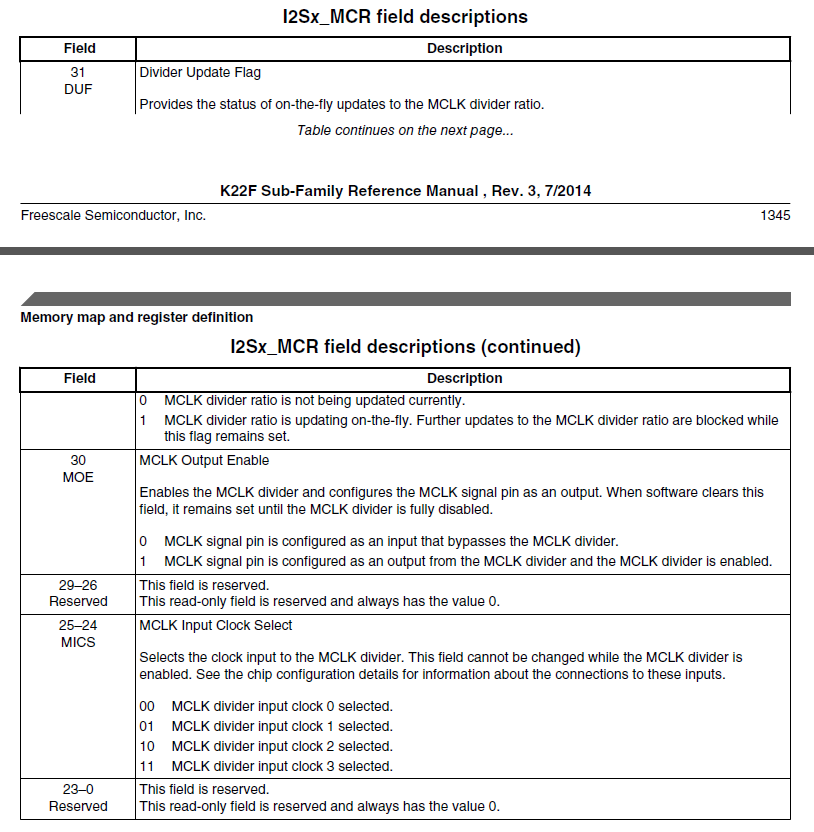

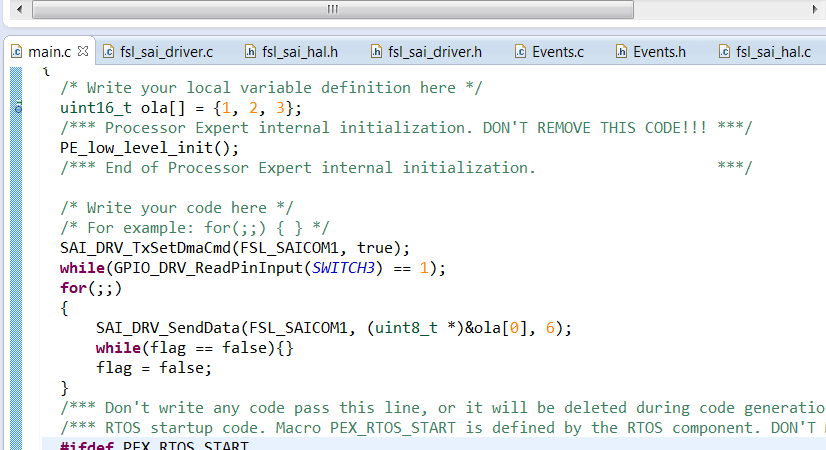

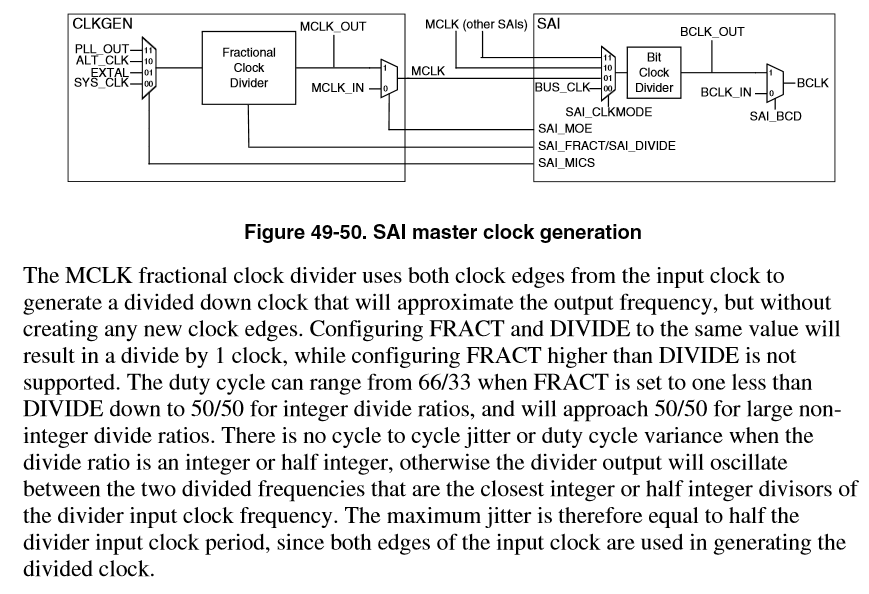

As can be seen in the next figure extracted from the device's manual, it is a register indicating whether the device clock may or

not be updated.

The code appears to have been poorly designed, should not get stuck in this condition. What can I do? Programming using registers?

Freescale does not seem to give much support for I2S module.

Thanks,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Matheus,

please, can you upload your project?

I will test it on my side.

Best Regards,

Iva

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Matheus,

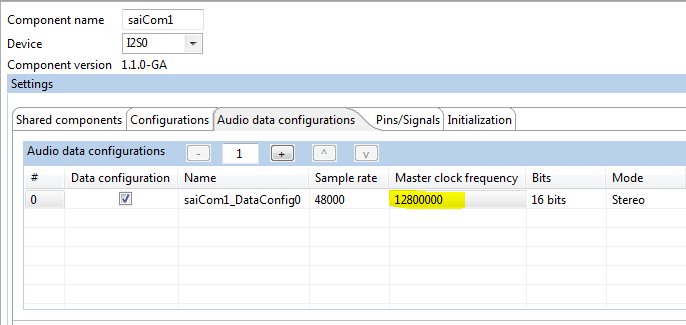

Your CPU component has Core clock and Bus clock frequency 20.97152 MHz thus MCLK divider in the SAI peripheral can't divide this frequency to 24.576 MHz. You can increase the CPU frequency or decrease the Master clock frequency value in the fsl_sai component. For example MCLK 12288000 Hz will work.

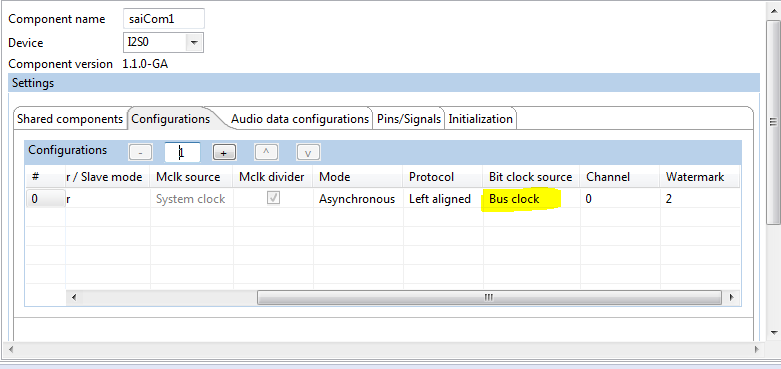

You can also increase the Sample rate accuracy by changing the Bit clock source from Bus Clock to Master clock in the saiCom1_InitConfig0 configuration.

Unfortunately fsl_sai component for the KSDK 1.1.0 has no timing validations. We've added I2S timing validations into KSDK 1.2.0 service pack which will be available soon.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks Iva,

The program pass this code lines.

I did not find material about KSDK API. Everthing that I found in the link below is too shallow.

Software Development Kit for Kinetis MCUs|Freescale

Now I cant go on, beacuse some drawbacks. I make a new code for test that is attached, to anyone who has a FRDM K22F, and a logic analizer, can test.

First, I press the switch 3 in the board to begin the communication, which is shown in figure below.

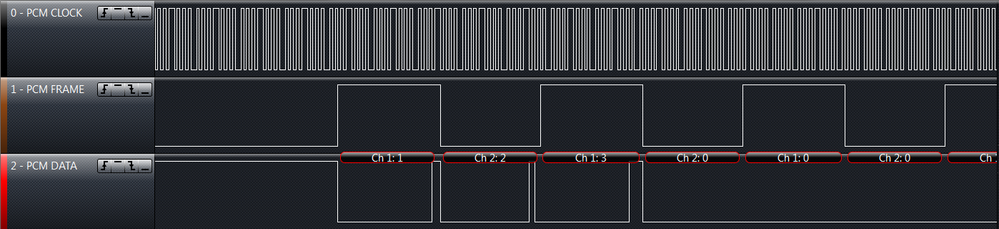

I send a block with 3 values to I2S module, which can be observed in the code of the figure below.

First, I set the DMA communication and after wait for the press of SW3. When pressed, a loop sends the block forever. The block must be sent after a block complete sent flag be set in a interrupt. That flag is set correctly how confirmed in debug.

However, it can be seen in the waves from the figure below, that the block is sent just one time.

Looking more closely, we can see that is the block: fisrt the number 1, after 2, after 3.

In the debug I noticed that the code gets stuck when tries send the block for the second time, which can be observed in the figure below.

Even pressing "F5" button, step into, the debug stop here.

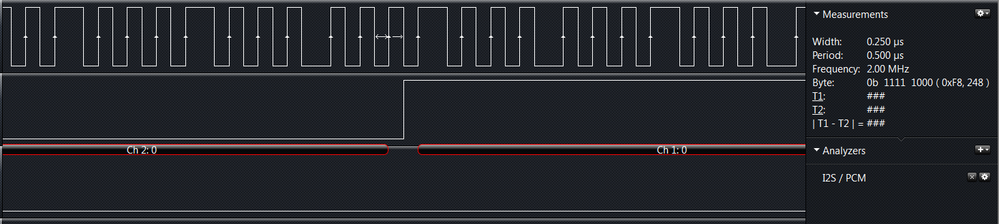

Can be saw too in the figure below, that the "bit clock frequency" is irregular.

As can be seen, set I2S module without support is a headache.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Matheus,

New Kinetis Design Studio and Kinetis SDK v1.2 with updated fsl_sai driver is available for download.

New Kinetis Design Studio V3.0.0 available

Ondrej

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Matheus,

1. In most cases MCLK should be multiple of Bit clock, for 48 kHz sample rate eg. 12288000 Hz and not 1280000 Hz

2. If you need MCLK and Bit clock aligned (eg. for delta-sigma DAC) select MCLK as Bit clock source. Not Bus clock.

3. MCLK frequency is generated from the internal System clock. System clock in this situation is not multiple of MCLK. It may have impact to MCLK duty cycle and also for bit clock (in case it is generated from the MCLK). As RM says :

You can also use external MCLK clock source for better precision and very low jitter.

Best Regards,

Ondrej

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ondrej,

Your suggestion did not work out. The result was the same when I used the master clock to 1280000 Hz and the source of the clock bit as the clock bus.

However, when I set a frequency of 10000000 Hz and a sample rate of 5000 worked perfectly! But I dont know why it worked so...

Any suggestion?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Matheus,

I've set MCLK to 12 288 000 Hz, as Bit clock source MCLK, enabled the MCLK pin. Measured bit clock looks ok 48000* 16 bits * 2 channels = 1 536 000 Hz.

I've increased CPU clocks and changed the mode to PEE. PEE uses external 8 MHz crystal. Now I can see data packets on the TX line periodically. Driver works in interrupt mode. With 20 MHz core clock I've seen several FIFO underrun errors.

Attached project with updated code and clock settings.

I recommend KSDK 1.2.0 for new i2s projects.

Ondrej