- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- SRAM using EIM in a iMX6

SRAM using EIM in a iMX6

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

SRAM using EIM in a iMX6

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi all,

We're connecting a 4MB Static RAM using the EIM interface in a custom iMX6 board.

We are trying to set a filesystem in that SRAM.

The kernel version is from yocto 3.10.53. We're only using the pins:

- EIM_CS0_B

- EIM_OE_B

- EIM_RW

- EIM_DATA00 to EIM_DATA15

- EIM_AD00 to EIM_ADDR21

and in DTS we have:

/*https://www.kernel.org/doc/Documentation/devicetree/bindings/bus/imx-weim.txt*/

&weim {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_weim_ram_1 &pinctrl_weim_cs0_1>;

#address-cells = <2>;

#size-cells = <1>;

/* <cs-number> 0 <physical address of mapping> <size> = size 64MB -> addr=22 pins*/

ranges = <0 0 0x08000000 0x008000000>;

status = "okay";

sram@0,0 {

compatible = "mtd-ram";

reg = <0 0 0x00400000>;

#address-cells = <1>;

#size-cells = <1>;

bank-width = <2>;

/* EIM_CSnGCR1, EIM_CSnGCR2, EIM_CSnRCR1, EIM_CSnRCR2, EIM_CSnWCR1, EIM_CSnWCR2 */

fsl,weim-cs-timing = <0x403184B1 0x00001010 0x14017000

0x00000000 0x14000E00 0x00000000>;

};

};

I have three question:

1) To use the SRAM as a block device where we can set a filesystem the "mtd-ram" is the correct choice?

With the next command we can see the device recognized

# cat /proc/mtd

2) With that configuration we can see signals in the scope but if we try to make a fs in the block device related

we get an error. Is this correct?

# mkfs.ext2 /dev/mtdblock0

# mount /dev/mtdblock0 kk/

We have a SPI device too and the previous commands works ok.

3) Are there very obvious mistakes in this weim DTS definition we are not catching?

Any info is welcome, thanks!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

We have a SPI device too and the previous commands works ok.

Do you have an SPI SRAM device in your board? If so, could you please share

- which product it is

- what driver you are using

- device-tree entry

I would very much appreciate that.

Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

- We have a M25P32

- driver: options in kernel

CONFIG_MTD_RAM=y

CONFIG_MTD_PHYSMAP_OF=y

CONFIG_MTD_M25P80=y

- device tree:

+&ecspi1 {

+ fsl,spi-num-chipselects = <1>;

+ cs-gpios = <&gpio3 19 0>;

+ pinctrl-names = "default";

+ pinctrl-0 = <&pinctrl_ecspi1_1>;

+ status = "okay";

+

+ flash: m25p32@0 {

+ #address-cells = <1>;

+ #size-cells = <1>;

+ compatible = "st,m25p32";

+ spi-max-frequency = <20000000>;

+ reg = <0>;

+ };

+};

+

+&weim {

+ pinctrl-names = "default";

+ pinctrl-0 = <&pinctrl_weim_ram_1 &pinctrl_weim_cs0_1>;

+ #address-cells = <2>;

+ #size-cells = <1>;

+ /* <cs-number> 0 <physical address of mapping> <size> = size 64MB -> addr=22 pins*/

+ ranges = <0 0 0x08000000 0x008000000>;

+ status = "okay";

+

+ sram@0,0 {

+ compatible = "mtd-ram";

+ reg = <0 0 0x00400000>;

+ #address-cells = <1>;

+ #size-cells = <1>;

+ bank-width = <2>;

+ /* EIM_CSnGCR1, EIM_CSnGCR2, EIM_CSnRCR1, EIM_CSnRCR2, EIM_CSnWCR1, EIM_CSnWCR2 */

+ fsl,weim-cs-timing = <0x40B184B1 0x00001010 0x14017000

+ 0x00000000 0x14000E00 0x00000000>;

+ };

+};

Hope it helps!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for your quick reply.

We are planning to use 23LCV1024 SPI SRAM from Microchip. I couldn't find a specific driver for it so I'm looking for something to start with.

I had thought maybe you were using something similar, rather than a flash memory. But thanks anyway, it will be very helpful.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi all,

Finally the solution come from changing the values of 'fsl,weim-cs-timing'. All the other things are ok.

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I have also some trouble with my external SRAM, could you please give your corrected timing fsl,weim-cs-timing configuration ?

I am able to have correct individual access, but as soon as I try to get fast consecutive access, I have a big dead time of around 380ns between two readings, and 360ns between two writings.

Thanks a lot.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Poussemousse,

Sorry for the delay! We're facing similar issues. We have right consecutive reads but consecutives writes we can

see long delays like you. Our weim and sram configuration is:

&weim {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_weim_ram_1 &pinctrl_weim_cs0_1>;

#address-cells = <2>;

#size-cells = <1>;

/* <cs-number> 0 <physical address of mapping> <size> = size 64MB -> addr=22 pins*/

ranges = <0 0 0x08000000 0x008000000>;

status = "okay";

sram@0,0 {

compatible = "mtd-ram";

reg = <0 0 0x00400000>;

#address-cells = <1>;

#size-cells = <1>;

bank-width = <2>;

/* EIM_CSnGCR1, EIM_CSnGCR2, EIM_CSnRCR1, EIM_CSnRCR2, EIM_CSnWCR1, EIM_CSnWCR2 */

fsl,weim-cs-timing = <0x00010CB1 0x00001010 0x0C015100

0x00000000 0xCC1C7640 0x00000000>;

};

};

It seems that the writing delay match the weim watchdog time. Once the watchdog is fired the write is done.

Have you solve the issue??

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thank you for your feedback, unfortunately it doesn't solve our problem.

Using iMX6S, we are interfacing a 16bits parallel 45ns asynchronous SRAM, and the only way to have consecutive accesses without dead time is to widen the bus.

EIM bus registers :

EIM_CS1GCR1 00010001

EIM_CS1GCR2 00000000

EIM_CS1RCR1 03000000

EIM_CS1RCR2 00000008

EIM_CS1WCR1 03000000

EIM_CS1WCR2 00000000

I explain :

With a 16 bits configuration : reading or Writing 2 different words of 16 bits, imply to wait for about 250/280ns between the 2 accesses.

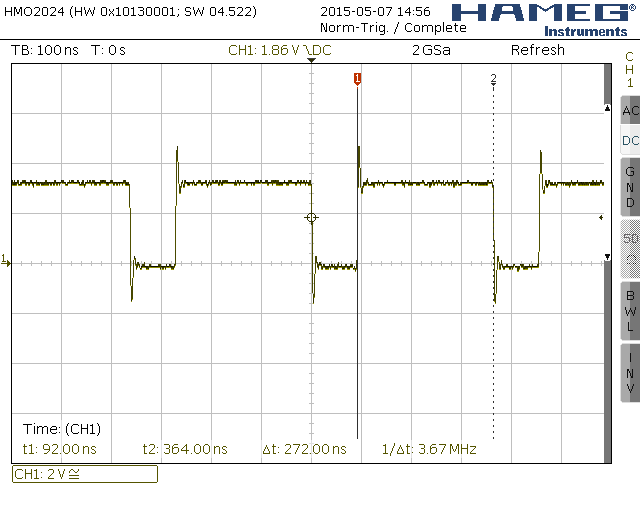

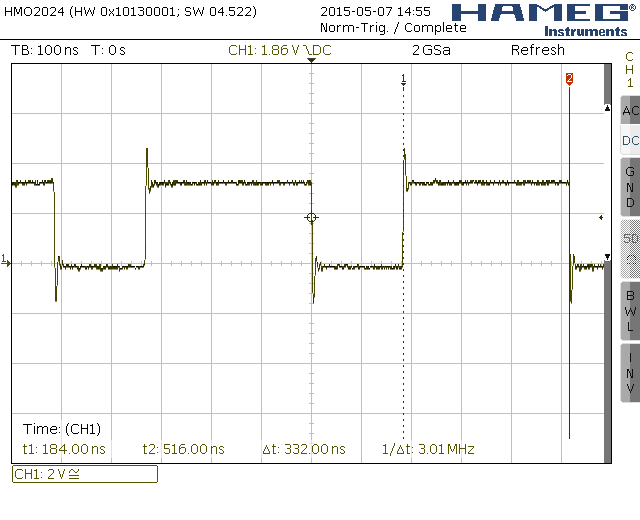

In the following pictures, we observe CS signal.

With a 32 bits configuration : reading 2 different words of 16 bits, through 2 consecutive accesses doesn't any dead time (90ns time = 2 very consecutive access of our 45ns SRAM) , but than we have to wait again for about 270ns between the 2 words of 32 bits.

With a 64 bits configuration: writing 1 words of 64bits = 4x 16bits word, through 4 consecutive accesses doesn't any dead time (180ns = 4x45ns) , but then we have to wait again for about 332ns for next 64 bits word Write

We are wondering if it is due to internal bus Exchange into the iMx6 which could explain this pain.

Any help would be very appreciated.

Poussemousse

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Please refer to chapter "EIM NOR Driver" of "i.MX_6_Linux_Reference_Manual.pdf".

In particular :

"Similar to the SPI NOR, the parallel NOR uses the MTD subsystem. Because the parallel

NOR is very small, you may only use the jffs2 but cannot use the UBIFS for it."

and

"Add weim-nor to the kernel command line to enable the WEIM NOR. The WEIM NOR

has pin conflict with some other modules, such as the SPI."

Have a great day,

Yuri

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------