- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- EIM DTACK Mode

EIM DTACK Mode

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

EIM DTACK Mode

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi all,

we want to use the EIM for communication between the i.MX processor and an FPGA.

- The accesses are single word, that is why we use the asynchronous mode, single read (SRD=0, SWR=0, APR=0).

- The accesses are of different latency, that is why we want to use DTACK mode and terminate each access on the assertion of the EIM_DTACK signal.

Now I have the following problem:

EIM ignores the DTACK signal, even though DAE is enabled. The length of a read access is always defined by RWSC. Is there any other bit that needs to be configured so that each access is terminated on assertion of EIM_DTACK?

Best regards

Alex

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Doerflinger

selection of DTACK polling can be choosed with

EIM_CSnGCR2 field DAPS - bit field determine the starting point of DTACK

input signal polling, sect. 22.9.2 IMX6DQRM

RWSC time is min.length access time (Figure 22-2. Read Access)

which can be prolonged using DTACK, that is EIM starts to poll DTACK

after RWSC time. From sect.22.1.2.2 Asynchronous Page Read Mode:

"The initial access timing is according to RWSC field..".

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Igor,

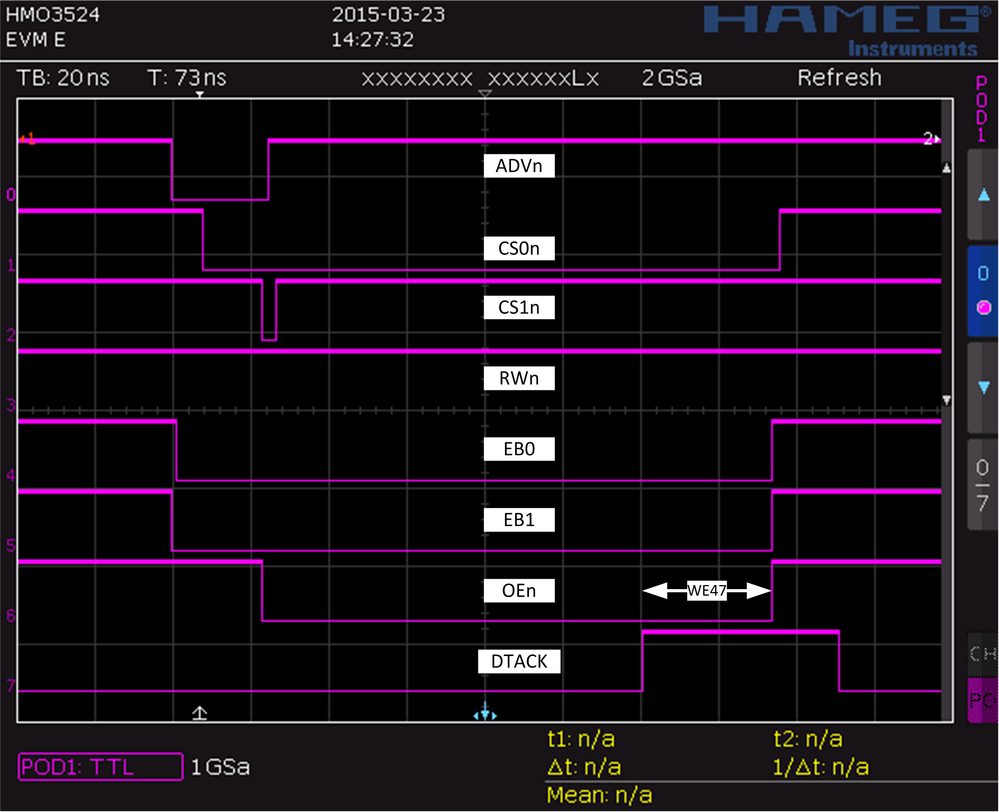

thanks for your reply. In our configuration the EIM now reacts on the DTACK signal, but I still don't really understand the timing between DTACK assertion and CS idle. We use the following configuration:

Asynchronus Multiplexed Mode (MUM=1, SRD=0, SWR=0)

DAPS = 0

CS Assertion is delayed one cycle (RCSA=001, WCSA=001)

Measurements with the oscilloscope show that the time between these signals is 30ns +-3ns. The time should be equal to WE47 in Figure 22 (DTACK Mode Read Access) of IMX6DQCEC. This datasheet quotes that WE47 = MAXCO - MAXCSO + MAXDTI. In order to optimize the EIM timing for maximum bandwidth, I have two questions:

1. How do I calculate the latency between DTACK active and CS idle? I suppose it should be: WE47 = Sync Time + max. one cycle synchronizing DTACK = max. 3 ACLK cycles = 22.5ns with a 133MHz clock. Is that correct? Why do I get 30ns +-3ns?

2. The datasheet IMX6DQCEC quotes that MAXDTI = 10. I suppose this should be MAXDTI = 2*ACLK cycles + 10ns. Is that correct?

3. The impact of RWSC is a little strange. You mentioned, that it is the min. access time length. I observed, that WE47 = 30ns +-3ns + RWSC * ACLK period. For maximum performance I chose RWSC = 0, which works even though RWSC = 0 is a reserved value (IMX6QRM, 22.9.3). Is this ok, or would you not recommend to use the reserved value?

4. Is ACLK in IMX6QRM, Figure 22-16, the same as EIM clock mentioned in the EIM Register Definition (EIM clock cycles before..., chapter 22.9)?

Best regards

Alex

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Igor,

thanks again for your help.

1. Sorry I was not specific enough. I meant "latency between DTACK assertion and CS idle", the time marked as WE47 in the picture and as it is named in IMX6DQCEC, Figure 22. In IMX6DQCEC it shows, that WE47 = MAXCO - MAXCSO + MAXDTI. This I cannot reconstruct. I did observe, that a possible calculation would be WE47 = max. one cycle synchronizing DTACK + MAXDTI + RWSC*ACLK period= max. 1*ACLK + (2*ACLK period + 10ns) + RWSC*ACLK period. Why does RWSC influence WE47? This does not correspond to IMX6QRM, 22.9.3, and IMX6QRM, Figure 22-16.

2. Thanks for your confirmation!

3. I know RWSC=0 is reserved. But RWSC=0 seems to work and leads to the shortest WE47 latency. Is this ok, or would you not recommend to use the reserved value?

4. When comparing the assertion of the EIM control signals, I can measure that EIM clock = 133MHz. This frequency is also quoted in IMX6QRM, 22.1.2.4. But you are right, in IMX6SDLCEC, 4.9.3, it says that the root clock is 132MHz, and the EIM operating clock is max. 104MHz. Now I'm a little bit confused. Can throw some light on this toppic?

Thanks a lot so far!

Best regards

Alex

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Alex

1.4. Maximum operating frequency for EIM data transfer is 104 MHz.

This frequency is obtained from silicon characterization.

So maximum frequency for ACLK is 104 MHz. Your previous measurements were with ACLK =133 MHz,

so you should set ACLK < 104 MHz and recheck once more

3. It is not recommend to use the reserved value.

Best regards

igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Alex

1. what is definition of "latency between DTACK active and CS idle" ?

2. correct

3. RWSC = 0 is a reserved value

4. yes. All clocks are derived from ACLK_EIM_SLOW_CLK_ROOT (max. 132 MHz).

From IMX6SDLCEC sect.4.9.3 External Interface Module (EIM) (with same EIM as i.MX6DQ):

Maximum operating frequency for EIM data transfer is 104 MHz.

The maximum frequency for ACLK is 104 MHz.

Best regards

igor