- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- Too High Sleep current with RTC

Too High Sleep current with RTC

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi all

I measure a power cunsumption of about 2-3 uA without RTC when ti uC is in LLS-Mode ( measured on J4, FRDM-KL25Z ). As soon as I have the RTC running the current consumption is about 23-24 uA. I see in the datasheet that I_RTC should be between 432 and 810 nA - much smaller then 20 uA. If I dont have the RTC-Clock connected to PTC1 the current consumption is ok even if the RTC-Module is enabled.

Does anyone know what is wrong here?

Thank you for any hint .. Dominic

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

It is probably a hardware issue. My RTC-Clock signal is not very nice (but event not very bad!). Having a nice clock generated by a Clock-Generator I dont measure the current penalty anymore. So my problem is basically solved but if anyone knows why the bad clock signal results in an increased current consumptin I am very interested in!

Thank you all! Dominic

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hm, I see that the RTC component is not required for the high power consumption. As soon as I have RTC clock input enabled and I have a 32.768 kHz clock attached to PTC1 the power consomption in LLS-Mode jumps from 2-3 uA to 23-24 uA. I dont see why :-( Does anyone know?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Can we assume that you have the 32K oscillator section set to the 'lowest power' oscillation mode?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

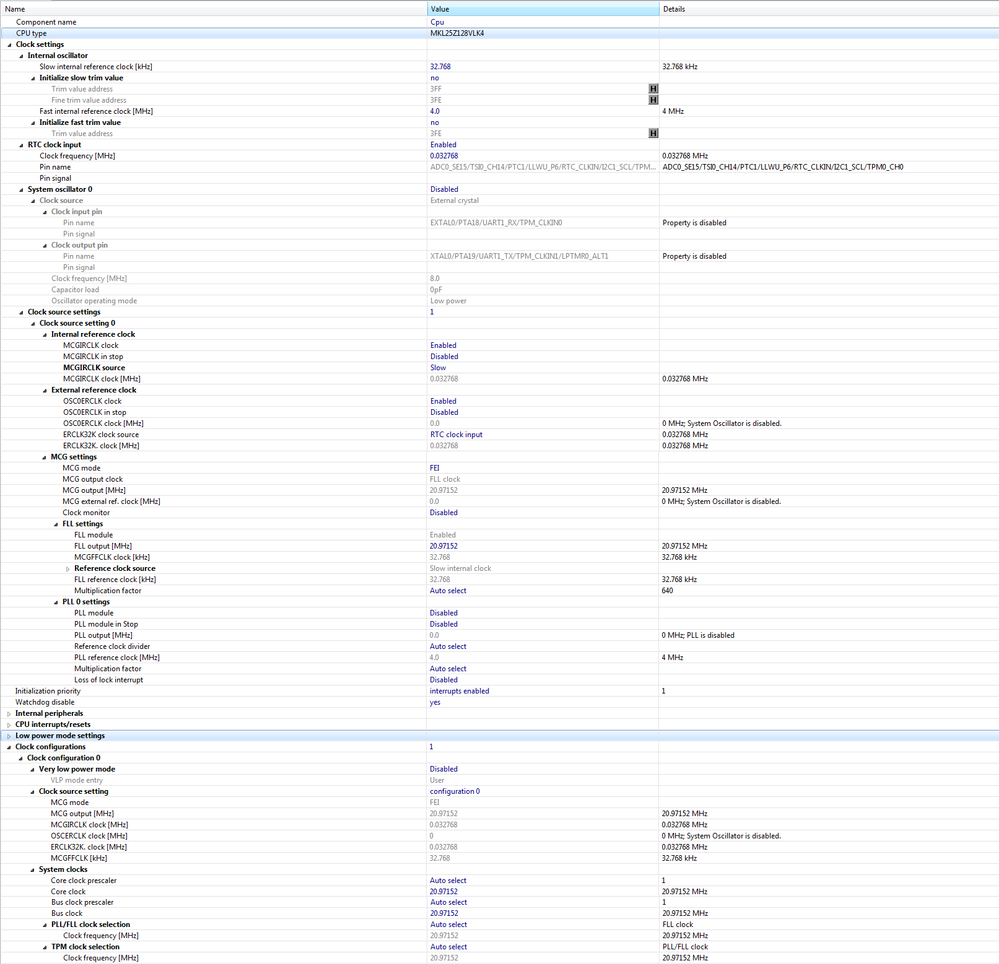

I fear you cant and I cant Event find the Settings you wrote - but it sounds interesting! Can you tell me where I find it? Here are my CPU Settings.

Thanks! Dominic

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

It is probably a hardware issue. My RTC-Clock signal is not very nice (but event not very bad!). Having a nice clock generated by a Clock-Generator I dont measure the current penalty anymore. So my problem is basically solved but if anyone knows why the bad clock signal results in an increased current consumptin I am very interested in!

Thank you all! Dominic

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I take it from this you have an external 32KHz clock source, NOT the internal oscillator. In that case, you must insure that the digital input signal spends 'limited' time at any significant voltage 'away from the rails', as like any CMOS input middling voltages incur significant shoot-thru current in the input buffer. I wouldn't be surprised to see something on the order of 100uA at dead-center (Vbat/2).

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

My Clock Signal is dirty because PTC1 is internally connected to the OpenSDA INTERFACE ( SDA_PTD6 ) on the KL25Z Board Rev. E. Removing resistor R24 ( 0 Ohm ) solves the issue. Does anyone know why it is connected to OpenSDA and if it is a Problem to remove R24?

Thanx! Dominic