- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Pad Control register (IOMUXC_SW_PAD_CTL_PAD_EIM_BCLK) Problem

Pad Control register (IOMUXC_SW_PAD_CTL_PAD_EIM_BCLK) Problem

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I got a running System over EIM Bus Interface for the i.mx6dl in synchronous mode. I got a problem regarding to

i.MX 6Solo/6DualLite Applications Processor Reference Manual, Rev. 0, 11/2012

37.3.318 Pad Control Register (IOMUXC_SW_PAD_CTL_PAD_EIM_BCLK).

If i am changing the DSE register (Drive strength field) to a value bigger than 60_OHM,

i can see that the i.MX6dl captures the Input Data one cycle too early!!!!

It seems that only the DSE setting on the eim_bclk port is responsible for the early data sample,

if i change the DSE values for other eim specific ports, i can't notice any problems for the bus communication!

I took a look at the oscilloscope and i haven't seen any timing specific differences of the peripherals for the eim signals between and different xx_ohm values =>

the problem must be generated from the i.MX6dl!

According to 22.8.3 Chip Select n Read Configuration Register 1 (EIM_CSnRCR1),

i need to set the RWSC register +1 that i will get correct read data if i set the eim_bclk port to a value > 60_ohm!

Does someone has an explaination for this behaviour?

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

One more remark:

for correct operaton with continuous BCLK mode next steps should be performed,

described in sect.22.5.1 Continuous BCLK IMX6SDLRM :

To let EIM work properly under continuous BCLK MODE, the initialization must follow

below procedure. The initialize procedure should be done before any access to EIM. If it

is not possible to do so, e.g. device booted up from EIM, the initialize flow should be

done after performming a reset of EIM.

The recommended initialize flow is as follow

1. Disable EIM clock by clearing bit 4 of EIM_WIAR Register.

2. Select Continuous BCLK by setting bit 3 of EIM_WCR Register.

3. Enable DLL by setting bit 0 of EIM_DCR Register.

4. Enable EIM clock by setting bit 4 of EIM_WIAR Register.

5. Reset DLL by toggling bit 1 of EIM_DCR Register(1->0->1).

6. Wait for DLL lock (Both bit 0 and bit 1 of EIM_DSR Register are asserted).

After initialization, EIM can be programed to various access timing, but BCD MUST be kept to 0.

DLL Upadte Interval and inital value can be set by write EIM_DCR Register in

corresponding bit field.

Also DLL provides manual adjustment to delay. An extra offset can be added to internal

delay line, which can be used when DLL have some kind of predicable error.

One very important update for EIM max.clock in synchronous mode

given in latest rev.4 i.MX6SDL Datasheet (rev.4, 12/2014), p.52

sect.4.9.3 "External Interface Module (EIM)":

"ACLK_EXSC is also used when the EIM is in synchronous mode.

The maximum frequency for ACLK_EXSC is 104 MHz."

Internally ACLK_EXSC is connected to aclk_eim_slow_clk_root

according to Table 22-4.

That means that in CCM one needs to set clock for EIM module also

(ACLK_EIM_SLOW_CLK_ROOT) <= 104MHz

description is given in Figure 18-2 "Clock Tree - Part 1" , Table 22-4 "EIM Clocks"

i.MX6SDL Reference Manual (rev.1 5/2013)

aclk_eim_slow_clk_root = aclk_exsc

http://cache.freescale.com/files/32bit/doc/ref_manual/IMX6SDLRM.pdf

http://cache.freescale.com/files/32bit/doc/data_sheet/IMX6SDLCEC.pdf

~igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi David

what is BCLK frequency and if this happens when frequency is decreased ?

Best regards

igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Igor

The BCD Setting is "00" => The BCLK frequency is about 100MHz

At the moment i am not able to change the BCD setting, but i think i will not have any affect to my problem, due to the usage of the fastest clock!

greets david

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi David

at some bclk frequency combination bclk trace layout & DSE

may produce ringing, casing appearance additional bclk clock.

Best regards

igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Igor

My first setting for eim_bclk was for 40_Ohm, there i recognized a high signal ringing on HW, to reduce this signal ringings i set the register to 80_ohm!

Update:

I am using contiuous burst mode so the BCD value has to be "00",

To reduce the clock frequency i changed the

Page 833/18.6.8 CCM Serial Clock Multiplexer Register 1 (CCM_CSCMR1)

aclk_eim_slow_podf register from "001" to "011", the eim_bclk port has now a frequenzy of ~50MHz!

I checked the different Drive strength field values for eim_bclk from 34_ohm to 240_ohm, and every setting worked for read accesses!

How is this possible?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

probably there is ringing on clock signal or ripple on power lines

with some DS settings. You can for example add small capacitor

on it and check changes. 40_Ohm gives fast rise times (steep slopes),

80_ohm gives more flat edges, flat edges may give instabilty for

register triggers working on edges - usually they require fast edges.

~igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

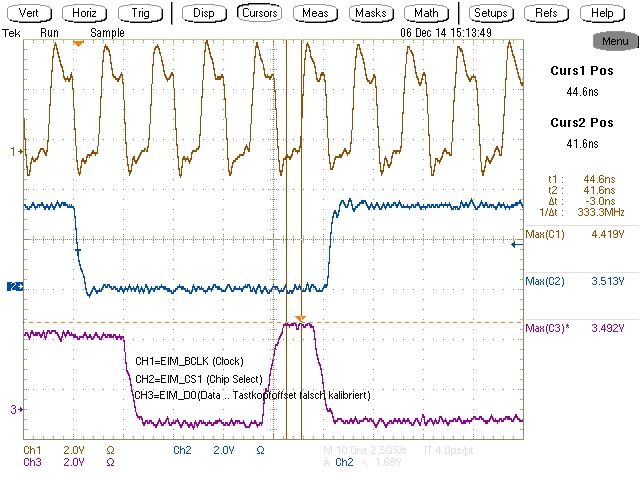

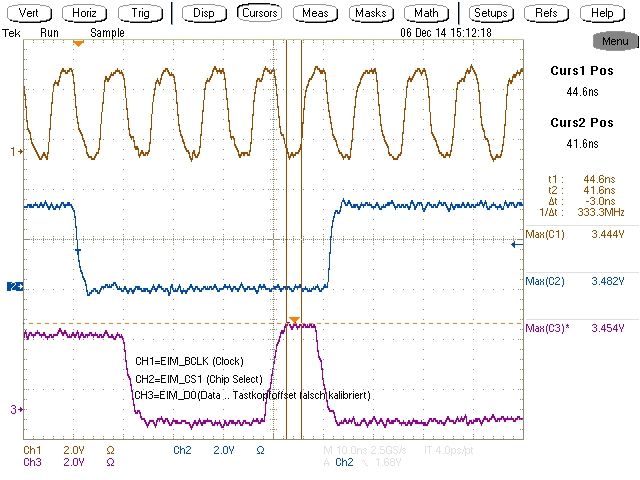

Picture 1: Synchron Read Access, eim_bclk = 40_ohm

Picture 2: Synchron Read Access, eim_bclk = 80_ohm

With the configuration for Picture 1 the synchronous read access worked with rwsc = 4.

With the configuration for Picture 2 the synchronous read access won't work with rwsc = 4 (setting shown in picture),

but it will work with rwsc = 5,

if the setting rwsc = 5 is used the eim_cs1 signal will be deasserted 1 eim_bclk cycle later,

the eim_d0 signal is similar to rwsc = 4

As you can see there are no relevant timing differences of the eim_data for 40_ohm and 80_ohm setting (1 point int timing scale = 2ns).

If i change the eim_bclk drive strength setting, only the eim_bclk port will change, i dont think that it will affect the intern i.MX6dl clk, so if the periphery signals are similar as you can see in the 2 pictures, how is it possible that i need a rwsc +1 setting?????

Just for Information: I use a PLL in the FPGA for synchronous accesses and i made a configuration where i triggered the eim_data output-ffs -90° before the rising edge of eim_bclk => The eim_data where set ~2,5 ns faster than you see in the pictures and i got the same problem that i need to set rwsc register +1 for eim_bclk > 60_ohm!!

=> This is the proof that the FPGA does nothing wrong and theproblem must be created in the i.MX6dl !

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

One more remark:

for correct operaton with continuous BCLK mode next steps should be performed,

described in sect.22.5.1 Continuous BCLK IMX6SDLRM :

To let EIM work properly under continuous BCLK MODE, the initialization must follow

below procedure. The initialize procedure should be done before any access to EIM. If it

is not possible to do so, e.g. device booted up from EIM, the initialize flow should be

done after performming a reset of EIM.

The recommended initialize flow is as follow

1. Disable EIM clock by clearing bit 4 of EIM_WIAR Register.

2. Select Continuous BCLK by setting bit 3 of EIM_WCR Register.

3. Enable DLL by setting bit 0 of EIM_DCR Register.

4. Enable EIM clock by setting bit 4 of EIM_WIAR Register.

5. Reset DLL by toggling bit 1 of EIM_DCR Register(1->0->1).

6. Wait for DLL lock (Both bit 0 and bit 1 of EIM_DSR Register are asserted).

After initialization, EIM can be programed to various access timing, but BCD MUST be kept to 0.

DLL Upadte Interval and inital value can be set by write EIM_DCR Register in

corresponding bit field.

Also DLL provides manual adjustment to delay. An extra offset can be added to internal

delay line, which can be used when DLL have some kind of predicable error.

One very important update for EIM max.clock in synchronous mode

given in latest rev.4 i.MX6SDL Datasheet (rev.4, 12/2014), p.52

sect.4.9.3 "External Interface Module (EIM)":

"ACLK_EXSC is also used when the EIM is in synchronous mode.

The maximum frequency for ACLK_EXSC is 104 MHz."

Internally ACLK_EXSC is connected to aclk_eim_slow_clk_root

according to Table 22-4.

That means that in CCM one needs to set clock for EIM module also

(ACLK_EIM_SLOW_CLK_ROOT) <= 104MHz

description is given in Figure 18-2 "Clock Tree - Part 1" , Table 22-4 "EIM Clocks"

i.MX6SDL Reference Manual (rev.1 5/2013)

aclk_eim_slow_clk_root = aclk_exsc

http://cache.freescale.com/files/32bit/doc/ref_manual/IMX6SDLRM.pdf

http://cache.freescale.com/files/32bit/doc/data_sheet/IMX6SDLCEC.pdf

~igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am looking at similar setup as the original poster and came across this entry. Looking at the reference manual for the Dual/Quad (Document Number: IMX6DQRM Rev. 3, 07/2015) and comparing it to the one for the Solo/DualLite (Document Number: IMX6SDLRM Rev. 2, 04/2015). The Dual/Quad manual does not have the 22.5.1 section about continuous BCLK in it or the register documentation for the EIM_DCR and EIM_DSR bits, despite have a later publish date. Is there truly a difference between parts or is there an omission in the docs?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Igor,

i can't imagine how but it seems that a wrong initialize of continuous bclk was responsible for the early data latch at eim_bclk drive strength setting >60_ohm.

If i do the initialize as it is shown in chapter 22.5.1, it works with the calculated amount of wsc!

Thanks for help Igor!

Best Regards,

David Niebauer

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I think that first picture should not be considered at all since it has processor

data levels at 4.4V :smileyalert: while datasheets allows only 3.6V Table 8. Operating Ranges

http://cache.freescale.com/files/32bit/doc/data_sheet/IMX6DQCEC.pdf?fasp=1&WT_TYPE=Data%20Sheets&WT_...IMX6SDLCEC

So definitely processor operates wrongly at such levels and probably

wrongly outputs incorrect number of bclk signals.