- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- Problem when booting MKE4Z08.

Problem when booting MKE4Z08.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello.

I am working in project where a Kinetis MKE04Z8VFK4 is used. The problem I have is that the CPU:s external oscillator does not start when the Power to the CPU is cycled OFF and ON again. When the code is downloaded and started the CPU is executing the code correctly. But when the Power is cycled I can see that the external oscillator does not oscillate and no code is executed. I have assembled a number of MKE04Z8VFK4 on other circuit boards and there it works perfectly. It seems that the LVD or POR reset is the problem here, the ICS is not initiated correctly after POR. When I reset the CPU by activating the reset pin the CPU starts up correctly. I use an Segger J-link Pro to download the code to the CPU. The CPU is running in FEE clock mode. I have tried to run the CPU in FEI clock mode with the same result, no code is executed.

Please help me in this matter because I am running out of ideas how to go on.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Bo

I thought that I copied the FOPT table from the KE04 user's manual but I must have taken it from the KL04 by mistake (sorry). There don't look to be options here for the KE04, therefore I think that you have only two options:

1. Ensure that the NMI line is always pulled to '1' at reset.

or

2. Add an NMI interrupt handler (in flash based vector table) which will immediately be called, which then disables the NMI function and returns so that the booting can continue normally.

Regards

Mark

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Bo

When you enable the oscillator you can select its gain (either high or low). If the gain setting doesn't match the circuit the oscillator will not always start.

Try both low and high gain settings to see whether there is a mismatch that leads to unreliable starting.

Regards

Mark

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Bo

Also disable the NMI pin function in the FOTP flash setting to avoid problems of starting in case the NMI line is not at '1'.

Regards

Mark

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Mark.

I am not sure I understand your answer. Are there more than one way to disable NMI?

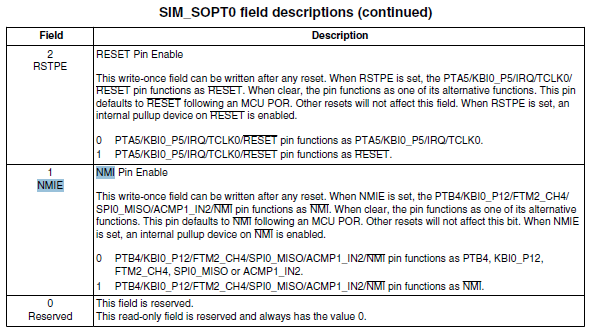

NMIE in System Options Register (SIM_SOPT) is already set to 0 in code but it seems to have no effect when CPU starts up.

I have tried to move setting NMIE in SIM_SOPT from MAIN() to start() (earlier in code), but this change has no effect.

It seems that NMIE does not work correctly?

'

Regards

/Bo

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Bo

You must disable it in the "flash configuration" block so that it is valid out-of-reset. Code will not be able to stop a pending interrupt because the interrupt will be taken before the code has a chance to run.

The Flash configuration block is the area 0x400..0x40f in Flash which can be filled with protection, security and options that are vaid when the chip starts out of reset.

Regards

Mark

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Mark.

I still don't understand how to do this in MKE04Z8.

In reference manual for MKE04Z8 you can read this about the FTMRE_FOPT field descriptions

Field Description

NV Nonvolatile Bits

The NV[7:0] bits are available as nonvolatile bits. During the reset sequence, the FOPT register is loaded

from the flash nonvolatile byte in the flash configuration field at global address 0x40F located in flash memory.

This differs from the MKL04Z8 CPU for which the following can be read:

Table 6-2. Flash Option Register (FTFA_FOPT) Bit Definitions(continued)

BitNum Field Value Definition

5 FAST_INIT Select initialization speed on POR, VLLSx, and any system reset .

0 Slower initialization. The Flash initialization will be slower with the benefit of reduced average current during this time. The duration of the recovery will be controlled by the clock divider selection determined by the LPBOOT setting.

1 Fast Initialization.The Flash has faster recoveries at the expense of higher current during these times.

3 RESET_PIN_CFG Enable/disable control for the RESET pin.

0 RESET pin is disabled following a POR and cannot be enabled as RESET function. When this option is selected, there could be a short period of contention during a POR ramp where the device drives the pin out low prior to establishing the setting of this option and releasing the RESET function on the pin. This bit is preserved through system resets and low power modes. When RESET pin function is disabled it cannot be used as a source for low power mode wakeup. NOTE: When the reset pin has been disabled and security has been enabled by

means of the FSEC register, a mass erase can be performed only by setting both the mass erase and system reset request bits in the

MDM-AP register.

1 RESET pin is dedicated. The port is configured with pullup enabled, open drain, passive filter enabled.

2 NMI_DIS Enable/disable control for the NMI function.

0 NMI interrupts are always blocked. The associated pin continues to default to NMI pin controls with internal pullup enabled. When NMI pin function is disabled it cannot be used as a source for low power mode wakeup.

1 NMI pin/interrupts reset default to enabled.

1 Reserved Reserved for future expansion.

4,0 LPBOOT Control the reset value of OUTDIV1 value in SIM_CLKDIV1 register. Larger divide value selections produce lower average power consumption during POR, VLLSx recoveries and reset sequencing and after reset exit. The recovery times are also extended if the FAST_INIT option is not selected.

00 Core and system clock divider (OUTDIV1) is 0x7 (divide by 8)

01 Core and system clock divider (OUTDIV1) is 0x3 (divide by 4)

10 Core and system clock divider (OUTDIV1) is 0x1 (divide by 2)

11 Core and system clock divider (OUTDIV1) is 0x0 (divide by 1)

Is the bit definitions for FTMRE_FOPT (MKE04Z8) the same as for FTFA_FOPT (MKL04Z8) ?

If this is the case, why has it been left out in the MKE04Z8 reference manual?

Regards

/Bo

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Bo

I thought that I copied the FOPT table from the KE04 user's manual but I must have taken it from the KL04 by mistake (sorry). There don't look to be options here for the KE04, therefore I think that you have only two options:

1. Ensure that the NMI line is always pulled to '1' at reset.

or

2. Add an NMI interrupt handler (in flash based vector table) which will immediately be called, which then disables the NMI function and returns so that the booting can continue normally.

Regards

Mark

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Mark.

I have added a NMI interrupt handler where I added following code:

void NMI_Isr(void)

{

uint32_t u32Soptbl;

u32Soptbl = SIM->SOPT;

u32Soptbl = u32Soptbl & 0xFFFFFFF8; //disable NMi and reset.Bit 0 is reserved.

SIM->SOPT = u32Soptbl;

}

And it works perfect. Now the CPU starts correctly and does not hang.

Thank you for the tip.

Regards

/Bo

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Bo,

I have the same problem to boot the MCU after PowerOnReset..

The MCU must catch the nmi state after PowerOnReset..

As following your code, it's fine.. Thank you..

Regards,

Nick.