- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- Digital Signal Controllers

- :

- MC56F84789 missing PWMB registers definitions in MC56F84789_rev1.0.h

MC56F84789 missing PWMB registers definitions in MC56F84789_rev1.0.h

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The Reference Manual for the MC56F847xx family states that PWMB has the registers: PWMB_SMnFRACVALx and the PWMB_SMnFRCTRL (pages 744-751).

They were included in the last revision as stated on page 1097 (A.28 PWMB changes).

The processor header file (...\CW MCU v10.6\MCU\lib\wizard_data\DSC\DataBase\derivatives\include\MC56F84789_rev1.0.h), however, do not include them, and it has to be done by hand.

Does the processor really have the fractional registers for PWMB?

page 1097 (A.28 PWMB changes) also states that:

"In Introduction section, reworded to clearly indicate that PWMB supports digital dithering, while PWMA does not

support digital dithering."

However, in page 743, the introduction says the opposite:

The primary difference between PWMB and PWMA: PWMA supports NanoEdge placement (digital dithering); PWMB does not support NanoEdge placement (digital dithering).

I suppose that page 743 is correct, as the rest of the document support its version. Am I correct?

Thanks for the attention.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Martin,

I now clearly see the issue in the latest edition of the document. First, please review this section:

28.4.2.9.2 Fractional Delay Logic without Micro-Edge Placement Block

For submodules that are not supported by the micro-edge placer, the PWM can use

dithering to simulate fine edge control. Enable this feature by setting the

FRCTRL[FRACx_EN] bits. It is unnecessary to set FRCTRL[FRAC_PU]. The PWM

period or the PWM edges will dither from the nearest whole number values to achieve an

average value that is equivalent to the programmed fractional value. For example, if you

want the PWM period to be 50.2 clock cycles, then program VAL1 with 0x0032 and

FRACVAL1 with 0x3000. The PWM period will be 50 cycles long most of the time, but

will occasionaly be 51 cycles long to achieve a long-term average of 50.2 cycles.

In submodules that are not supported by a micro-edge placer, the clock frequency is not

required to be any specific value to achieve proper operation.

It is clear that "digital dithering" is only needed when nano-edge placement is not available.

Digital dithering is available only for PWMB.

PWMA has nano-edge placement.

The issue is introduced in a recent version of the documentation that EQUATES "nano-edge placement" with "digital dithering".

They are in fact mutually exclusive.

The document shall be revised to strike the pharses "digital dithering" where they wrongly appear as in the below:

"The primary difference between PWMB and PWMA: PWMA supports NanoEdge

placement (digital dithering); PWMB does not support NanoEdge placement (digital

dithering)."

Such that it will instead read something like:

The primary difference between PWMB and PWMA: PWMA supports NanoEdge

placement (but does not digital dithering); PWMB does not support NanoEdge placement (but does support digital

dithering).

Thank you for pointing this out. We will also correct the header files as required if after review we find that the registers needed for digital dithering are missing in the IDE.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Martin,

I now clearly see the issue in the latest edition of the document. First, please review this section:

28.4.2.9.2 Fractional Delay Logic without Micro-Edge Placement Block

For submodules that are not supported by the micro-edge placer, the PWM can use

dithering to simulate fine edge control. Enable this feature by setting the

FRCTRL[FRACx_EN] bits. It is unnecessary to set FRCTRL[FRAC_PU]. The PWM

period or the PWM edges will dither from the nearest whole number values to achieve an

average value that is equivalent to the programmed fractional value. For example, if you

want the PWM period to be 50.2 clock cycles, then program VAL1 with 0x0032 and

FRACVAL1 with 0x3000. The PWM period will be 50 cycles long most of the time, but

will occasionaly be 51 cycles long to achieve a long-term average of 50.2 cycles.

In submodules that are not supported by a micro-edge placer, the clock frequency is not

required to be any specific value to achieve proper operation.

It is clear that "digital dithering" is only needed when nano-edge placement is not available.

Digital dithering is available only for PWMB.

PWMA has nano-edge placement.

The issue is introduced in a recent version of the documentation that EQUATES "nano-edge placement" with "digital dithering".

They are in fact mutually exclusive.

The document shall be revised to strike the pharses "digital dithering" where they wrongly appear as in the below:

"The primary difference between PWMB and PWMA: PWMA supports NanoEdge

placement (digital dithering); PWMB does not support NanoEdge placement (digital

dithering)."

Such that it will instead read something like:

The primary difference between PWMB and PWMA: PWMA supports NanoEdge

placement (but does not digital dithering); PWMB does not support NanoEdge placement (but does support digital

dithering).

Thank you for pointing this out. We will also correct the header files as required if after review we find that the registers needed for digital dithering are missing in the IDE.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you John.

Now I am shure we understood each other.

I wish you a happy "mutually exclusive" new year.

Martin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks Martin,

Please let us know if we can help out on your project any further.

Best Regards,

John L. Winters

Senior Applications Engineer

AMR/EU MCU & MPU AE Group

Freescale Inc.

2100 Elliot Road

This email and any associated attachments have been classified as:

Freescale Confidential and Proprietary

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

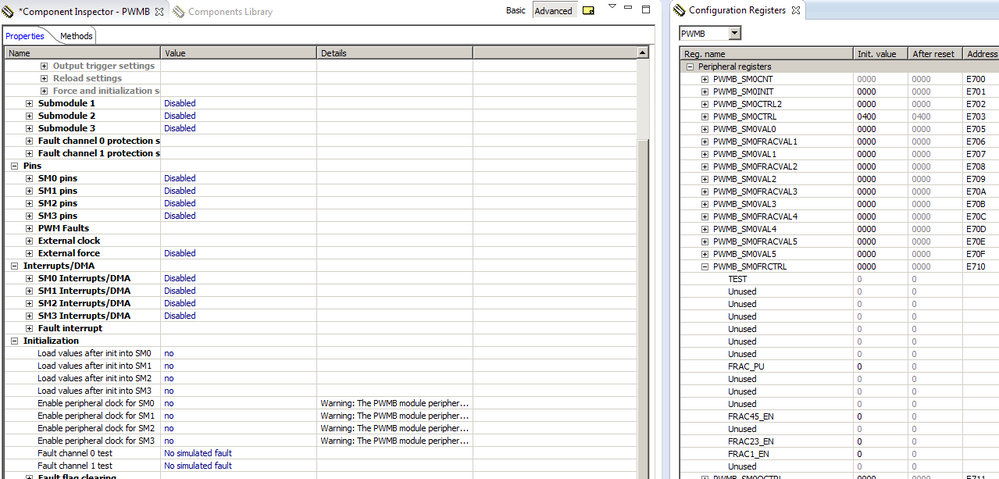

After review, the latest CW, 10.6 with updates shows the required registers within Processor Expert GUI to control the "digital dithering" for PWMB:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Maybe the PWMB and PWMA both suppport the NanoEdge placement now according to the newest Reference Manual . I notice they add the PWMB Fractional Registers that the early Reference Manual doesn't have. And the cw10.6 has these Registers too , though they aren't including in the MC5684789.h. Anyway you can test whether it really has it.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

"The primary difference between PWMB and PWMA is that PWMA supports NanoEdge placement. PWMB does not support this feature." - the reference manual for MC56F84789.

Digital dithering can be performed in software to provide more resolution for PWMB. It involves alternating between two counts to give the approximate effect of an "in between count".

However, PWMA is capable of actual NanoEdge placement without resorting to this method.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

John,

I saw in the reference manual what you wrote.

However, page 1097 (A.28 PWMB changes) also states that:

"In Introduction section, reworded to clearly indicate that PWMB supports digital dithering, while PWMA does not

support digital dithering."

It seems that the reference manual is contradictory. Also, all the registers for PWMB_SMnFRACVALx are there and are there is nothing else stating that those registers are not functional.

Whom may I write to so that it can be reviewed?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

Dithering means to alternate between two values. If you have nano edge you do not need dithering. Also the existence of registers does not imply their support if higher level documentation negates them.

Best Regards,

John L. Winters

Senior Applications Engineer

AMR/EU MCU & MPU AE Group

Freescale Inc.

2100 Elliot Road

This email and any associated attachments have been classified as:

Freescale Confidential and Proprietary

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear John,

I understand what you say. The problem is that the higher level

documentation is saying the opposite in two/three different parts of the

reference manual. That's why I went to look the at the registers. Also,

PWMA and PWMB are two entirely different chapters in the reference

manual, by witch I would assume that their documentation describes their

functionalities correctly, since they are not condensed in one chapter.

I thank you for your attention, and I am very sorry that freescale don't

want to know about "documentation bugs".

Martin