- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- PowerQUICC Processors

- :

- MPC8569E increase flash memory, Uboot not working.

MPC8569E increase flash memory, Uboot not working.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

MPC8569E increase flash memory, Uboot not working.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have with me an MPC8569E based board. It is using 2 chips for flash memory, both of 128Mb, effectively the size of flash being 256Mb.

So the current Memory map of flash is :

0xF000_0000 to 0xFFFF_FFFF,

consisting of 2 banks (0xF000_0000 to 0xF7FF_FFFF and 0xF800_0000 to 0xFFFF_FFFF)

The corresponding entries in Uboot files are:

file: include/configs/MPC8569MDS.h

| #define CONFIG_SYS_CCSRBAR | 0xE0000000 | /* relocated CCSRBAR */ |

#define CONFIG_SYS_FLASH_BASE 0xF0000000

#define CONFIG_SYS_FLASH_BASE2 0xF8000000 /* Second flash bank of 128MB */

#define CONFIG_SYS_FLASH_BASE_PHYS CONFIG_SYS_FLASH_BASE

#define CONFIG_SYS_FLASH_BANKS_LIST {CONFIG_SYS_FLASH_BASE, CONFIG_SYS_FLASH_BASE2}

/*Chip select 0 - Flash 2*/

#define CONFIG_FLASH_BR_PRELIM 0xF8001011

#define CONFIG_FLASH_OR_PRELIM 0xF8006FF3

/*Chip select 1 - Flash 1*/

#define CONFIG_FLASH_BR1_PRELIM 0xF0001011

#define CONFIG_FLASH_OR1_PRELIM 0xF0006FF3

file: board/freescale/mpc8569mds/law.c

SET_LAW(CONFIG_SYS_FLASH_BASE, LAW_SIZE_512M, LAW_TRGT_IF_LBC),

file: board/freescale/mpc8569mds/tlb.c

SET_TLB_ENTRY(1, CONFIG_SYS_FLASH_BASE, CONFIG_SYS_FLASH_BASE,

MAS3_SX|MAS3_SW|MAS3_SR, MAS2_I|MAS2_G,

0, 0, BOOKE_PAGESZ_256M, 1),

Our requirement is to increase the flash Memory from 256Mb to 512Mb.

So now instead of 2x128Mb chips I am going to use 2x256Mb chips

The new memory map is thus:

0xE000_0000 to 0xFFFF_FFFF,

consisting of 2 banks (0xE000_0000 to 0xEFFF_FFFF and 0xF000_0000 to 0xFFFF_FFFF)

The corresponding modifications i made in Uboot files are:

file: include/configs/MPC8569MDS.h

| #define CONFIG_SYS_CCSRBAR | 0xD0000000 | /* relocated CCSRBAR again */ |

#define CONFIG_SYS_FLASH_BASE 0xE0000000

#define CONFIG_SYS_FLASH_BASE2 0xF0000000 /* Second flash bank of 128MB */

*Chip select 0 - Flash 2*/

#define CONFIG_FLASH_BR_PRELIM 0xF0001011

#define CONFIG_FLASH_OR_PRELIM 0xF0006FF3

/*Chip select 1 - Flash 1*/

#define CONFIG_FLASH_BR1_PRELIM 0xE0001011

#define CONFIG_FLASH_OR1_PRELIM 0xF0006FF3

I don't find any need to change tlb.c or law.c keeping in view the entries used previously.

Now when I boot the board I get the following:

U-Boot 2009.11 (Oct 26 2014 - 12:58:32)

CPU: 8569E, Version: 2.1, (0x80880021)

Core: E500, Version: 5.1, (0x80211051)

Clock Configuration:

CPU0:1066.667 MHz,

CCB:533.333 MHz,

DDR:400 MHz (800 MT/s data rate) (Asynchronous), LBC:66.667 MHz

QE:533.333 MHz

L1: D-cache 32 kB enabled

I-cache 32 kB enabled

Board: 8569 SCM MCP

I2C: ready

DRAM: Initializing

0 kB left unmapped

DDR: 2 GB (DDR3, 64-bit, CL=6, ECC off)

FLASH: Bad trap at PC: 7ff49458, SR: 21200, vector=d00

NIP: 7FF49458 XER: 20000000 LR: 7FF4941C REGS: 7febfd48 TRAP: 0d00 DAR: E0000000

MSR: 00021200 EE: 0 PR: 0 FP: 0 ME: 1 IR/DR: 00

GPR00: 000000F0 7FEBFE38 7FEBFF58 7FFC4230 000000F0 7FEBFE3F 000000F0 00000000

GPR08: 7FEBFE2C 000000F0 00000000 E0000000 00000006 2692A314 7FF88C00 7FFC0000

GPR16: 8A000422 8946C19B 1704812A 88700586 00001000 7FEBFD38 00000000 7FF4109C

GPR24: 7FEBFEF0 E0000000 7FF7517C E0000000 00000000 7FFC4230 7FF89104 E0000000

Call backtrace:

7FF4941C 7FF498E8 7FF4A6CC 7FF4ADC4 7FF42A14 7FF41630

Exception in kernel pc 7ff49458 signal 0

What am I missing here?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The error you're seeing is a TLB miss. Double check your TLB setup to make sure that all of flash is covered. You said you left tlb.c alone, which would explain faulting in the upper half of flash, but your dump shows a fault in the lower half of flash. Could you post your entire tlb.c file and board config header, and if possible a dump of the TLB after the crash?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Scott

Another of my peer had suggested me the same thing. But I wonder "How did you come to this conclusion".

I messed up with the old files a little and I don't know exactly what configuration of tlb.c was there when the first time error I posted above was produced.

I am re-doing it all. So If I do the settings of tlb.c as posted in the original post of mine (leaving it alone) and MPC8569MDS.h and law.c as in the original post, the Uboot won't even show up.

The error dump I showed above comes when the tlb.c has:

SET_TLB_ENTRY(1/*_tlb*/, CONFIG_SYS_FLASH_BASE/*epn*/, CONFIG_SYS_FLASH_BASE/*rpn*/,

MAS3_SX|MAS3_SW|MAS3_SR/*perms*/, MAS2_I|MAS2_G/*wimge*/,

0/*ts*/, 0/*esel*/, BOOKE_PAGESZ_256M/*_sz*/, 1/*iprot*/),

SET_TLB_ENTRY(1/*_tlb*/, CONFIG_SYS_FLASH_BASE2/*epn*/, CONFIG_SYS_FLASH_BASE2/*rpn*/,

MAS3_SX|MAS3_SW|MAS3_SR/*perms*/, MAS2_I|MAS2_G/*wimge*/,

0/*ts*/, 0/*esel*/, BOOKE_PAGESZ_256M/*_sz*/, 1/*iprot*/),

and rest 2 files are as in the original post.

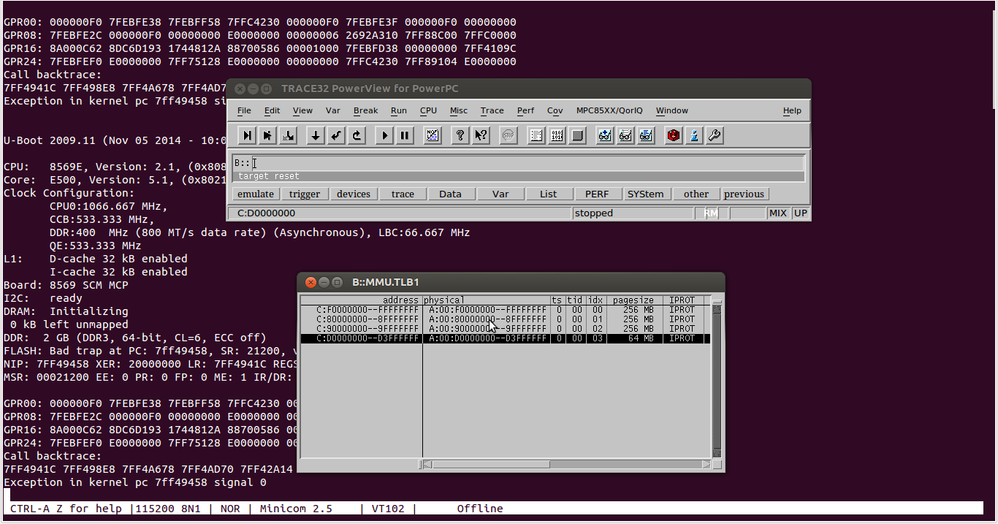

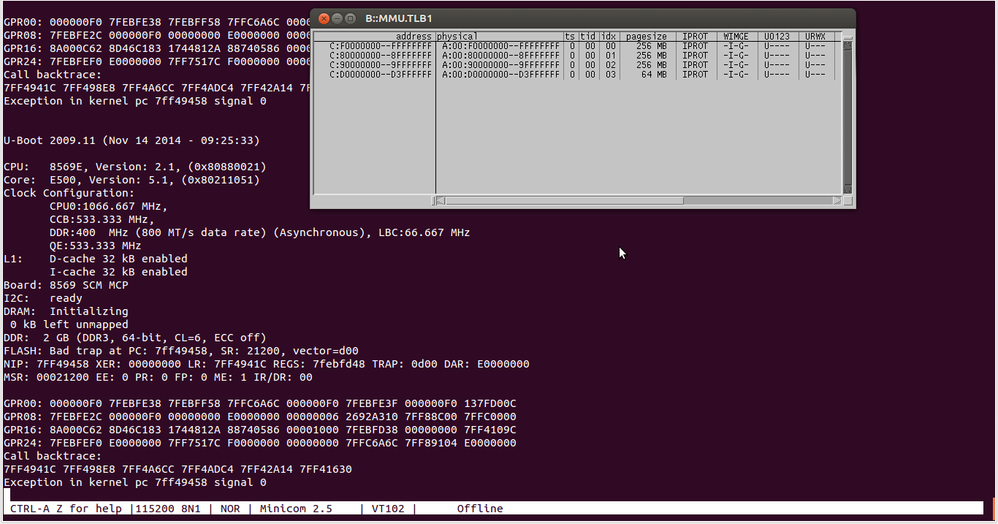

The Following image shows the dump of tlb after crash !!

Can you help me understand what is the role of this tlb entry in tlb.c. Additionally I didn't quite understand the 'epn' and 'rpn' argumnets from description in "E500_core_rm.pdf". Can you explain that a bit.

Thanks in advance.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I knew that it was a TLB miss because of "vector=d00", which corresponds to "STD_EXCEPTION(0x0d00, DataTLBError, UnknownException)" in arch/powerpc/cpu/mpc85xx/start.S.

Your problem is that you're using the same ESEL (entry select) for both entries, so the second entry will overwrite the first, and you will have no mapping for the first half of flash. You need to pick an unused ESEL for the second entry.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Scott,

Great Information @Scott. I think I tried a different esel too. I have rechecked by using esel as 1 in the second TLB entry , the one for the higher flash.

This is what I have used:

SET_TLB_ENTRY(1/*_tlb*/, CONFIG_SYS_FLASH_BASE/*epn*/, CONFIG_SYS_FLASH_BASE/*rpn*/,

MAS3_SX|MAS3_SW|MAS3_SR/*perms*/, MAS2_I|MAS2_G/*wimge*/,

0/*ts*/, 0/*esel*/, BOOKE_PAGESZ_256M/*_sz*/, 1/*iprot*/),

SET_TLB_ENTRY(1/*_tlb*/, CONFIG_SYS_FLASH_BASE2/*epn*/, CONFIG_SYS_FLASH_BASE2/*rpn*/,

MAS3_SX|MAS3_SW|MAS3_SR/*perms*/, MAS2_I|MAS2_G/*wimge*/,

0/*ts*/, 1/*esel*/, BOOKE_PAGESZ_256M/*_sz*/, 1/*iprot*/),

The error remained totally the same.

Below is the dump of my whole tlb.c file:

#include <common.h>

#include <asm/mmu.h>

struct fsl_e_tlb_entry tlb_table[] = {

/* TLB 0 - for temp stack in cache */

SET_TLB_ENTRY(0, CONFIG_SYS_INIT_RAM_ADDR, CONFIG_SYS_INIT_RAM_ADDR,

MAS3_SX|MAS3_SW|MAS3_SR, 0,

0, 0, BOOKE_PAGESZ_4K, 0),

SET_TLB_ENTRY(0, CONFIG_SYS_INIT_RAM_ADDR + 4 * 1024,

CONFIG_SYS_INIT_RAM_ADDR + 4 * 1024,

MAS3_SX|MAS3_SW|MAS3_SR, 0,

0, 0, BOOKE_PAGESZ_4K, 0),

SET_TLB_ENTRY(0, CONFIG_SYS_INIT_RAM_ADDR + 8 * 1024,

CONFIG_SYS_INIT_RAM_ADDR + 8 * 1024,

MAS3_SX|MAS3_SW|MAS3_SR, 0,

0, 0, BOOKE_PAGESZ_4K, 0),

SET_TLB_ENTRY(0, CONFIG_SYS_INIT_RAM_ADDR + 12 * 1024,

CONFIG_SYS_INIT_RAM_ADDR + 12 * 1024,

MAS3_SX|MAS3_SW|MAS3_SR, 0,

0, 0, BOOKE_PAGESZ_4K, 0),

/* TLB 1 Initializations */

/*

* TLBe 0: 64M Non-cacheable, guarded

* Out of reset this entry is only 4K.

* 0xfc000000 256K NAND FLASH (CS3)

* 0xfe000000 32M NOR FLASH (CS0)

*/

//SET_TLB_ENTRY(1, CONFIG_SYS_NAND_BASE, CONFIG_SYS_NAND_BASE,

// MAS3_SX|MAS3_SW|MAS3_SR, MAS2_I|MAS2_G,

// 0, 0, BOOKE_PAGESZ_64M, 1),

/*

#define SET_TLB_ENTRY(_tlb, _epn, _rpn, _perms, _wimge, _ts, _esel, _sz, _iprot) \

{ .mas0 = FSL_BOOKE_MAS0(_tlb, _esel, 0), \

.mas1 = FSL_BOOKE_MAS1(1, _iprot, 0, _ts, _sz), \

.mas2 = FSL_BOOKE_MAS2(_epn, _wimge), \

.mas3 = FSL_BOOKE_MAS3(_rpn, 0, _perms), \

.mas7 = FSL_BOOKE_MAS7(_rpn), }

*/

SET_TLB_ENTRY(1/*_tlb*/, CONFIG_SYS_FLASH_BASE/*epn*/, CONFIG_SYS_FLASH_BASE/*rpn*/,

MAS3_SX|MAS3_SW|MAS3_SR/*perms*/, MAS2_I|MAS2_G/*wimge*/,

0/*ts*/, 0/*esel*/, BOOKE_PAGESZ_256M/*_sz*/, 1/*iprot*/),

SET_TLB_ENTRY(1/*_tlb*/, CONFIG_SYS_FLASH_BASE2/*epn*/, CONFIG_SYS_FLASH_BASE2/*rpn*/,

MAS3_SX|MAS3_SW|MAS3_SR/*perms*/, MAS2_I|MAS2_G/*wimge*/,

0/*ts*/, 1/*esel*/, BOOKE_PAGESZ_256M/*_sz*/, 1/*iprot*/),

/*

* TLBe 1: 256KB Non-cacheable, guarded

* 0xf8000000 32K BCSR

* 0xf8008000 32K PIB (CS4)

* 0xf8010000 32K PIB (CS5)

*/

//SET_TLB_ENTRY(1, CONFIG_SYS_BCSR_BASE, CONFIG_SYS_BCSR_BASE_PHYS,

// MAS3_SX|MAS3_SW|MAS3_SR, MAS2_I|MAS2_G,

// 0, 1, BOOKE_PAGESZ_256K, 1),

/*

* TLBe 2: 256M Non-cacheable, guarded

* 0xa00000000 256M PCIe MEM (lower half)

*/

SET_TLB_ENTRY(1, CONFIG_SYS_PCIE1_MEM_VIRT, CONFIG_SYS_PCIE1_MEM_PHYS,

MAS3_SX|MAS3_SW|MAS3_SR, MAS2_I|MAS2_G,

0, 1, BOOKE_PAGESZ_256M, 1),

/*

* TLBe 3: 256M Non-cacheable, guarded

* 0xb00000000 256M PCIe MEM (higher half)

*/

SET_TLB_ENTRY(1, (CONFIG_SYS_PCIE1_MEM_VIRT + 0x10000000),

(CONFIG_SYS_PCIE1_MEM_PHYS + 0x10000000),

MAS3_SX|MAS3_SW|MAS3_SR, MAS2_I|MAS2_G,

0, 2, BOOKE_PAGESZ_256M, 1),

/*

* TLBe 4: 64M Non-cacheable, guarded

* 0xe000_0000 1M CCSRBAR

* 0xe280_0000 8M PCIe IO

*/

SET_TLB_ENTRY(1, CONFIG_SYS_CCSRBAR, CONFIG_SYS_CCSRBAR_PHYS,

MAS3_SX|MAS3_SW|MAS3_SR, MAS2_I|MAS2_G,

0, 3, BOOKE_PAGESZ_64M, 1),

/*

SET_TLB_ENTRY(1, CONFIG_SYS_PCIE1_IO_VIRT, CONFIG_SYS_PCIE1_IO_PHYS,

MAS3_SX|MAS3_SW|MAS3_SR, MAS2_I|MAS2_G,

0, 4, BOOKE_PAGESZ_256M, 1),

*/

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Is BCSR commented out because it doesn't exist on this board, or because you wanted to take the TLB entry? Are you sure the new output is exactly the same -- could you post it?

BTW, I don't think this is related to your problem, but you should not have MAS3_SX on I/O mappings, as instruction fetches ignore the guarded bit.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi scott,

Sorry for the late reply, I was not available.

The BCSR is not present on this board, it was on the eval board I got to know.

I am pretty sure the output was same.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Could you please paste it in case it's not 100% identical, and double check that you're running the modified code? Also, that tlb.c can't be the whole file because it ends without closing the array.

Could you use a debugger to dump the TLB1 contents after the crash?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Scott,

I was wondering If it can be an issue related with U-Boot version? I mean the settings seem to be correct.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Here is all we need:

the file MPC8569MDS.h

***********************************************************************************************

/*

* Copyright (C) 2009-2010 Freescale Semiconductor, Inc.

*

* See file CREDITS for list of people who contributed to this

* project.

*

* This program is free software; you can redistribute it and/or

* modify it under the terms of the GNU General Public License as

* published by the Free Software Foundation; either version 2 of

* the License, or (at your option) any later version.

*

* This program is distributed in the hope that it will be useful,

* but WITHOUT ANY WARRANTY; without even the implied warranty of

* MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the

* GNU General Public License for more details.

*

* You should have received a copy of the GNU General Public License

* along with this program; if not, write to the Free Software

* Foundation, Inc., 59 Temple Place, Suite 330, Boston,

* MA 02111-1307 USA

*/

/*

* mpc8569mds board configuration file

*/

#ifndef __CONFIG_H

#define __CONFIG_H

/* High Level Configuration Options */

#define CONFIG_BOOKE 1 /* BOOKE */

#define CONFIG_E500 1 /* BOOKE e500 family */

#define CONFIG_MPC85xx 1 /* MPC8540/60/55/41/48/68 */

#define CONFIG_MPC8569 1 /* MPC8569 specific */

#define CONFIG_MPC8569MDS 1 /* MPC8569MDS board specific */

/*

#define CONFIG_POST 1

#define CONFIG_SYS_POST_MEMORY 1

*/

#define CONFIG_FSL_ELBC 1 /* Has Enhance localbus controller */

#define CONFIG_PCI 1 /* Disable PCI/PCIE */

#define CONFIG_PCIE1 1 /* PCIE controller */

#define CONFIG_FSL_PCI_INIT 1 /* use common fsl pci init code */

#define CONFIG_FSL_PCIE_RESET 1 /* need PCIe reset errata */

#define CONFIG_SYS_PCI_64BIT 1 /* enable 64-bit PCI resources */

#define CONFIG_QE /* Enable QE */

#define CONFIG_ENV_OVERWRITE

#define CONFIG_FSL_LAW 1 /* Use common FSL init code */

#ifndef __ASSEMBLY__

extern unsigned long get_clock_freq(void);

#endif

/* Replace a call to get_clock_freq (after it is implemented)*/

#define CONFIG_SYS_CLK_FREQ 66666666

#define CONFIG_DDR_CLK_FREQ CONFIG_SYS_CLK_FREQ

/*#define CONFIG_DDR_CLK_FREQ 40000000 */

/*MURMU

#define CONFIG_PQ_MDS_PIB

*/

#ifdef CONFIG_MK_ATM

#define CONFIG_PQ_MDS_PIB

#define CONFIG_PQ_MDS_PIB_ATM

#endif

#ifdef CONFIG_MK_NAND

#define CONFIG_NAND_U_BOOT 1

#define CONFIG_RAMBOOT_NAND 1

#define CONFIG_RAMBOOT_TEXT_BASE 0xf8f82000

#endif

#ifdef CONFIG_MK_DDR2

#define CONFIG_FSL_DDR2

#endif

/* MT8JSF12864HY */

#ifdef CONFIG_MK_DDR3HY

#if defined(CONFIG_MK_DDR2)

#error "Err: enabled two kinds of DDR!"

#endif

#define CONFIG_FSL_DDR3

#define CONFIG_FSL_DDR3_RTT_WR 2

#endif

/* MT8JSF12864HZ */

#ifdef CONFIG_MK_DDR3HZ

#if defined(CONFIG_MK_DDR2) || defined(CONFIG_MK_DDR3HY)

#error "Err: enabled two/three kinds of DDR!"

#endif

#define CONFIG_FSL_DDR3

#define CONFIG_FSL_DDR3_RTT_WR 0

#endif

#if !defined(CONFIG_MK_DDR2) && !defined(CONFIG_MK_DDR3HY) && \

!defined(CONFIG_MK_DDR3HZ)

#error "Err: none of DDR is specified!"

#error " Must specify one kind of DDR(DDR2, DDR3HZ or DDR3HY)"

#endif

/*

* These can be toggled for performance analysis, otherwise use default.

*/

#define CONFIG_L2_CACHE /* toggle L2 cache */

#define CONFIG_BTB /* toggle branch predition */

/*

* Only possible on E500 Version 2 or newer cores.

*/

#define CONFIG_ENABLE_36BIT_PHYS

#define CONFIG_BOARD_EARLY_INIT_F /* Call board_pre_init */

#define CONFIG_MISC_INIT_R /* call misc_init_r() */

#define CONFIG_HWCONFIG

#define CONFIG_SYS_MEMTEST_START 0x00200000 /* memtest works on */

#define CONFIG_SYS_MEMTEST_END 0x00400000

/*

* Config the L2 Cache as L2 SRAM

*/

#define CONFIG_SYS_INIT_L2_ADDR 0xf8f80000

#define CONFIG_SYS_INIT_L2_ADDR_PHYS CONFIG_SYS_INIT_L2_ADDR

#define CONFIG_SYS_L2_SIZE (512 << 10)

#define CONFIG_SYS_INIT_L2_END (CONFIG_SYS_INIT_L2_ADDR + CONFIG_SYS_L2_SIZE)

/*

* Base addresses -- Note these are effective addresses where the

* actual resources get mapped (not physical addresses)

*/

#define CONFIG_SYS_CCSRBAR 0xD0000000 /* relocated CCSRBAR */ // See board/freescale/mpc8569mds/law.c for memory map

#define CONFIG_SYS_CCSRBAR_PHYS CONFIG_SYS_CCSRBAR

/* physical addr of CCSRBAR */

#define CONFIG_SYS_IMMR CONFIG_SYS_CCSRBAR

/* PQII uses CONFIG_SYS_IMMR */

#if defined(CONFIG_RAMBOOT_NAND) && !defined(CONFIG_NAND_SPL)

#define CONFIG_SYS_CCSRBAR_DEFAULT CONFIG_SYS_CCSRBAR

#else

#define CONFIG_SYS_CCSRBAR_DEFAULT 0xff700000 /*CCSRBAR Default */

#endif

#define CONFIG_SYS_PCI1_ADDR (CONFIG_SYS_CCSRBAR+0x8000)

#define CONFIG_SYS_PCIE1_ADDR (CONFIG_SYS_CCSRBAR+0xa000)

/* DDR Setup */

#undef CONFIG_FSL_DDR_INTERACTIVE

#define CONFIG_SPD_EEPROM /* Use SPD EEPROM for DDR setup*/ /* Not using SPD EEPROM MURMU*/

#define CONFIG_DDR_SPD

#define CONFIG_DDR_DLL /* possible DLL fix needed */

#define CONFIG_ECC_INIT_VIA_DDRCONTROLLER /* DDR controller or DMA? */

#define CONFIG_MEM_INIT_VALUE 0xDeadBeef /*0xDeadBeef */

#define CONFIG_SYS_DDR_SDRAM_BASE 0x00000000

/* DDR is system memory*/

#define CONFIG_SYS_SDRAM_BASE CONFIG_SYS_DDR_SDRAM_BASE

#define CONFIG_NUM_DDR_CONTROLLERS 1

#define CONFIG_DIMM_SLOTS_PER_CTLR 1

#define CONFIG_CHIP_SELECTS_PER_CTRL (2 * CONFIG_DIMM_SLOTS_PER_CTLR)

/* I2C addresses of SPD EEPROMs */

#define SPD_EEPROM_ADDRESS1 0x51 /* CTLR 0 DIMM 0 */ /*MURMU Since MPC8569 has dual I2C Controller, these are the controller addresses */

#define SPD_EEPROM_ADDRESS2 0x52 /* CTLR 1 DIMM 0 */

/* These are used when DDR doesn't use SPD. */

#define CONFIG_SYS_SDRAM_SIZE 2048 /* DDR is 2048MB */

#define CONFIG_SYS_DDR_CS0_BNDS 0x0000007F /* for 2048MB */

#define CONFIG_SYS_DDR_CS0_CONFIG 0x80014302 /* 15 rows, 10 cols, 3 Bank addr */

#define CONFIG_SYS_DDR_TIMING_3 0x00020000 /*0x00020000 */

#define CONFIG_SYS_DDR_TIMING_0 0x00330004

#define CONFIG_SYS_DDR_TIMING_1 0x6F6F4644 /*0x6F6B4644*/

#define CONFIG_SYS_DDR_TIMING_2 0x002888D0

#define CONFIG_SYS_DDR_SDRAM_CFG 0x47000000

#define CONFIG_SYS_DDR_SDRAM_CFG_2 0x04401040

#define CONFIG_SYS_DDR_SDRAM_MODE 0x40401521

#define CONFIG_SYS_DDR_SDRAM_MODE_2 0x8000C000

#define CONFIG_SYS_DDR_SDRAM_INTERVAL 0x03E00000

#define CONFIG_SYS_DDR_DATA_INIT 0xdeadbeef /*deadbeef*/

#define CONFIG_SYS_DDR_SDRAM_CLK_CNTL 0x01000000

#define CONFIG_SYS_DDR_TIMING_4 0x00220001

#define CONFIG_SYS_DDR_TIMING_5 0x03402400

#define CONFIG_SYS_DDR_ZQ_CNTL 0x89080600

#define CONFIG_SYS_DDR_WRLVL_CNTL 0x0655A604

#define CONFIG_SYS_DDR_CDR_1 0x80040000

#define CONFIG_SYS_DDR_CDR_2 0x00000000

#define CONFIG_SYS_DDR_OCD_CTRL 0x00000000

#define CONFIG_SYS_DDR_OCD_STATUS 0x00000000

#define CONFIG_SYS_DDR_CONTROL 0xc7000000 /* Type = DDR3 */

#define CONFIG_SYS_DDR_CONTROL2 0x24400000

#define CONFIG_SYS_DDR_ERR_INT_EN 0x0000000d

#define CONFIG_SYS_DDR_ERR_DIS 0x00000000

#define CONFIG_SYS_DDR_SBE 0x00010000

#undef CONFIG_CLOCKS_IN_MHZ

/*

* Local Bus Definitions

*/

/*addition MURMU */

#define CONFIG_SYS_FLASH_BASE 0xE0000000 //CS1 /* First flash bank , start of FLASH 256MB */

#define CONFIG_SYS_FLASH_BASE2 0xF0000000 //CS0 /* Second flash bank of 256MB */

#define CONFIG_SYS_FLASH_BASE_PHYS CONFIG_SYS_FLASH_BASE

#define CONFIG_SYS_FLASH_BANKS_LIST {CONFIG_SYS_FLASH_BASE2, CONFIG_SYS_FLASH_BASE}

#define CONFIG_SYS_CPLD_BASE 0xD0120000 /* Base addres for CPLD, FPGA, RTC etc devices */

/*Chip select 0 - Flash 2*/

#define CONFIG_FLASH_BR_PRELIM 0xF0001011 //RAJEEV 0xF0001011

#define CONFIG_FLASH_OR_PRELIM 0xF0006FF7

/*Chip select 1 - Flash 1*/

#define CONFIG_FLASH_BR1_PRELIM 0xE0001011 //RAJEEV

#define CONFIG_FLASH_OR1_PRELIM 0xF0006FF7

/* Chip Select 4 - CPLD */

#define CONFIG_SYS_BR4_PRELIM 0xD0120811

#define CONFIG_SYS_OR4_PRELIM 0xFFFFEFF7

#define CONFIG_SYS_FLASH_QUIET_TEST

#define CONFIG_FLASH_SHOW_PROGRESS 45 /* count down from 45/5: 9..1 */

#define CONFIG_SYS_MAX_FLASH_BANKS 2 //RAJEEV changed from 2 /* number of banks */

#define CONFIG_SYS_MAX_FLASH_SECT 2048 //RAJEEV Changed from 1024 /* sectors per device */

#undef CONFIG_SYS_FLASH_CHECKSUM

#define CONFIG_SYS_FLASH_ERASE_TOUT 60000 /* Flash Erase Timeout (ms) */

#define CONFIG_SYS_FLASH_WRITE_TOUT 500 /* Flash Write Timeout (ms) */

#define CONFIG_SYS_MONITOR_BASE TEXT_BASE /* start of monitor */

#if defined(CONFIG_SYS_SPL) || defined(CONFIG_RAMBOOT_NAND)

#define CONFIG_SYS_RAMBOOT

#else

#undef CONFIG_SYS_RAMBOOT

#endif

#define CONFIG_FLASH_CFI_DRIVER

#define CONFIG_SYS_FLASH_CFI

#define CONFIG_SYS_FLASH_EMPTY_INFO

/*MURMU there is no nand device

Chip select 3 - NAND

#ifndef CONFIG_NAND_SPL

#define CONFIG_SYS_NAND_BASE 0xFC000000

#else

#define CONFIG_SYS_NAND_BASE 0xFFF00000

#endif

*/

/* NAND boot: 4K NAND loader config */

/*

#define CONFIG_SYS_NAND_SPL_SIZE 0x1000

#define CONFIG_SYS_NAND_U_BOOT_SIZE ((512 << 10) - 0x2000)

#define CONFIG_SYS_NAND_U_BOOT_DST (CONFIG_SYS_INIT_L2_ADDR)

#define CONFIG_SYS_NAND_U_BOOT_START \

(CONFIG_SYS_INIT_L2_ADDR + CONFIG_SYS_NAND_SPL_SIZE)

#define CONFIG_SYS_NAND_U_BOOT_OFFS (0)

#define CONFIG_SYS_NAND_U_BOOT_RELOC (CONFIG_SYS_INIT_L2_END - 0x2000)

#define CONFIG_SYS_NAND_U_BOOT_RELOC_SP ((CONFIG_SYS_INIT_L2_END - 1) & ~0xF)

#define CONFIG_SYS_NAND_BASE_PHYS CONFIG_SYS_NAND_BASE

#define CONFIG_SYS_NAND_BASE_LIST { CONFIG_SYS_NAND_BASE, }

#define CONFIG_SYS_MAX_NAND_DEVICE 1

#define CONFIG_MTD_NAND_VERIFY_WRITE 1

#define CONFIG_CMD_NAND 1

#define CONFIG_NAND_FSL_ELBC 1

#define CONFIG_SYS_NAND_BLOCK_SIZE (128 * 1024)

#define CONFIG_NAND_BR_PRELIM (CONFIG_SYS_NAND_BASE_PHYS \

| (2<<BR_DECC_SHIFT) \

| BR_PS_8 \

| BR_MS_FCM \

| BR_V)

#define CONFIG_NAND_OR_PRELIM (0xFFFC0000 \

| OR_FCM_CSCT \

| OR_FCM_CST \

| OR_FCM_CHT \

| OR_FCM_SCY_1 \

| OR_FCM_TRLX \

| OR_FCM_EHTR)

*/

#ifdef CONFIG_RAMBOOT_NAND

#define CONFIG_SYS_BR0_PRELIM CONFIG_NAND_BR_PRELIM /* NAND Base Address */

#define CONFIG_SYS_OR0_PRELIM CONFIG_NAND_OR_PRELIM /* NAND Options */

#define CONFIG_SYS_BR3_PRELIM CONFIG_FLASH_BR_PRELIM /* NOR Base Address */

#define CONFIG_SYS_OR3_PRELIM CONFIG_FLASH_OR_PRELIM /* NOR Options */

#else

#define CONFIG_SYS_BR0_PRELIM CONFIG_FLASH_BR_PRELIM /* NOR Base Address */

#define CONFIG_SYS_OR0_PRELIM CONFIG_FLASH_OR_PRELIM /* NOR Options */

//MURMU#define CONFIG_SYS_BR3_PRELIM CONFIG_NAND_BR_PRELIM /* NAND Base Address */

//MURMU#define CONFIG_SYS_OR3_PRELIM CONFIG_NAND_OR_PRELIM /* NAND Options */

#endif

/*

* SDRAM on the LocalBus

* MURMU I dont find it's use as there is no SDRAM on localbus

*/

#define CONFIG_SYS_LBC_SDRAM_BASE 0xf0000000 /* Localbus SDRAM */

#define CONFIG_SYS_LBC_SDRAM_SIZE 64 /* LBC SDRAM is 64MB */

#define CONFIG_SYS_LBC_LCRR 0x00000004 /* LB clock ratio reg */

#define CONFIG_SYS_LBC_LBCR 0x00040000 /* LB config reg */

#define CONFIG_SYS_LBC_LSRT 0x20000000 /* LB sdram refresh timer */

#define CONFIG_SYS_LBC_MRTPR 0x00000000 /* LB refresh timer prescal*/

#define CONFIG_SYS_INIT_RAM_LOCK 1

#define CONFIG_SYS_INIT_RAM_ADDR 0xe4010000 /* Initial RAM address */

#define CONFIG_SYS_INIT_RAM_END 0x4000 /* End of used area in RAM */

#define CONFIG_SYS_GBL_DATA_SIZE 128 /* num bytes initial data */

#define CONFIG_SYS_GBL_DATA_OFFSET \

(CONFIG_SYS_INIT_RAM_END - CONFIG_SYS_GBL_DATA_SIZE)

#define CONFIG_SYS_INIT_SP_OFFSET CONFIG_SYS_GBL_DATA_OFFSET

#define CONFIG_SYS_MONITOR_LEN (256 * 1024) /* Reserve 256 kB for Mon */

#define CONFIG_SYS_MALLOC_LEN (512 * 1024) /* Reserved for malloc */

/* Serial Port */

#define CONFIG_CONS_INDEX 2 //Debdutta chagned from 1 to 2

#define CONFIG_SERIAL_MULTI 1

#undef CONFIG_SERIAL_SOFTWARE_FIFO

#define CONFIG_SYS_NS16550

#define CONFIG_SYS_NS16550_SERIAL

#define CONFIG_SYS_NS16550_REG_SIZE 1

#define CONFIG_SYS_NS16550_CLK get_bus_freq(0)

#define CONFIG_SYS_BAUDRATE_TABLE \

{300, 600, 1200, 2400, 4800, 9600, 19200, 38400,115200}

/* DUART Addresses */

//MURMU #define CONFIG_SYS_NS16550_COM1 (CONFIG_SYS_CCSRBAR+0x4500)

#define CONFIG_SYS_NS16550_COM2 (CONFIG_SYS_CCSRBAR+0x4600)

/* Use the HUSH parser*/

#define CONFIG_SYS_HUSH_PARSER

#ifdef CONFIG_SYS_HUSH_PARSER

#define CONFIG_SYS_PROMPT_HUSH_PS2 "> "

#endif

/* pass open firmware flat tree */

#define CONFIG_OF_LIBFDT 1

#define CONFIG_OF_BOARD_SETUP 1

#define CONFIG_OF_STDOUT_VIA_ALIAS 1

#define CONFIG_SYS_64BIT_VSPRINTF 1

#define CONFIG_SYS_64BIT_STRTOUL 1

/*

* I2C

*/

#define CONFIG_FSL_I2C /* Use FSL common I2C driver */

#define CONFIG_HARD_I2C /* I2C with hardware support*/

#undef CONFIG_SOFT_I2C /* I2C bit-banged */

#define CONFIG_I2C_MULTI_BUS

#define CONFIG_SYS_I2C_SPEED 400000 /* I2C speed and slave address */

#define CONFIG_SYS_I2C_SLAVE 0x7F

#define CONFIG_SYS_I2C_NOPROBES {{0,0x69}} /* Don't probe these addrs */

#define CONFIG_SYS_I2C_OFFSET 0x3000

//MURMU #define CONFIG_SYS_I2C2_OFFSET 0x3100

/*

* I2C2 EEPROM

*/

#define CONFIG_ID_EEPROM

#ifdef CONFIG_ID_EEPROM

#define CONFIG_SYS_I2C_EEPROM_NXID

#endif

#define CONFIG_SYS_I2C_EEPROM_ADDR 0x52

#define CONFIG_SYS_I2C_EEPROM_ADDR_LEN 1

#define CONFIG_SYS_EEPROM_BUS_NUM 1

#define PLPPAR1_I2C_BIT_MASK 0x0000000F

#define PLPPAR1_I2C2_VAL 0x00000000

#define PLPPAR1_ESDHC_VAL 0x0000000A

#define PLPDIR1_I2C_BIT_MASK 0x0000000F

#define PLPDIR1_I2C2_VAL 0x0000000F

#define PLPDIR1_ESDHC_VAL 0x00000006

/*MURMU CHANDRA*/

#define PLPPAR1_UART0_BIT_MASK 0x00000fc0

#define PLPPAR1_ESDHC_4BITS_VAL 0x00000a80

#define PLPDIR1_UART0_BIT_MASK 0x00000fc0

#define PLPDIR1_ESDHC_4BITS_VAL 0x00000a80

/*

* General PCI

* Memory Addresses are mapped 1-1. I/O is mapped from 0

* See board/freescale/mpc8569mds/law.c for memory map

*/

#define CONFIG_SYS_PCIE1_MEM_VIRT 0x80000000

#define CONFIG_SYS_PCIE1_MEM_BUS 0x80000000

#define CONFIG_SYS_PCIE1_MEM_PHYS 0x80000000

#define CONFIG_SYS_PCIE1_MEM_SIZE 0x10000000 /* 256M */

#define CONFIG_SYS_PCIE1_IO_VIRT 0xb0000000

#define CONFIG_SYS_PCIE1_IO_BUS 0x00000000

#define CONFIG_SYS_PCIE1_IO_PHYS 0xb0000000

#define CONFIG_SYS_PCIE1_IO_SIZE 0x20000000 /* 512M */

#define CONFIG_SYS_SRIO_MEM_VIRT 0x90000000

#define CONFIG_SYS_SRIO_MEM_BUS 0x90000000

#define CONFIG_SYS_SRIO_MEM_PHYS 0x90000000

#ifdef CONFIG_QE

/*

* QE UEC ethernet configuration

*/

#undef CONFIG_SYS_UCC_RGMII_MODE /* MURMU modified from define to undef Set UCC work at RGMII by default */

#define CONFIG_SYS_UCC_RMII_MODE /*MURMU modified from undef to define Set UCC work at RMII mode */

#ifdef CONFIG_MK_RMII

/* Set UCC work at RMII */

#if defined(CONFIG_MK_ATM)

#error "Err: ATM and RMII can't be enabled at the same time!"

#endif

#undef CONFIG_SYS_UCC_RGMII_MODE

#define CONFIG_SYS_UCC_RMII_MODE

//MURMU it is not used for MDS board; to decide whether to use it for our board #define CONFIG_PQ_MDS_PIB

#endif

#define CONFIG_MIIM_ADDRESS (CONFIG_SYS_CCSRBAR + 0x82120)

#define CONFIG_UEC_ETH

#define CONFIG_ETHPRIME "FSL UEC3"

#define CONFIG_PHY_MODE_NEED_CHANGE

#define CONFIG_UEC_ETH3 /* GETH3 */

#define CONFIG_HAS_ETH2

#ifdef CONFIG_UEC_ETH3

#define CONFIG_SYS_UEC3_UCC_NUM 2 /* UCC3 */

#define CONFIG_SYS_UEC3_RX_CLK QE_CLK_NONE

#if defined(CONFIG_SYS_UCC_RGMII_MODE)

#define CONFIG_SYS_UEC3_TX_CLK QE_CLK12

#define CONFIG_SYS_UEC3_ETH_TYPE GIGA_ETH

#define CONFIG_SYS_UEC3_PHY_ADDR 0x1 /* Phy address for RGMII */

#define CONFIG_SYS_UEC3_INTERFACE_MODE ENET_1000_RGMII_ID

#elif defined(CONFIG_SYS_UCC_RMII_MODE)

#define CONFIG_SYS_UEC3_TX_CLK QE_CLK16 /* CLK16 for RMII */

#define CONFIG_SYS_UEC3_ETH_TYPE FAST_ETH

#define CONFIG_SYS_UEC3_PHY_ADDR 0x1 /* Phy Address for RMII */

#define CONFIG_SYS_UEC3_INTERFACE_MODE ENET_100_RMII

#endif /* CONFIG_SYS_UCC_RGMII_MODE */

#endif /* CONFIG_UEC_ETH3 */

#define CONFIG_UEC_ETH4 /* GETH4 */

#define CONFIG_HAS_ETH3

#ifdef CONFIG_UEC_ETH4

#define CONFIG_SYS_UEC4_UCC_NUM 3 /* UCC4 */

#define CONFIG_SYS_UEC4_RX_CLK QE_CLK_NONE

#if defined(CONFIG_SYS_UCC_RGMII_MODE)

#define CONFIG_SYS_UEC4_TX_CLK QE_CLK17

#define CONFIG_SYS_UEC4_ETH_TYPE GIGA_ETH

#define CONFIG_SYS_UEC4_PHY_ADDR 0x2 /* Phy address for RGMII */

#define CONFIG_SYS_UEC4_INTERFACE_MODE ENET_1000_RGMII_ID

#elif defined(CONFIG_SYS_UCC_RMII_MODE)

#define CONFIG_SYS_UEC4_TX_CLK QE_CLK16 /* CLK 16 for RMII */

#define CONFIG_SYS_UEC4_ETH_TYPE FAST_ETH

#define CONFIG_SYS_UEC4_PHY_ADDR 0x2 /* Phy Address for RMII */

#define CONFIG_SYS_UEC4_INTERFACE_MODE ENET_100_RMII

#endif /* CONFIG_SYS_UCC_RGMII_MODE */

#endif /* CONFIG_UEC_ETH4 */

#undef CONFIG_UEC_ETH7 /* GETH7 */

#define CONFIG_HAS_ETH6

#ifdef CONFIG_UEC_ETH7

#define CONFIG_SYS_UEC7_UCC_NUM 6 /* UCC7 */

#define CONFIG_SYS_UEC7_RX_CLK QE_CLK_NONE

#if defined(CONFIG_SYS_UCC_RGMII_MODE)

#define CONFIG_SYS_UEC7_TX_CLK QE_CLK17

#define CONFIG_SYS_UEC7_ETH_TYPE GIGA_ETH

#define CONFIG_SYS_UEC7_PHY_ADDR 0x3 /* Phy Address for RGMII */

#define CONFIG_SYS_UEC7_INTERFACE_MODE ENET_1000_RGMII_ID

#elif defined(CONFIG_SYS_UCC_RMII_MODE)

#define CONFIG_SYS_UEC7_TX_CLK QE_CLK16 /* CLK_16 for RMII */

#define CONFIG_SYS_UEC7_ETH_TYPE FAST_ETH

#define CONFIG_SYS_UEC7_PHY_ADDR 0x3 /* Phy Address for RMII */

#define CONFIG_SYS_UEC7_INTERFACE_MODE ENET_100_RMII

#endif /* CONFIG_SYS_UCC_RGMII_MODE */

#endif /* CONFIG_UEC_ETH7 */

#endif /* CONFIG_QE */

#if defined(CONFIG_PCI)

#define CONFIG_NET_MULTI

#define CONFIG_PCI_PNP /* do pci plug-and-play */

#undef CONFIG_EEPRO100

#undef CONFIG_TULIP

#define CONFIG_PCI_SCAN_SHOW /* show pci devices on startup */

#endif /* CONFIG_PCI */

#ifndef CONFIG_NET_MULTI

#define CONFIG_NET_MULTI 1

#endif

/*

* Environment

*/

#if defined(CONFIG_SYS_RAMBOOT)

#if defined(CONFIG_RAMBOOT_NAND)

#define CONFIG_ENV_IS_IN_NAND 1

#define CONFIG_ENV_SIZE CONFIG_SYS_NAND_BLOCK_SIZE

#define CONFIG_ENV_OFFSET ((512 * 1024) + CONFIG_SYS_NAND_BLOCK_SIZE)

#endif

#else

#define CONFIG_ENV_IS_IN_FLASH 1

#define CONFIG_ENV_ADDR (CONFIG_SYS_MONITOR_BASE - CONFIG_ENV_SECT_SIZE)

#define CONFIG_ENV_SECT_SIZE 0x20000 /* 256K(one sector) for env */

#define CONFIG_ENV_SIZE CONFIG_ENV_SECT_SIZE

#endif

#define CONFIG_LOADS_ECHO 1 /* echo on for serial download */

#define CONFIG_SYS_LOADS_BAUD_CHANGE 1 /* allow baudrate change */

/* QE microcode/firmware address */

#define CONFIG_SYS_QE_FW_ADDR 0xfff00000

/*

* BOOTP options

*/

#define CONFIG_BOOTP_BOOTFILESIZE

#define CONFIG_BOOTP_BOOTPATH

#define CONFIG_BOOTP_GATEWAY

#define CONFIG_BOOTP_HOSTNAME

/*

* Command line configuration.

*/

#include <config_cmd_default.h>

#define CONFIG_CMD_PING

#define CONFIG_CMD_I2C

#define CONFIG_CMD_MII

#define CONFIG_CMD_ELF

#define CONFIG_CMD_IRQ

#define CONFIG_CMD_SETEXPR

#if defined(CONFIG_PCI)

#define CONFIG_CMD_PCI

#endif

#undef CONFIG_WATCHDOG /* watchdog disabled */

#define CONFIG_MMC 1

#ifdef CONFIG_MMC

#define CONFIG_FSL_ESDHC

#define CONFIG_SYS_FSL_ESDHC_ADDR CONFIG_SYS_MPC85xx_ESDHC_ADDR

#define CONFIG_CMD_MMC

#define CONFIG_GENERIC_MMC

#define CONFIG_CMD_EXT2

#define CONFIG_CMD_FAT

#define CONFIG_DOS_PARTITION

#endif

/*

* Miscellaneous configurable options

*/

#define CONFIG_SYS_LONGHELP /* undef to save memory */

#define CONFIG_CMDLINE_EDITING /* Command-line editing */

#define CONFIG_SYS_LOAD_ADDR 0x1000000 /* default load address */

#define CONFIG_SYS_PROMPT "SCM3_MCP=> " /* Monitor Command Prompt *///RAJEEV

#if defined(CONFIG_CMD_KGDB)

#define CONFIG_SYS_CBSIZE 2048 /* Console I/O Buffer Size */

#else

#define CONFIG_SYS_CBSIZE 512 /* Console I/O Buffer Size */

#endif

#define CONFIG_SYS_PBSIZE (CONFIG_SYS_CBSIZE+sizeof(CONFIG_SYS_PROMPT)+16)

/* Print Buffer Size */

#define CONFIG_SYS_MAXARGS 32 /* max number of command args */

#define CONFIG_SYS_BARGSIZE CONFIG_SYS_CBSIZE

/* Boot Argument Buffer Size */

#define CONFIG_SYS_HZ 1000 /* decrementer freq: 1ms ticks */

/*

* For booting Linux, the board info and command line data

* have to be in the first 16 MB of memory, since this is

* the maximum mapped by the Linux kernel during initialization.

*/

#define CONFIG_SYS_BOOTMAPSZ (16 << 20)

/* Initial Memory map for Linux*/

/*

* Internal Definitions

*

* Boot Flags

*/

#define BOOTFLAG_COLD 0x01 /* Normal Power-On: Boot from FLASH */

#define BOOTFLAG_WARM 0x02 /* Software reboot */

#if defined(CONFIG_CMD_KGDB)

#define CONFIG_KGDB_BAUDRATE 230400 /* speed to run kgdb serial port */

#define CONFIG_KGDB_SER_INDEX 2 /* which serial port to use */

#endif

/*

* Environment Configuration

*/

#define CONFIG_HOSTNAME SCM3-MCP

//#define CONFIG_ROOTPATH /nfsroot

#define CONFIG_ROOTPATH /root

#define CONFIG_BOOTFILE uImage

#define CONFIG_SERVERIP 192.168.8.117

#define CONFIG_GATEWAYIP 192.168.8.1

#define CONFIG_NETMASK 255.255.255.0

#define CONFIG_IPADDR 192.168.8.203

#define CONFIG_ETHADDR 76:00:00:98:74:1A

#define CONFIG_ETH1ADDR 76:00:00:98:74:1B

#define CONFIG_ETH2ADDR 76:00:00:98:74:1C

#define CONFIG_ENABLE_ESDHC esdhc //Debdutta

#define CONFIG_LOADADDR 1000000 /*default location for tftp and bootm*/

#define CONFIG_BOOTDELAY 3 /* -1 disables auto-boot */

/* #undef CONFIG_BOOTARGS */ /* the boot command will set bootargs*/

#define CONFIG_BAUDRATE 115200

#define CONFIG_CARD_TYPE cdot_scm_mcp003 /* Type of the card */

#define CONFIG_BOOTARGS "console=ttyS1,115200n8 root=/dev/mtdblock0 rw rootfstype=jffs2 ip=off"

#define CONFIG_EXTRA_ENV_SETTINGS \

"netdev=eth0\0" \

"consoledev=ttyS0\0" \

"ramdiskaddr=600000\0" \

"ramdiskfile=your.ramdisk.u-boot\0" \

"fdtaddr=400000\0" \

"fdtfile=your.fdt.dtb\0" \

"nfsargs=setenv bootargs root=/dev/nfs rw " \

"nfsroot=$serverip:$rootpath " \

"ip=$ipaddr:$serverip:$gatewayip:$netmask:$hostname:$netdev:off " \

"console=$consoledev,$baudrate $othbootargs\0" \

"ramargs=setenv bootargs root=/dev/ram rw " \

"console=$consoledev,$baudrate $othbootargs\0" \

#define CONFIG_NFSBOOTCOMMAND \

"run nfsargs;" \

"tftp $loadaddr $bootfile;" \

"tftp $fdtaddr $fdtfile;" \

"bootm $loadaddr - $fdtaddr"

#define CONFIG_RAMBOOTCOMMAND \

"run ramargs;" \

"tftp $ramdiskaddr $ramdiskfile;" \

"tftp $loadaddr $bootfile;" \

"bootm $loadaddr $ramdiskaddr"

#define CONFIG_BOOTCOMMAND "run bootargs;bootm 0xffce0000 - 0xfff40000"

#endif /* __CONFIG_H */

***********************************************************************************************

The tlb.c file:

***********************************************************************************************

/*

* Copyright 2009 Freescale Semiconductor, Inc.

*

* (C) Copyright 2000

* Wolfgang Denk, DENX Software Engineering, wd@denx.de.

*

* See file CREDITS for list of people who contributed to this

* project.

*

* This program is free software; you can redistribute it and/or

* modify it under the terms of the GNU General Public License as

* published by the Free Software Foundation; either version 2 of

* the License, or (at your option) any later version.

*

* This program is distributed in the hope that it will be useful,

* but WITHOUT ANY WARRANTY; without even the implied warranty of

* MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the

* GNU General Public License for more details.

*

* You should have received a copy of the GNU General Public License

* along with this program; if not, write to the Free Software

* Foundation, Inc., 59 Temple Place, Suite 330, Boston,

* MA 02111-1307 USA

*/

#include <common.h>

#include <asm/mmu.h>

struct fsl_e_tlb_entry tlb_table[] = {

/* TLB 0 - for temp stack in cache */

SET_TLB_ENTRY(0, CONFIG_SYS_INIT_RAM_ADDR, CONFIG_SYS_INIT_RAM_ADDR,

MAS3_SX|MAS3_SW|MAS3_SR, 0,

0, 0, BOOKE_PAGESZ_4K, 0),

SET_TLB_ENTRY(0, CONFIG_SYS_INIT_RAM_ADDR + 4 * 1024,

CONFIG_SYS_INIT_RAM_ADDR + 4 * 1024,

MAS3_SX|MAS3_SW|MAS3_SR, 0,

0, 0, BOOKE_PAGESZ_4K, 0),

SET_TLB_ENTRY(0, CONFIG_SYS_INIT_RAM_ADDR + 8 * 1024,

CONFIG_SYS_INIT_RAM_ADDR + 8 * 1024,

MAS3_SX|MAS3_SW|MAS3_SR, 0,

0, 0, BOOKE_PAGESZ_4K, 0),

SET_TLB_ENTRY(0, CONFIG_SYS_INIT_RAM_ADDR + 12 * 1024,

CONFIG_SYS_INIT_RAM_ADDR + 12 * 1024,

MAS3_SX|MAS3_SW|MAS3_SR, 0,

0, 0, BOOKE_PAGESZ_4K, 0),

/* TLB 1 Initializations */

/*

* TLBe 0: 64M Non-cacheable, guarded

* Out of reset this entry is only 4K.

* 0xfc000000 256K NAND FLASH (CS3)

* 0xfe000000 32M NOR FLASH (CS0)

*/

//SET_TLB_ENTRY(1, CONFIG_SYS_NAND_BASE, CONFIG_SYS_NAND_BASE,

// MAS3_SX|MAS3_SW|MAS3_SR, MAS2_I|MAS2_G,

// 0, 0, BOOKE_PAGESZ_64M, 1),

SET_TLB_ENTRY(1, CONFIG_SYS_FLASH_BASE2, CONFIG_SYS_FLASH_BASE2,

MAS3_SX|MAS3_SW|MAS3_SR, MAS2_I|MAS2_G,

0, 0, BOOKE_PAGESZ_256M, 1),

SET_TLB_ENTRY(1, CONFIG_SYS_FLASH_BASE, CONFIG_SYS_FLASH_BASE,

MAS3_SX|MAS3_SW|MAS3_SR, MAS2_I|MAS2_G,

0, 1, BOOKE_PAGESZ_256M, 1),

/*

* TLBe 1: 256KB Non-cacheable, guarded

* 0xf8000000 32K BCSR

* 0xf8008000 32K PIB (CS4)

* 0xf8010000 32K PIB (CS5)

*/

//MURMU SET_TLB_ENTRY(1, CONFIG_SYS_BCSR_BASE, CONFIG_SYS_BCSR_BASE_PHYS,

// MAS3_SX|MAS3_SW|MAS3_SR, MAS2_I|MAS2_G,

// 0, 1, BOOKE_PAGESZ_256K, 1),

/*

* TLBe 2: 256M Non-cacheable, guarded

* 0xa00000000 256M PCIe MEM (lower half)

*/

SET_TLB_ENTRY(1, CONFIG_SYS_PCIE1_MEM_VIRT, CONFIG_SYS_PCIE1_MEM_PHYS,

MAS3_SX|MAS3_SW|MAS3_SR, MAS2_I|MAS2_G,

0, 1, BOOKE_PAGESZ_256M, 1),

/*

* TLBe 3: 256M Non-cacheable, guarded

* 0xb00000000 256M PCIe MEM (higher half)

*/

SET_TLB_ENTRY(1, (CONFIG_SYS_PCIE1_MEM_VIRT + 0x10000000),

(CONFIG_SYS_PCIE1_MEM_PHYS + 0x10000000),

MAS3_SX|MAS3_SW|MAS3_SR, MAS2_I|MAS2_G,

0, 2, BOOKE_PAGESZ_256M, 1),

/*

* TLBe 4: 64M Non-cacheable, guarded

* 0xe000_0000 1M CCSRBAR

* 0xe280_0000 8M PCIe IO

*/

SET_TLB_ENTRY(1, CONFIG_SYS_CCSRBAR, CONFIG_SYS_CCSRBAR_PHYS,

MAS3_SX|MAS3_SW|MAS3_SR, MAS2_I|MAS2_G,

0, 3, BOOKE_PAGESZ_64M, 1),

/*

SET_TLB_ENTRY(1, CONFIG_SYS_PCIE1_IO_VIRT, CONFIG_SYS_PCIE1_IO_PHYS,

MAS3_SX|MAS3_SW|MAS3_SR, MAS2_I|MAS2_G,

0, 4, BOOKE_PAGESZ_256M, 1),

*/

#if defined(CONFIG_SYS_RAMBOOT) && defined(CONFIG_SYS_INIT_L2_ADDR)

/* *I*G - L2SRAM */

SET_TLB_ENTRY(1, CONFIG_SYS_INIT_L2_ADDR, CONFIG_SYS_INIT_L2_ADDR_PHYS,

MAS3_SX|MAS3_SW|MAS3_SR, MAS2_I|MAS2_G,

0, 4, BOOKE_PAGESZ_256K, 1),

SET_TLB_ENTRY(1, CONFIG_SYS_INIT_L2_ADDR + 0x40000,

CONFIG_SYS_INIT_L2_ADDR_PHYS + 0x40000,

MAS3_SX|MAS3_SW|MAS3_SR, MAS2_I|MAS2_G,

0, 5, BOOKE_PAGESZ_256K, 1),

#endif

};

int num_tlb_entries = ARRAY_SIZE(tlb_table);

***********************************************************************************************

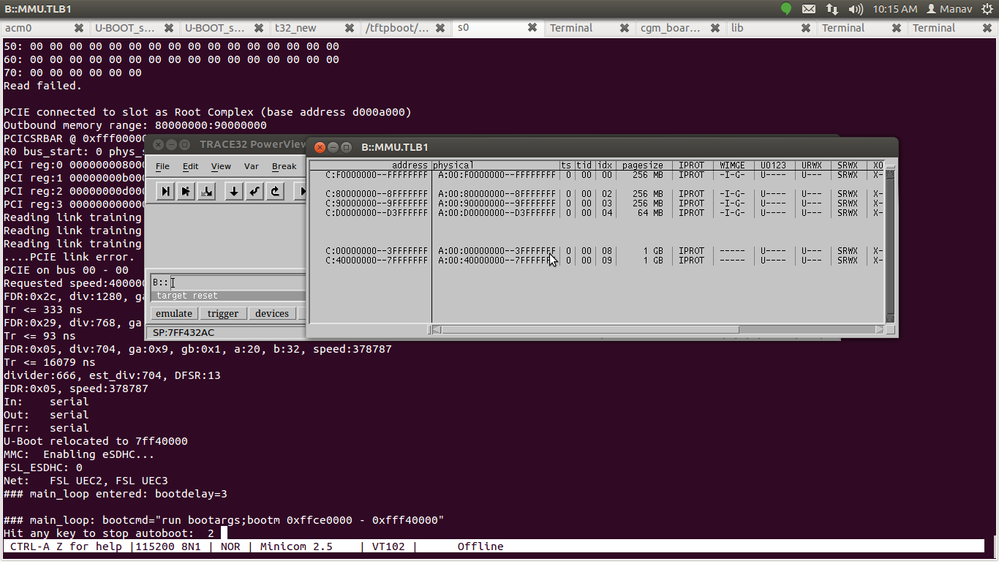

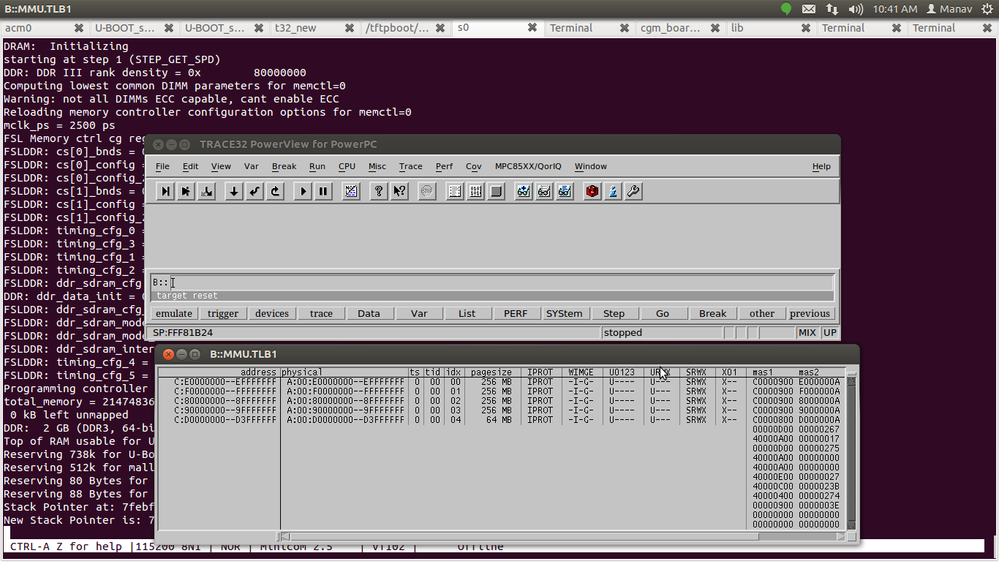

And the Snapshot of TLB1 from lauterback debugger after crash occurs is attached.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The TLB entry for CONFIG_SYS_PCIE1_MEM_VIRT is using ESEL1 and overwriting the entry that maps flash (sorry for not noticing this in what you had posted before). You swapped "FLASH_BASE" with "FLASH_BASE2" relative to the code snippet you posted earlier, which is why the faulting address is still 0xe0000000 and not somewhere in the second half.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Scott,

Yeah I noticed it too later !! I corrected It.

Now I am gonna show you two configurations. This should really narrow down. Please hold on a little more with me.

1. The one where CCSRBAR is relocated (from 0xE0000000 to 0xD0000000) and I am using only CS0. (Its working fine)

2. The one where CCSRBAR is relocated (from 0xE0000000 to 0xD0000000) and I am using both flash banks. (Uboot not running at all)

***************************************************************************************************************

***************************************************************************************************************

FIRST CONFIGURATION

File: include/configs/MPC8569MDS.h

/*

* Copyright (C) 2009-2010 Freescale Semiconductor, Inc.

*

* See file CREDITS for list of people who contributed to this

* project.

*

* This program is free software; you can redistribute it and/or

* modify it under the terms of the GNU General Public License as

* published by the Free Software Foundation; either version 2 of

* the License, or (at your option) any later version.

*

* This program is distributed in the hope that it will be useful,

* but WITHOUT ANY WARRANTY; without even the implied warranty of

* MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the

* GNU General Public License for more details.

*

* You should have received a copy of the GNU General Public License

* along with this program; if not, write to the Free Software

* Foundation, Inc., 59 Temple Place, Suite 330, Boston,

* MA 02111-1307 USA

*/

/*

* mpc8569mds board configuration file

*/

#ifndef __CONFIG_H

#define __CONFIG_H

/* High Level Configuration Options */

#define CONFIG_BOOKE 1 /* BOOKE */

#define CONFIG_E500 1 /* BOOKE e500 family */

#define CONFIG_MPC85xx 1 /* MPC8540/60/55/41/48/68 */

#define CONFIG_MPC8569 1 /* MPC8569 specific */

#define CONFIG_MPC8569MDS 1 /* MPC8569MDS board specific */

/*

#define CONFIG_POST 1

#define CONFIG_SYS_POST_MEMORY 1

*/

#define CONFIG_FSL_ELBC 1 /* Has Enhance localbus controller */

#define CONFIG_PCI 1 /* Disable PCI/PCIE */

#define CONFIG_PCIE1 1 /* PCIE controller */

#define CONFIG_FSL_PCI_INIT 1 /* use common fsl pci init code */

#define CONFIG_FSL_PCIE_RESET 1 /* need PCIe reset errata */

#define CONFIG_SYS_PCI_64BIT 1 /* enable 64-bit PCI resources */

#define CONFIG_QE /* Enable QE */

#define CONFIG_ENV_OVERWRITE

#define CONFIG_FSL_LAW 1 /* Use common FSL init code */

#ifndef __ASSEMBLY__

extern unsigned long get_clock_freq(void);

#endif

/* Replace a call to get_clock_freq (after it is implemented)*/

#define CONFIG_SYS_CLK_FREQ 66666666

#define CONFIG_DDR_CLK_FREQ CONFIG_SYS_CLK_FREQ

/*#define CONFIG_DDR_CLK_FREQ 40000000 */

/*MURMU

#define CONFIG_PQ_MDS_PIB

*/

#ifdef CONFIG_MK_ATM

#define CONFIG_PQ_MDS_PIB

#define CONFIG_PQ_MDS_PIB_ATM

#endif

#ifdef CONFIG_MK_NAND

#define CONFIG_NAND_U_BOOT 1

#define CONFIG_RAMBOOT_NAND 1

#define CONFIG_RAMBOOT_TEXT_BASE 0xf8f82000

#endif

#ifdef CONFIG_MK_DDR2

#define CONFIG_FSL_DDR2

#endif

/* MT8JSF12864HY */

#ifdef CONFIG_MK_DDR3HY

#if defined(CONFIG_MK_DDR2)

#error "Err: enabled two kinds of DDR!"

#endif

#define CONFIG_FSL_DDR3

#define CONFIG_FSL_DDR3_RTT_WR 2

#endif

/* MT8JSF12864HZ */

#ifdef CONFIG_MK_DDR3HZ

#if defined(CONFIG_MK_DDR2) || defined(CONFIG_MK_DDR3HY)

#error "Err: enabled two/three kinds of DDR!"

#endif

#define CONFIG_FSL_DDR3

#define CONFIG_FSL_DDR3_RTT_WR 0

#endif

#if !defined(CONFIG_MK_DDR2) && !defined(CONFIG_MK_DDR3HY) && \

!defined(CONFIG_MK_DDR3HZ)

#error "Err: none of DDR is specified!"

#error " Must specify one kind of DDR(DDR2, DDR3HZ or DDR3HY)"

#endif

/*

* These can be toggled for performance analysis, otherwise use default.

*/

#define CONFIG_L2_CACHE /* toggle L2 cache */

#define CONFIG_BTB /* toggle branch predition */

/*

* Only possible on E500 Version 2 or newer cores.

*/

#define CONFIG_ENABLE_36BIT_PHYS

#define CONFIG_BOARD_EARLY_INIT_F /* Call board_pre_init */

#define CONFIG_MISC_INIT_R /* call misc_init_r() */

#define CONFIG_HWCONFIG

#define CONFIG_SYS_MEMTEST_START 0x00200000 /* memtest works on */

#define CONFIG_SYS_MEMTEST_END 0x00400000

/*

* Config the L2 Cache as L2 SRAM

*/

#define CONFIG_SYS_INIT_L2_ADDR 0xf8f80000

#define CONFIG_SYS_INIT_L2_ADDR_PHYS CONFIG_SYS_INIT_L2_ADDR

#define CONFIG_SYS_L2_SIZE (512 << 10)

#define CONFIG_SYS_INIT_L2_END (CONFIG_SYS_INIT_L2_ADDR + CONFIG_SYS_L2_SIZE)

/*

* Base addresses -- Note these are effective addresses where the

* actual resources get mapped (not physical addresses)

*/

#define CONFIG_SYS_CCSRBAR 0xD0000000 /* relocated CCSRBAR */ // See board/freescale/mpc8569mds/law.c for memory map

#define CONFIG_SYS_CCSRBAR_PHYS CONFIG_SYS_CCSRBAR

/* physical addr of CCSRBAR */

#define CONFIG_SYS_IMMR CONFIG_SYS_CCSRBAR

/* PQII uses CONFIG_SYS_IMMR */

#if defined(CONFIG_RAMBOOT_NAND) && !defined(CONFIG_NAND_SPL)

#define CONFIG_SYS_CCSRBAR_DEFAULT CONFIG_SYS_CCSRBAR

#else

#define CONFIG_SYS_CCSRBAR_DEFAULT 0xff700000 /*CCSRBAR Default */

#endif

#define CONFIG_SYS_PCI1_ADDR (CONFIG_SYS_CCSRBAR+0x8000)

#define CONFIG_SYS_PCIE1_ADDR (CONFIG_SYS_CCSRBAR+0xa000)

/* DDR Setup */

#undef CONFIG_FSL_DDR_INTERACTIVE

#define CONFIG_SPD_EEPROM /* Use SPD EEPROM for DDR setup*/ /* Not using SPD EEPROM MURMU*/

#define CONFIG_DDR_SPD

#define CONFIG_DDR_DLL /* possible DLL fix needed */

#define CONFIG_ECC_INIT_VIA_DDRCONTROLLER /* DDR controller or DMA? */

#define CONFIG_MEM_INIT_VALUE 0xDeadBeef /*0xDeadBeef */

#define CONFIG_SYS_DDR_SDRAM_BASE 0x00000000

/* DDR is system memory*/

#define CONFIG_SYS_SDRAM_BASE CONFIG_SYS_DDR_SDRAM_BASE

#define CONFIG_NUM_DDR_CONTROLLERS 1

#define CONFIG_DIMM_SLOTS_PER_CTLR 1

#define CONFIG_CHIP_SELECTS_PER_CTRL (2 * CONFIG_DIMM_SLOTS_PER_CTLR)

/* I2C addresses of SPD EEPROMs */

#define SPD_EEPROM_ADDRESS1 0x51 /* CTLR 0 DIMM 0 */ /*MURMU Since MPC8569 has dual I2C Controller, these are the controller addresses */

#define SPD_EEPROM_ADDRESS2 0x52 /* CTLR 1 DIMM 0 */

/* These are used when DDR doesn't use SPD. */

#define CONFIG_SYS_SDRAM_SIZE 2048 /* DDR is 2048MB */

#define CONFIG_SYS_DDR_CS0_BNDS 0x0000007F /* for 2048MB */

#define CONFIG_SYS_DDR_CS0_CONFIG 0x80014302 /* 15 rows, 10 cols, 3 Bank addr */

#define CONFIG_SYS_DDR_TIMING_3 0x00020000 /*0x00020000 */

#define CONFIG_SYS_DDR_TIMING_0 0x00330004

#define CONFIG_SYS_DDR_TIMING_1 0x6F6F4644 /*0x6F6B4644*/

#define CONFIG_SYS_DDR_TIMING_2 0x002888D0

#define CONFIG_SYS_DDR_SDRAM_CFG 0x47000000

#define CONFIG_SYS_DDR_SDRAM_CFG_2 0x04401040

#define CONFIG_SYS_DDR_SDRAM_MODE 0x40401521

#define CONFIG_SYS_DDR_SDRAM_MODE_2 0x8000C000

#define CONFIG_SYS_DDR_SDRAM_INTERVAL 0x03E00000

#define CONFIG_SYS_DDR_DATA_INIT 0xdeadbeef /*deadbeef*/

#define CONFIG_SYS_DDR_SDRAM_CLK_CNTL 0x01000000

#define CONFIG_SYS_DDR_TIMING_4 0x00220001

#define CONFIG_SYS_DDR_TIMING_5 0x03402400

#define CONFIG_SYS_DDR_ZQ_CNTL 0x89080600

#define CONFIG_SYS_DDR_WRLVL_CNTL 0x0655A604

#define CONFIG_SYS_DDR_CDR_1 0x80040000

#define CONFIG_SYS_DDR_CDR_2 0x00000000

#define CONFIG_SYS_DDR_OCD_CTRL 0x00000000

#define CONFIG_SYS_DDR_OCD_STATUS 0x00000000

#define CONFIG_SYS_DDR_CONTROL 0xc7000000 /* Type = DDR3 */

#define CONFIG_SYS_DDR_CONTROL2 0x24400000

#define CONFIG_SYS_DDR_ERR_INT_EN 0x0000000d

#define CONFIG_SYS_DDR_ERR_DIS 0x00000000

#define CONFIG_SYS_DDR_SBE 0x00010000

#undef CONFIG_CLOCKS_IN_MHZ

/*

* Local Bus Definitions

*/

/*addition MURMU */

#define CONFIG_SYS_FLASH_BASE 0xF0000000 //CS0 /* Second flash bank of 256MB */

#define CONFIG_SYS_FLASH_BASE_PHYS CONFIG_SYS_FLASH_BASE

#define CONFIG_SYS_CPLD_BASE 0xD0120000 /* Base addres for CPLD, FPGA, RTC etc devices */

/*Chip select 0 - Flash 2*/

#define CONFIG_FLASH_BR_PRELIM 0xF0001011 // 0xF0001011

#define CONFIG_FLASH_OR_PRELIM 0xF0006FF7

* Chip Select 4 - CPLD */

#define CONFIG_SYS_BR4_PRELIM 0xD0120811

#define CONFIG_SYS_OR4_PRELIM 0xFFFFEFF7

#define CONFIG_SYS_FLASH_QUIET_TEST

#define CONFIG_FLASH_SHOW_PROGRESS 45 /* count down from 45/5: 9..1 */

#define CONFIG_SYS_MAX_FLASH_BANKS 1 // changed from 2 /* number of banks */

#define CONFIG_SYS_MAX_FLASH_SECT 2048 // Changed from 1024 /* sectors per device */

#undef CONFIG_SYS_FLASH_CHECKSUM

#define CONFIG_SYS_FLASH_ERASE_TOUT 60000 /* Flash Erase Timeout (ms) */

#define CONFIG_SYS_FLASH_WRITE_TOUT 500 /* Flash Write Timeout (ms) */

#define CONFIG_SYS_MONITOR_BASE TEXT_BASE /* start of monitor */

#if defined(CONFIG_SYS_SPL) || defined(CONFIG_RAMBOOT_NAND)

#define CONFIG_SYS_RAMBOOT

#else

#undef CONFIG_SYS_RAMBOOT

#endif

#define CONFIG_FLASH_CFI_DRIVER

#define CONFIG_SYS_FLASH_CFI

#define CONFIG_SYS_FLASH_EMPTY_INFO

/*MURMU there is no nand device

Chip select 3 - NAND

#ifndef CONFIG_NAND_SPL

#define CONFIG_SYS_NAND_BASE 0xFC000000

#else

#define CONFIG_SYS_NAND_BASE 0xFFF00000

#endif

*/

/* NAND boot: 4K NAND loader config */

/*

#define CONFIG_SYS_NAND_SPL_SIZE 0x1000

#define CONFIG_SYS_NAND_U_BOOT_SIZE ((512 << 10) - 0x2000)

#define CONFIG_SYS_NAND_U_BOOT_DST (CONFIG_SYS_INIT_L2_ADDR)

#define CONFIG_SYS_NAND_U_BOOT_START \

(CONFIG_SYS_INIT_L2_ADDR + CONFIG_SYS_NAND_SPL_SIZE)

#define CONFIG_SYS_NAND_U_BOOT_OFFS (0)

#define CONFIG_SYS_NAND_U_BOOT_RELOC (CONFIG_SYS_INIT_L2_END - 0x2000)

#define CONFIG_SYS_NAND_U_BOOT_RELOC_SP ((CONFIG_SYS_INIT_L2_END - 1) & ~0xF)

#define CONFIG_SYS_NAND_BASE_PHYS CONFIG_SYS_NAND_BASE

#define CONFIG_SYS_NAND_BASE_LIST { CONFIG_SYS_NAND_BASE, }

#define CONFIG_SYS_MAX_NAND_DEVICE 1

#define CONFIG_MTD_NAND_VERIFY_WRITE 1

#define CONFIG_CMD_NAND 1

#define CONFIG_NAND_FSL_ELBC 1

#define CONFIG_SYS_NAND_BLOCK_SIZE (128 * 1024)

#define CONFIG_NAND_BR_PRELIM (CONFIG_SYS_NAND_BASE_PHYS \

| (2<<BR_DECC_SHIFT) \

| BR_PS_8 \

| BR_MS_FCM \

| BR_V)

#define CONFIG_NAND_OR_PRELIM (0xFFFC0000 \

| OR_FCM_CSCT \

| OR_FCM_CST \

| OR_FCM_CHT \

| OR_FCM_SCY_1 \

| OR_FCM_TRLX \

| OR_FCM_EHTR)

*/

#ifdef CONFIG_RAMBOOT_NAND

#define CONFIG_SYS_BR0_PRELIM CONFIG_NAND_BR_PRELIM /* NAND Base Address */

#define CONFIG_SYS_OR0_PRELIM CONFIG_NAND_OR_PRELIM /* NAND Options */

#define CONFIG_SYS_BR3_PRELIM CONFIG_FLASH_BR_PRELIM /* NOR Base Address */

#define CONFIG_SYS_OR3_PRELIM CONFIG_FLASH_OR_PRELIM /* NOR Options */

#else

#define CONFIG_SYS_BR0_PRELIM CONFIG_FLASH_BR_PRELIM /* NOR Base Address */

#define CONFIG_SYS_OR0_PRELIM CONFIG_FLASH_OR_PRELIM /* NOR Options */

//MURMU#define CONFIG_SYS_BR3_PRELIM CONFIG_NAND_BR_PRELIM /* NAND Base Address */

//MURMU#define CONFIG_SYS_OR3_PRELIM CONFIG_NAND_OR_PRELIM /* NAND Options */

#endif

/*

* SDRAM on the LocalBus

* MURMU I dont find it's use as there is no SDRAM on localbus

*/

#define CONFIG_SYS_LBC_SDRAM_BASE 0xf0000000 /* Localbus SDRAM */

#define CONFIG_SYS_LBC_SDRAM_SIZE 64 /* LBC SDRAM is 64MB */

#define CONFIG_SYS_LBC_LCRR 0x00000004 /* LB clock ratio reg */

#define CONFIG_SYS_LBC_LBCR 0x00040000 /* LB config reg */

#define CONFIG_SYS_LBC_LSRT 0x20000000 /* LB sdram refresh timer */

#define CONFIG_SYS_LBC_MRTPR 0x00000000 /* LB refresh timer prescal*/

#define CONFIG_SYS_INIT_RAM_LOCK 1

#define CONFIG_SYS_INIT_RAM_ADDR 0xe4010000 /* Initial RAM address */

#define CONFIG_SYS_INIT_RAM_END 0x4000 /* End of used area in RAM */

#define CONFIG_SYS_GBL_DATA_SIZE 128 /* num bytes initial data */

#define CONFIG_SYS_GBL_DATA_OFFSET \

(CONFIG_SYS_INIT_RAM_END - CONFIG_SYS_GBL_DATA_SIZE)

#define CONFIG_SYS_INIT_SP_OFFSET CONFIG_SYS_GBL_DATA_OFFSET

#define CONFIG_SYS_MONITOR_LEN (256 * 1024) /* Reserve 256 kB for Mon */

#define CONFIG_SYS_MALLOC_LEN (512 * 1024) /* Reserved for malloc */

/* Serial Port */

#define CONFIG_CONS_INDEX 2 //Debdutta chagned from 1 to 2

#define CONFIG_SERIAL_MULTI 1

#undef CONFIG_SERIAL_SOFTWARE_FIFO

#define CONFIG_SYS_NS16550

#define CONFIG_SYS_NS16550_SERIAL

#define CONFIG_SYS_NS16550_REG_SIZE 1

#define CONFIG_SYS_NS16550_CLK get_bus_freq(0)

#define CONFIG_SYS_BAUDRATE_TABLE \

{300, 600, 1200, 2400, 4800, 9600, 19200, 38400,115200}

/* DUART Addresses */

//MURMU #define CONFIG_SYS_NS16550_COM1 (CONFIG_SYS_CCSRBAR+0x4500)

#define CONFIG_SYS_NS16550_COM2 (CONFIG_SYS_CCSRBAR+0x4600)

/* Use the HUSH parser*/

#define CONFIG_SYS_HUSH_PARSER

#ifdef CONFIG_SYS_HUSH_PARSER

#define CONFIG_SYS_PROMPT_HUSH_PS2 "> "

#endif

/* pass open firmware flat tree */

#define CONFIG_OF_LIBFDT 1

#define CONFIG_OF_BOARD_SETUP 1

#define CONFIG_OF_STDOUT_VIA_ALIAS 1

#define CONFIG_SYS_64BIT_VSPRINTF 1

#define CONFIG_SYS_64BIT_STRTOUL 1

/*

* I2C

*/

#define CONFIG_FSL_I2C /* Use FSL common I2C driver */

#define CONFIG_HARD_I2C /* I2C with hardware support*/

#undef CONFIG_SOFT_I2C /* I2C bit-banged */

#define CONFIG_I2C_MULTI_BUS

#define CONFIG_SYS_I2C_SPEED 400000 /* I2C speed and slave address */

#define CONFIG_SYS_I2C_SLAVE 0x7F

#define CONFIG_SYS_I2C_NOPROBES {{0,0x69}} /* Don't probe these addrs */

#define CONFIG_SYS_I2C_OFFSET 0x3000

//MURMU #define CONFIG_SYS_I2C2_OFFSET 0x3100

/*

* I2C2 EEPROM

*/

#define CONFIG_ID_EEPROM

#ifdef CONFIG_ID_EEPROM

#define CONFIG_SYS_I2C_EEPROM_NXID

#endif

#define CONFIG_SYS_I2C_EEPROM_ADDR 0x52

#define CONFIG_SYS_I2C_EEPROM_ADDR_LEN 1

#define CONFIG_SYS_EEPROM_BUS_NUM 1

#define PLPPAR1_I2C_BIT_MASK 0x0000000F

#define PLPPAR1_I2C2_VAL 0x00000000

#define PLPPAR1_ESDHC_VAL 0x0000000A

#define PLPDIR1_I2C_BIT_MASK 0x0000000F

#define PLPDIR1_I2C2_VAL 0x0000000F

#define PLPDIR1_ESDHC_VAL 0x00000006

/*MURMU CHANDRA*/

#define PLPPAR1_UART0_BIT_MASK 0x00000fc0

#define PLPPAR1_ESDHC_4BITS_VAL 0x00000a80

#define PLPDIR1_UART0_BIT_MASK 0x00000fc0

#define PLPDIR1_ESDHC_4BITS_VAL 0x00000a80

/*

* General PCI

* Memory Addresses are mapped 1-1. I/O is mapped from 0

* See board/freescale/mpc8569mds/law.c for memory map

*/

#define CONFIG_SYS_PCIE1_MEM_VIRT 0x80000000

#define CONFIG_SYS_PCIE1_MEM_BUS 0x80000000

#define CONFIG_SYS_PCIE1_MEM_PHYS 0x80000000

#define CONFIG_SYS_PCIE1_MEM_SIZE 0x10000000 /* 256M */

#define CONFIG_SYS_PCIE1_IO_VIRT 0xb0000000

#define CONFIG_SYS_PCIE1_IO_BUS 0x00000000

#define CONFIG_SYS_PCIE1_IO_PHYS 0xb0000000

#define CONFIG_SYS_PCIE1_IO_SIZE 0x20000000 /* 512M */

#define CONFIG_SYS_SRIO_MEM_VIRT 0x90000000

#define CONFIG_SYS_SRIO_MEM_BUS 0x90000000

#define CONFIG_SYS_SRIO_MEM_PHYS 0x90000000

#ifdef CONFIG_QE

/*

* QE UEC ethernet configuration

*/

#undef CONFIG_SYS_UCC_RGMII_MODE /* MURMU modified from define to undef Set UCC work at RGMII by default */

#define CONFIG_SYS_UCC_RMII_MODE /*MURMU modified from undef to define Set UCC work at RMII mode */

#ifdef CONFIG_MK_RMII

/* Set UCC work at RMII */

#if defined(CONFIG_MK_ATM)

#error "Err: ATM and RMII can't be enabled at the same time!"

#endif

#undef CONFIG_SYS_UCC_RGMII_MODE

#define CONFIG_SYS_UCC_RMII_MODE

//MURMU it is not used for MDS board; to decide whether to use it for our board #define CONFIG_PQ_MDS_PIB

#endif

#define CONFIG_MIIM_ADDRESS (CONFIG_SYS_CCSRBAR + 0x82120)

#define CONFIG_UEC_ETH

#define CONFIG_ETHPRIME "FSL UEC3"

#define CONFIG_PHY_MODE_NEED_CHANGE

#define CONFIG_UEC_ETH3 /* GETH3 */

#define CONFIG_HAS_ETH2

#ifdef CONFIG_UEC_ETH3

#define CONFIG_SYS_UEC3_UCC_NUM 2 /* UCC3 */

#define CONFIG_SYS_UEC3_RX_CLK QE_CLK_NONE

#if defined(CONFIG_SYS_UCC_RGMII_MODE)

#define CONFIG_SYS_UEC3_TX_CLK QE_CLK12

#define CONFIG_SYS_UEC3_ETH_TYPE GIGA_ETH

#define CONFIG_SYS_UEC3_PHY_ADDR 0x1 /* Phy address for RGMII */

#define CONFIG_SYS_UEC3_INTERFACE_MODE ENET_1000_RGMII_ID

#elif defined(CONFIG_SYS_UCC_RMII_MODE)

#define CONFIG_SYS_UEC3_TX_CLK QE_CLK16 /* CLK16 for RMII */

#define CONFIG_SYS_UEC3_ETH_TYPE FAST_ETH

#define CONFIG_SYS_UEC3_PHY_ADDR 0x1 /* Phy Address for RMII */

#define CONFIG_SYS_UEC3_INTERFACE_MODE ENET_100_RMII

#endif /* CONFIG_SYS_UCC_RGMII_MODE */

#endif /* CONFIG_UEC_ETH3 */

#define CONFIG_UEC_ETH4 /* GETH4 */

#define CONFIG_HAS_ETH3

#ifdef CONFIG_UEC_ETH4

#define CONFIG_SYS_UEC4_UCC_NUM 3 /* UCC4 */

#define CONFIG_SYS_UEC4_RX_CLK QE_CLK_NONE

#if defined(CONFIG_SYS_UCC_RGMII_MODE)

#define CONFIG_SYS_UEC4_TX_CLK QE_CLK17

#define CONFIG_SYS_UEC4_ETH_TYPE GIGA_ETH

#define CONFIG_SYS_UEC4_PHY_ADDR 0x2 /* Phy address for RGMII */

#define CONFIG_SYS_UEC4_INTERFACE_MODE ENET_1000_RGMII_ID

#elif defined(CONFIG_SYS_UCC_RMII_MODE)

#define CONFIG_SYS_UEC4_TX_CLK QE_CLK16 /* CLK 16 for RMII */

#define CONFIG_SYS_UEC4_ETH_TYPE FAST_ETH

#define CONFIG_SYS_UEC4_PHY_ADDR 0x2 /* Phy Address for RMII */

#define CONFIG_SYS_UEC4_INTERFACE_MODE ENET_100_RMII

#endif /* CONFIG_SYS_UCC_RGMII_MODE */

#endif /* CONFIG_UEC_ETH4 */

#undef CONFIG_UEC_ETH7 /* GETH7 */

#define CONFIG_HAS_ETH6

#ifdef CONFIG_UEC_ETH7

#define CONFIG_SYS_UEC7_UCC_NUM 6 /* UCC7 */

#define CONFIG_SYS_UEC7_RX_CLK QE_CLK_NONE

#if defined(CONFIG_SYS_UCC_RGMII_MODE)

#define CONFIG_SYS_UEC7_TX_CLK QE_CLK17

#define CONFIG_SYS_UEC7_ETH_TYPE GIGA_ETH

#define CONFIG_SYS_UEC7_PHY_ADDR 0x3 /* Phy Address for RGMII */

#define CONFIG_SYS_UEC7_INTERFACE_MODE ENET_1000_RGMII_ID

#elif defined(CONFIG_SYS_UCC_RMII_MODE)

#define CONFIG_SYS_UEC7_TX_CLK QE_CLK16 /* CLK_16 for RMII */

#define CONFIG_SYS_UEC7_ETH_TYPE FAST_ETH

#define CONFIG_SYS_UEC7_PHY_ADDR 0x3 /* Phy Address for RMII */

#define CONFIG_SYS_UEC7_INTERFACE_MODE ENET_100_RMII

#endif /* CONFIG_SYS_UCC_RGMII_MODE */

#endif /* CONFIG_UEC_ETH7 */

#endif /* CONFIG_QE */

#if defined(CONFIG_PCI)

#define CONFIG_NET_MULTI

#define CONFIG_PCI_PNP /* do pci plug-and-play */

#undef CONFIG_EEPRO100

#undef CONFIG_TULIP

#define CONFIG_PCI_SCAN_SHOW /* show pci devices on startup */

#endif /* CONFIG_PCI */

#ifndef CONFIG_NET_MULTI

#define CONFIG_NET_MULTI 1

#endif

/*

* Environment

*/

#if defined(CONFIG_SYS_RAMBOOT)

#if defined(CONFIG_RAMBOOT_NAND)

#define CONFIG_ENV_IS_IN_NAND 1

#define CONFIG_ENV_SIZE CONFIG_SYS_NAND_BLOCK_SIZE

#define CONFIG_ENV_OFFSET ((512 * 1024) + CONFIG_SYS_NAND_BLOCK_SIZE)

#endif

#else

#define CONFIG_ENV_IS_IN_FLASH 1

#define CONFIG_ENV_ADDR (CONFIG_SYS_MONITOR_BASE - CONFIG_ENV_SECT_SIZE)

#define CONFIG_ENV_SECT_SIZE 0x20000 /* 256K(one sector) for env */

#define CONFIG_ENV_SIZE CONFIG_ENV_SECT_SIZE

#endif

#define CONFIG_LOADS_ECHO 1 /* echo on for serial download */

#define CONFIG_SYS_LOADS_BAUD_CHANGE 1 /* allow baudrate change */

/* QE microcode/firmware address */

#define CONFIG_SYS_QE_FW_ADDR 0xfff00000

/*

* BOOTP options

*/

#define CONFIG_BOOTP_BOOTFILESIZE

#define CONFIG_BOOTP_BOOTPATH

#define CONFIG_BOOTP_GATEWAY

#define CONFIG_BOOTP_HOSTNAME

/*

* Command line configuration.

*/

#include <config_cmd_default.h>

#define CONFIG_CMD_PING

#define CONFIG_CMD_I2C

#define CONFIG_CMD_MII

#define CONFIG_CMD_ELF

#define CONFIG_CMD_IRQ

#define CONFIG_CMD_SETEXPR

#if defined(CONFIG_PCI)

#define CONFIG_CMD_PCI

#endif

#undef CONFIG_WATCHDOG /* watchdog disabled */

#define CONFIG_MMC 1

#ifdef CONFIG_MMC

#define CONFIG_FSL_ESDHC

#define CONFIG_SYS_FSL_ESDHC_ADDR CONFIG_SYS_MPC85xx_ESDHC_ADDR

#define CONFIG_CMD_MMC

#define CONFIG_GENERIC_MMC

#define CONFIG_CMD_EXT2

#define CONFIG_CMD_FAT

#define CONFIG_DOS_PARTITION

#endif

/*

* Miscellaneous configurable options

*/

#define CONFIG_SYS_LONGHELP /* undef to save memory */

#define CONFIG_CMDLINE_EDITING /* Command-line editing */

#define CONFIG_SYS_LOAD_ADDR 0x1000000 /* default load address */

#define CONFIG_SYS_PROMPT "SCM3_MCP=> " /* Monitor Command Prompt *///

#if defined(CONFIG_CMD_KGDB)

#define CONFIG_SYS_CBSIZE 2048 /* Console I/O Buffer Size */

#else

#define CONFIG_SYS_CBSIZE 512 /* Console I/O Buffer Size */

#endif

#define CONFIG_SYS_PBSIZE (CONFIG_SYS_CBSIZE+sizeof(CONFIG_SYS_PROMPT)+16)

/* Print Buffer Size */

#define CONFIG_SYS_MAXARGS 32 /* max number of command args */

#define CONFIG_SYS_BARGSIZE CONFIG_SYS_CBSIZE

/* Boot Argument Buffer Size */

#define CONFIG_SYS_HZ 1000 /* decrementer freq: 1ms ticks */

/*

* For booting Linux, the board info and command line data

* have to be in the first 16 MB of memory, since this is

* the maximum mapped by the Linux kernel during initialization.

*/

#define CONFIG_SYS_BOOTMAPSZ (16 << 20)

/* Initial Memory map for Linux*/

/*

* Internal Definitions

*

* Boot Flags

*/

#define BOOTFLAG_COLD 0x01 /* Normal Power-On: Boot from FLASH */

#define BOOTFLAG_WARM 0x02 /* Software reboot */

#if defined(CONFIG_CMD_KGDB)

#define CONFIG_KGDB_BAUDRATE 230400 /* speed to run kgdb serial port */

#define CONFIG_KGDB_SER_INDEX 2 /* which serial port to use */

#endif

/*

* Environment Configuration

*/

#define CONFIG_HOSTNAME SCM3-MCP

//#define CONFIG_ROOTPATH /nfsroot

#define CONFIG_ROOTPATH /root

#define CONFIG_BOOTFILE uImage

#define CONFIG_SERVERIP 192.168.8.117

#define CONFIG_GATEWAYIP 192.168.8.1

#define CONFIG_NETMASK 255.255.255.0

#define CONFIG_IPADDR 192.168.8.203

#define CONFIG_ETHADDR 76:00:00:98:74:1A

#define CONFIG_ETH1ADDR 76:00:00:98:74:1B

#define CONFIG_ETH2ADDR 76:00:00:98:74:1C

#define CONFIG_ENABLE_ESDHC esdhc //Debdutta

#define CONFIG_LOADADDR 1000000 /*default location for tftp and bootm*/

#define CONFIG_BOOTDELAY 3 /* -1 disables auto-boot */

/* #undef CONFIG_BOOTARGS */ /* the boot command will set bootargs*/

#define CONFIG_BAUDRATE 115200

#define CONFIG_CARD_TYPE cdot_scm_mcp003 /* Type of the card */

#define CONFIG_BOOTARGS "console=ttyS1,115200n8 root=/dev/mtdblock0 rw rootfstype=jffs2 ip=off"

#define CONFIG_EXTRA_ENV_SETTINGS \

"netdev=eth0\0" \

"consoledev=ttyS0\0" \

"ramdiskaddr=600000\0" \

"ramdiskfile=your.ramdisk.u-boot\0" \

"fdtaddr=400000\0" \

"fdtfile=your.fdt.dtb\0" \

"nfsargs=setenv bootargs root=/dev/nfs rw " \

"nfsroot=$serverip:$rootpath " \

"ip=$ipaddr:$serverip:$gatewayip:$netmask:$hostname:$netdev:off " \

"console=$consoledev,$baudrate $othbootargs\0" \

"ramargs=setenv bootargs root=/dev/ram rw " \

"console=$consoledev,$baudrate $othbootargs\0" \

#define CONFIG_NFSBOOTCOMMAND \

"run nfsargs;" \

"tftp $loadaddr $bootfile;" \

"tftp $fdtaddr $fdtfile;" \

"bootm $loadaddr - $fdtaddr"

#define CONFIG_RAMBOOTCOMMAND \

"run ramargs;" \

"tftp $ramdiskaddr $ramdiskfile;" \

"tftp $loadaddr $bootfile;" \

"bootm $loadaddr $ramdiskaddr"

#define CONFIG_BOOTCOMMAND "run bootargs;bootm 0xffce0000 - 0xfff40000"

#endif /* __CONFIG_H */

FILE: board/freescale/mpc8569mds/tlb.c

/*

* Copyright 2009 Freescale Semiconductor, Inc.

*

* (C) Copyright 2000

* Wolfgang Denk, DENX Software Engineering, wd@denx.de.

*

* See file CREDITS for list of people who contributed to this

* project.

*

* This program is free software; you can redistribute it and/or

* modify it under the terms of the GNU General Public License as

* published by the Free Software Foundation; either version 2 of

* the License, or (at your option) any later version.

*

* This program is distributed in the hope that it will be useful,

* but WITHOUT ANY WARRANTY; without even the implied warranty of

* MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the

* GNU General Public License for more details.

*

* You should have received a copy of the GNU General Public License

* along with this program; if not, write to the Free Software

* Foundation, Inc., 59 Temple Place, Suite 330, Boston,

* MA 02111-1307 USA

*/

#include <common.h>

#include <asm/mmu.h>

struct fsl_e_tlb_entry tlb_table[] = {

/* TLB 0 - for temp stack in cache */

SET_TLB_ENTRY(0, CONFIG_SYS_INIT_RAM_ADDR, CONFIG_SYS_INIT_RAM_ADDR,

MAS3_SX|MAS3_SW|MAS3_SR, 0,

0, 0, BOOKE_PAGESZ_4K, 0),

SET_TLB_ENTRY(0, CONFIG_SYS_INIT_RAM_ADDR + 4 * 1024,

CONFIG_SYS_INIT_RAM_ADDR + 4 * 1024,

MAS3_SX|MAS3_SW|MAS3_SR, 0,

0, 0, BOOKE_PAGESZ_4K, 0),

SET_TLB_ENTRY(0, CONFIG_SYS_INIT_RAM_ADDR + 8 * 1024,

CONFIG_SYS_INIT_RAM_ADDR + 8 * 1024,

MAS3_SX|MAS3_SW|MAS3_SR, 0,

0, 0, BOOKE_PAGESZ_4K, 0),

SET_TLB_ENTRY(0, CONFIG_SYS_INIT_RAM_ADDR + 12 * 1024,

CONFIG_SYS_INIT_RAM_ADDR + 12 * 1024,

MAS3_SX|MAS3_SW|MAS3_SR, 0,

0, 0, BOOKE_PAGESZ_4K, 0),

/* TLB 1 Initializations */

/*

* TLBe 0: 256M Non-cacheable, guarded

* 0xff000000 256M FLASH (lower half)

*

*/

// SET_TLB_ENTRY(1, CONFIG_SYS_FLASH_BASE, CONFIG_SYS_FLASH_BASE,

// MAS3_SX|MAS3_SW|MAS3_SR, MAS2_I|MAS2_G,

// 0, 0, BOOKE_PAGESZ_256M, 1),

/*

* TLBe 1: 256M Non-cacheable, guarded

* 0xff000000 256M FLASH (upper half)

* Out of reset this entry is only 4K.

*/

SET_TLB_ENTRY(1, CONFIG_SYS_FLASH_BASE, CONFIG_SYS_FLASH_BASE,

MAS3_SX|MAS3_SW|MAS3_SR, MAS2_I|MAS2_G,

0, 0, BOOKE_PAGESZ_256M, 1),

/*

* TLBe 2: 256M Non-cacheable, guarded

* 0xa00000000 256M PCIe MEM (lower half)

*/

SET_TLB_ENTRY(1, CONFIG_SYS_PCIE1_MEM_VIRT, CONFIG_SYS_PCIE1_MEM_PHYS,

MAS3_SX|MAS3_SW|MAS3_SR, MAS2_I|MAS2_G,

0, 2, BOOKE_PAGESZ_256M, 1),

/*

* TLBe 3: 256M Non-cacheable, guarded

* 0xb00000000 256M PCIe MEM (higher half)

*/

SET_TLB_ENTRY(1, (CONFIG_SYS_PCIE1_MEM_VIRT + 0x10000000),

(CONFIG_SYS_PCIE1_MEM_PHYS + 0x10000000),

MAS3_SX|MAS3_SW|MAS3_SR, MAS2_I|MAS2_G,

0, 3, BOOKE_PAGESZ_256M, 1),

/*

* TLBe 4: 64M Non-cacheable, guarded

* 0xe000_0000 1M CCSRBAR

* 0xe280_0000 8M PCIe IO

*/

SET_TLB_ENTRY(1, CONFIG_SYS_CCSRBAR, CONFIG_SYS_CCSRBAR_PHYS,

MAS3_SX|MAS3_SW|MAS3_SR, MAS2_I|MAS2_G,

0, 4, BOOKE_PAGESZ_64M, 1),

#if defined(CONFIG_SYS_RAMBOOT) && defined(CONFIG_SYS_INIT_L2_ADDR)

/* *I*G - L2SRAM */

SET_TLB_ENTRY(1, CONFIG_SYS_INIT_L2_ADDR, CONFIG_SYS_INIT_L2_ADDR_PHYS,

MAS3_SX|MAS3_SW|MAS3_SR, MAS2_I|MAS2_G,

0, 5, BOOKE_PAGESZ_256K, 1),

SET_TLB_ENTRY(1, CONFIG_SYS_INIT_L2_ADDR + 0x40000,

CONFIG_SYS_INIT_L2_ADDR_PHYS + 0x40000,

MAS3_SX|MAS3_SW|MAS3_SR, MAS2_I|MAS2_G,

0, 6, BOOKE_PAGESZ_256K, 1),

#endif

};

int num_tlb_entries = ARRAY_SIZE(tlb_table);

SECOND CONFIGURATION

File: include/configs/MPC8569MDS.h

/*

* Copyright (C) 2009-2010 Freescale Semiconductor, Inc.

*

* See file CREDITS for list of people who contributed to this

* project.

*

* This program is free software; you can redistribute it and/or

* modify it under the terms of the GNU General Public License as

* published by the Free Software Foundation; either version 2 of

* the License, or (at your option) any later version.

*

* This program is distributed in the hope that it will be useful,

* but WITHOUT ANY WARRANTY; without even the implied warranty of

* MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the

* GNU General Public License for more details.

*

* You should have received a copy of the GNU General Public License

* along with this program; if not, write to the Free Software

* Foundation, Inc., 59 Temple Place, Suite 330, Boston,

* MA 02111-1307 USA

*/

/*

* mpc8569mds board configuration file

*/

#ifndef __CONFIG_H

#define __CONFIG_H

/* High Level Configuration Options */

#define CONFIG_BOOKE 1 /* BOOKE */

#define CONFIG_E500 1 /* BOOKE e500 family */

#define CONFIG_MPC85xx 1 /* MPC8540/60/55/41/48/68 */

#define CONFIG_MPC8569 1 /* MPC8569 specific */

#define CONFIG_MPC8569MDS 1 /* MPC8569MDS board specific */

/*

#define CONFIG_POST 1

#define CONFIG_SYS_POST_MEMORY 1

*/

#define CONFIG_FSL_ELBC 1 /* Has Enhance localbus controller */

#define CONFIG_PCI 1 /* Disable PCI/PCIE */

#define CONFIG_PCIE1 1 /* PCIE controller */

#define CONFIG_FSL_PCI_INIT 1 /* use common fsl pci init code */

#define CONFIG_FSL_PCIE_RESET 1 /* need PCIe reset errata */

#define CONFIG_SYS_PCI_64BIT 1 /* enable 64-bit PCI resources */

#define CONFIG_QE /* Enable QE */

#define CONFIG_ENV_OVERWRITE

#define CONFIG_FSL_LAW 1 /* Use common FSL init code */

#ifndef __ASSEMBLY__

extern unsigned long get_clock_freq(void);

#endif

/* Replace a call to get_clock_freq (after it is implemented)*/

#define CONFIG_SYS_CLK_FREQ 66666666

#define CONFIG_DDR_CLK_FREQ CONFIG_SYS_CLK_FREQ

/*#define CONFIG_DDR_CLK_FREQ 40000000 */

/*MURMU

#define CONFIG_PQ_MDS_PIB

*/

#ifdef CONFIG_MK_ATM

#define CONFIG_PQ_MDS_PIB

#define CONFIG_PQ_MDS_PIB_ATM

#endif

#ifdef CONFIG_MK_NAND

#define CONFIG_NAND_U_BOOT 1

#define CONFIG_RAMBOOT_NAND 1

#define CONFIG_RAMBOOT_TEXT_BASE 0xf8f82000

#endif

#ifdef CONFIG_MK_DDR2

#define CONFIG_FSL_DDR2

#endif

/* MT8JSF12864HY */

#ifdef CONFIG_MK_DDR3HY

#if defined(CONFIG_MK_DDR2)

#error "Err: enabled two kinds of DDR!"

#endif

#define CONFIG_FSL_DDR3

#define CONFIG_FSL_DDR3_RTT_WR 2

#endif

/* MT8JSF12864HZ */

#ifdef CONFIG_MK_DDR3HZ

#if defined(CONFIG_MK_DDR2) || defined(CONFIG_MK_DDR3HY)

#error "Err: enabled two/three kinds of DDR!"

#endif

#define CONFIG_FSL_DDR3

#define CONFIG_FSL_DDR3_RTT_WR 0

#endif

#if !defined(CONFIG_MK_DDR2) && !defined(CONFIG_MK_DDR3HY) && \

!defined(CONFIG_MK_DDR3HZ)

#error "Err: none of DDR is specified!"

#error " Must specify one kind of DDR(DDR2, DDR3HZ or DDR3HY)"

#endif

/*

* These can be toggled for performance analysis, otherwise use default.

*/

#define CONFIG_L2_CACHE /* toggle L2 cache */

#define CONFIG_BTB /* toggle branch predition */

/*

* Only possible on E500 Version 2 or newer cores.

*/

#define CONFIG_ENABLE_36BIT_PHYS

#define CONFIG_BOARD_EARLY_INIT_F /* Call board_pre_init */

#define CONFIG_MISC_INIT_R /* call misc_init_r() */

#define CONFIG_HWCONFIG

#define CONFIG_SYS_MEMTEST_START 0x00200000 /* memtest works on */

#define CONFIG_SYS_MEMTEST_END 0x00400000

/*

* Config the L2 Cache as L2 SRAM

*/

#define CONFIG_SYS_INIT_L2_ADDR 0xf8f80000

#define CONFIG_SYS_INIT_L2_ADDR_PHYS CONFIG_SYS_INIT_L2_ADDR

#define CONFIG_SYS_L2_SIZE (512 << 10)

#define CONFIG_SYS_INIT_L2_END (CONFIG_SYS_INIT_L2_ADDR + CONFIG_SYS_L2_SIZE)

/*

* Base addresses -- Note these are effective addresses where the

* actual resources get mapped (not physical addresses)

*/

#define CONFIG_SYS_CCSRBAR 0xD0000000 /* relocated CCSRBAR */ // See board/freescale/mpc8569mds/law.c for memory map

#define CONFIG_SYS_CCSRBAR_PHYS CONFIG_SYS_CCSRBAR

/* physical addr of CCSRBAR */

#define CONFIG_SYS_IMMR CONFIG_SYS_CCSRBAR

/* PQII uses CONFIG_SYS_IMMR */

#if defined(CONFIG_RAMBOOT_NAND) && !defined(CONFIG_NAND_SPL)

#define CONFIG_SYS_CCSRBAR_DEFAULT CONFIG_SYS_CCSRBAR

#else

#define CONFIG_SYS_CCSRBAR_DEFAULT 0xff700000 /*CCSRBAR Default */

#endif

#define CONFIG_SYS_PCI1_ADDR (CONFIG_SYS_CCSRBAR+0x8000)

#define CONFIG_SYS_PCIE1_ADDR (CONFIG_SYS_CCSRBAR+0xa000)

/* DDR Setup */

#undef CONFIG_FSL_DDR_INTERACTIVE

#define CONFIG_SPD_EEPROM /* Use SPD EEPROM for DDR setup*/ /* Not using SPD EEPROM MURMU*/

#define CONFIG_DDR_SPD

#define CONFIG_DDR_DLL /* possible DLL fix needed */

#define CONFIG_ECC_INIT_VIA_DDRCONTROLLER /* DDR controller or DMA? */