- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- Product Forums

- :

- PowerQUICC Processors

- :

- MPC8260a 60x SDRAM external address multiplixer in 60x-compatible mode?

MPC8260a 60x SDRAM external address multiplixer in 60x-compatible mode?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

MPC8260a 60x SDRAM external address multiplixer in 60x-compatible mode?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,everyone, I use MPC8260A in my design, now I encounter some problems when debugging. When I access SDRAM in CodeWarrior unsing USB-TAP, an error message "writemem on target failed at address 0x400, size 0x1000". But when I only access 0x100 bytes, it's ok. I measure signal waveform using DPO, the timing is correct.

Sometimes I refresh data in codewarrior, the memory data will change. It seems the refresh timing is wrong.

MPC8260 is in 60x-compatible mode,66Mhz bus clock . 60x SDRAM is configured 32bit-port ,128MB(13 rows, 10cols,4 bank, 512Mb density), page-based mode. So 60x SDRAM address is latched and muxed externally. Please help me to check the address connection?

BR: MS = 60x SDRAM, Port size = 32bit

OR: BPD = 01(4 bank), row start = A5, row number = 13

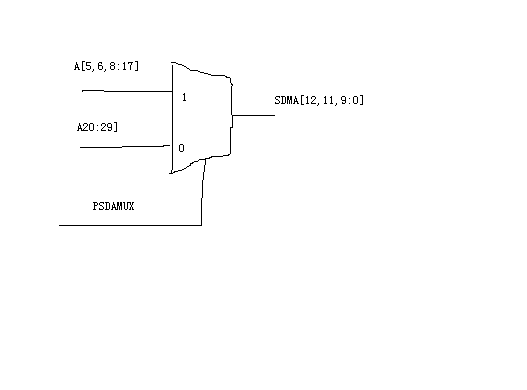

PSDMR:PBI = 1, SDAM = 100, BSAM = 010(A14-A16)

SDRAM BA[1:0] using dedicated pin BNKSEL[1:2].

row bank-sel col

A[5:17], A[18:19], A[20:29]

SDRAM pins: BA1 BA0 A12 A11 A10 A9----A0

Phsical : A15 A16 A17 A18 A19 A20---A29

ACT : BNKSEL1 BNKSEL2 A5 A6 SDA10 A9--- A17

R/W : BNKSEL1 BNKSEL2 -- -- AP A20--A29

60x address is muxed (using IDTQS3257):

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You mentioned just a few fields of the PSDMR, can you let me know full PSDMR value?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

PSDMR:PBI = 1, SDAM = 100, BSAM = 010(A14-A16), SDA10 = 011(A7), RFRC = 6 cycle, PRETOACT = 3, ACTTORW = 2 , BL = 1(8 bytes), LDOTOPRE = -2, WRC = 2, EAMUX = 1, BUFCMD = 1, CAL = 10(2), .

The command bit changes with command being issued, After issuing LOAD MODE REGISTER command, RFEN bit is set.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Try to set PSDMR[LDOTOPRE] = -1, instead of -2.

And let me know whether this helps.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have set PSDMR[LDOTOPRE] = -1,

I found the problem, the PSDMR[CL] field is not the same as value written by LOAD MODE REGISTER command, because in 60x-compatible mode , the LOAD MODE REGISTER value must be calaulted by user software. The software can run in SDRAM.

But I have a new problem when using USB_TAP. Now when I access SDRAM 0x200@0x0 size using Codewarrior Debug-> EPPC -> fill memory, then View memory, only the first 0x100 bytes space is filled and the beginning address(0x0-0x5) is not written, and the second 0x100 byte is not filled.

But when I fill memory every 0x100 bytes, all data is written and ok.

If the SDRAM is still is not configured properly. the software can't run from SDRAM. I dont know why.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Can you check and provide a piece of initialization code where LOAD MODE REGISTER command is issued to the SDRAM?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

And one more problem.

SMC is configured in UART, I use the Demo Board SMC initilization code, but the SMC TXD pin outputs nothing. I turn LED after the SMC configuration, then I view register in Codewarrior,

the I/O port is configured right, but register CPCR / BRGC1/ SMC1MR is all zero(not the right value),

I want to know if the SDRAM is not working properly, SMC initilization may be affected?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I do not think that non-functional SDRAM can affect initialization of the SMC. However this can be code dependent, try to use a debugger to trace if SMC registers are really set during initilaization.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Now I chose the MPC8260A(266/166/66Mhz), the CPM can run up to 166Mhz.

After I only change the CPM frequency from 166Mhz to 133Mhz by configuration word and MODCK[1:3] , the SMC works and ouputs properly.

I dont know why?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The following is my initilization code using C code. I port the code from one Demo , and work properly. The only difference : Demo(64 bit port) in single-CPU mode ,but my board in 60x-compatible mode.

*ramaddr = 0x00000000;

M8260_PSRT(immrVal) = 0xB;

M8260_BR1(immrVal) = 0x00001841;

M8260_OR1(immrVal) = 0xF8002Bb00;

M8260_PSDMR(immrVal) = 0xAC4E277F; // Prechage

*ramaddr = 0xFF;

M8260_PSDMR(immrVal) = 0x8C4E277F;// CBR

for(i = 0, i<8;i++)

*ramaddr = 0xFF;

M8260_PSDMR(immrVal) = 0x9C4E277F;

*(ramaddr + 0xCC) = 0xFF;

M8260_PSDMR(immrVal) = 0xC44E277f;

*ramaddr = 0xFF;

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Can you check if line

M8260_OR1(immrVal) = 0xF8002Bb00;

is exact copy from the code?

And one more question about address connection to the SDRAM. Do you have address latch prior to address multiplexer?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes, copy the code from Demo, but because the SDRAM port is not same, so OR1 is not totally same as Demo,

I have address latch(16373) prior to address multiplexer.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

If (M8260_OR1(immrVal) = 0xF8002Bb00) is really used in the code, it can cause a problem. Value 0xF8002Bb00 (that is 0xF_8002_Bb00) seems to be mistaken, it contains 36 bits instead of 32 ones, so 4 upper bits are lost. Try to check its bit pattern against description in the Manaul.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you!

I check the code once again.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes, I will try it.

Thanks!