- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Increasing internal LDO voltage causes ARM to hang

Increasing internal LDO voltage causes ARM to hang

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Champs,

My customer using i.MX6DL is having trouble of supplying ARM core voltage through internal LDO.

They tried a following power scenario.

1. LDO 1.150V

・ CPU=396MHz, PMIC-ARMCORE(SW1A/B)=1.3V

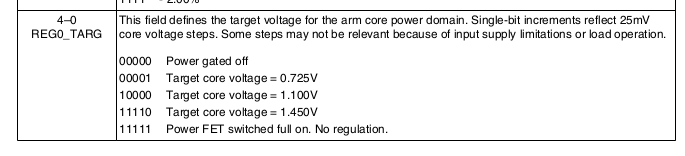

・ PMU_REG_CORE-REG0_TARG4–0)= 10010(1.150V, LDO Enable )

2. LDO Bypass

・ CPU=396MHz, PMIC-ARMCORE(SW1A/B)=1.3V

・ PMU_REG_CORE-REG0_TARG(4–0)= 11111(-V, LDO Bypass )

3. LDO 1.450V

・ CPU=396MHz, PMIC-ARMCORE(SW1A/B)=1.3V

・ PMU_REG_CORE-REG0_TARG(4–0)= 11110(1.450V, LDO Enable )

In this scenario, ARM hangs when setting #3.

However when they add a following intermediate power mode between the #2 and #3,

2.1. LDO 1.425V

・ CPU=396MHz, PMIC-ARMCORE(SW1A/B)=1.3V

・ PMU_REG_CORE-REG0_TARG(4–0)= 11100(1.425V, LDO Enable )

ARM goes fine from #1, #2, #2,1 to #3.

Is there any time or some other restriction to increase voltage?

Best regards,

Nori Shinozaki

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Nori

Table 7 "Absolute Maximum Ratings" IMX6SDLCEC

defines max. 1.3V for VDD_ARM_CAP,

it can not be 1.425V.

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Nori

Table 7 "Absolute Maximum Ratings" IMX6SDLCEC

defines max. 1.3V for VDD_ARM_CAP,

it can not be 1.425V.

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Igor,

Thanks, I simply thought 1.450V is Ok since it's listed in the RM...

Let me confirm on the value 11110 (0x1E).

In the Errata ERR005852 "Analog: Transition from Deep Sleep Mode to LDO Bypass Mode may

cause the slow response of the VDDARM_CAP output".

The workaround is "The software workaround to prevent this issue it to switch to analog bypass mode (0x1E), prior to

entering DSM, and then, revert to the normal bypass mode, when exiting from DSM"

Does this mean that 11110(0x1E) is a special value which turns digital LDO into "analog bypass mode"?

Best regards,

Nori Shinozaki