- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- KE02Z SPI Slave (strange behavior)

KE02Z SPI Slave (strange behavior)

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

KE02Z SPI Slave (strange behavior)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello

I'm trying to figure out how SPI Slave (FRDM-KE02Z) works. Two boards are connected only by GND and CLK (Slave is FRDM-KE02Z and Master is MCU board(not Freescale)) .

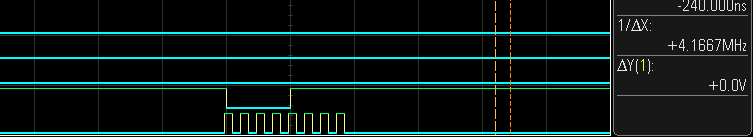

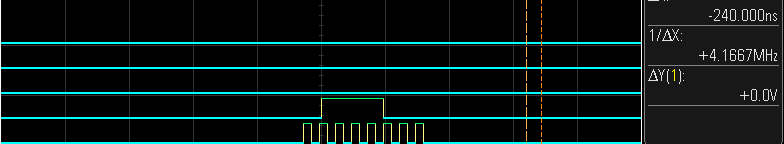

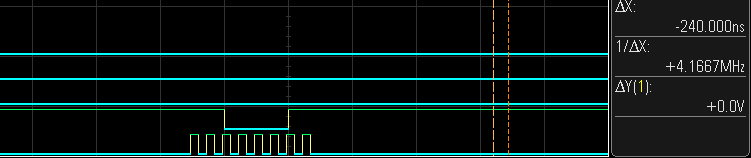

Master sent only CLK to Slave. Slave is configured: Clock polarity: Low, Clock phase: Change on leading edge. Immediately after power-up, Slave work correctly, it sends out data accurately by master clock, bit by bit on clock period. But when I reset Master board, data is shifted relative to clock, as on on figures below. Could somebody enplane me , how to get rid of shifting

Normal

Shifted

there is my code:

#include "Cpu.h"

#include "Events.h"

#include "SS1.h"

#include "PE_Types.h"

#include "PE_Error.h"

#include "PE_Const.h"

#include "IO_Map.h"

#define BLOCK_SIZE 1

uint8_t OutData[BLOCK_SIZE];

uint8_t InpData[BLOCK_SIZE];

volatile LDD_SPISLAVE_TError ComError = 0U;

LDD_TError Error;

LDD_TDeviceData *MySPIPtr;

int main(void)

{

PE_low_level_init();

MySPIPtr = SS1_Init(NULL);

while(1){

//Error = SS1_ReceiveBlock(MySPIPtr, InpData, BLOCK_SIZE);

OutData[0]=15;

Error = SS1_SendBlock(MySPIPtr, OutData, BLOCK_SIZE); /* Start transmission/reception */

while (!SS1_GetBlockSentStatus(MySPIPtr)) { /* Wait until data block is transmitted/received */

SS1_Main(MySPIPtr);

}

//SS1_Disable(NULL);

//SS1_Enable(NULL);

}

#ifdef PEX_RTOS_START

PEX_RTOS_START(); /* Startup of the selected RTOS. Macro is defined by the RTOS component. */

#endif

for(;;){}

}

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I think this happens because while the clock signal shifts the data in the shift register, I do reset the clock signal, but the data not shifted until end, and when clock signal comes again to shift register, it begin shifts the data from last point. How i can clean shift register in such case?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

If you reset the SPI (try power off/power on the module) you can probably reset the internal buffers/registers.

Regards

Mark

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Mark

I can't try power off/on because the central idea of my project is frequent sensor checking. There is a sensor which has an interface similar to the shift register:clock input pin, data output pin. but it's not that simple, it has CS pin. My idea was use KE02Z between some Master device and the sensor, because Master device doesn't has CS signal, KE02Z SPI must determine there is clock signal from Master device to sensor or not, and if it there is, send CS signal to the sensor by MISO. I connected clock signal output from Master device to sensor and KE02Z clock input. CS pin of sensor to KE02Z MISO, and when Master device send 18 clock periods I'd like that KE02Z starts MISO transmission to sensor CS pin on first clock period and ends on last clock period.

Sorry for complex description.:smileysilly:

It may be better to solve this problem on timers, timer counts 18 clock periods and send CS signal via GPIO. How to do that it would work as quickly as possible?? Clock frequence is 4Mhz

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Cit Ram:

Mark suggested to power off/on *only* the SPI module, not the whole MCU. I have not tried this but in your case using Processor Expert you may test the Disable() and Enable() methods, which use the SPIx_C1[SPE] bit to activate/deactivate SPI.

Regarding using a timer to count periods, you can use a TimerUnit_LDD PEx component and select FTM as counter, then use it in Input Capture mode by setting "Input Clock Source" as External.

Hope this helps!

Jorge_Gonzalez

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for your answer Jorge

I made as you wrote. But I have question, if input clock signal is 4MHz, timer not too slow for this work?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

According to datasheet, if you operate at maximum 20 MHz bus clock, then the input pulse frequency can be up to 6.6 MHz (assuming symmetrical duty cycle). Hence 4 MHz should be fine.

Regards!

Jorge_Gonzalez

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for your answer Jorge.

I think Timer won't help me, because clock signal can be stopped on any clock period. If my project to describe in simple words. I need to make a clock signal detector. If there is a clock signal, CS(or any other pin) must be = 0. If no clock signal, CS(or any other pin) = 1. Could you advise me something.