- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- CodeWarrior

- :

- CodeWarrior for QorIQ

- :

- The address problem about p2020rdb in Codewarrior

The address problem about p2020rdb in Codewarrior

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello there,

I an designing a product using p2020cpu refering to the design of p2020rdb-pc. I have 4GB DDR, 32MB Nor Flash. My memory map:

0x0_0000_0000 0x0_ffff_ffff DDR

0x1_e000_0000 0x1_e00f_ffff CCSRBAR

0xf_fe00_0000 0xf_ffff_ffff NOR (0xf_eff8_0000 uboot)

I have modify the base address of nor in LAW to 0xFFE000000,and the NOR configuration in MMU.

Now I found the following codes in p2020rdb_pc_init_rom.tcl.

# L2SRBAR0

# bit 0-17 = BASE addr: 0xFFFC0000

mem [CCSR 0x20100] = 0xFFFC0000

1)Why the L2SRBAR0 base address at 0xfffc0000 in p2020rdb-pc? Should I modify the address in my board?

# Set interrupt vectors in SRAM

# IVPR

reg ${SPR_GROUP}IVPR = 0xFFFF0000

# debug - (a valid instruction should exist to be fetched)

reg ${SPR_GROUP}IVOR15 = 0x0000F000

# program

reg ${SPR_GROUP}IVOR6 = 0x0000F700

# Put a valid opcode at debug and program exception vector addresses

mem v:0xFFFFF000 = 0x48000000

mem v:0xFFFFF700 = 0x48000000

Need I modify the code above?

Best regards,

Min Zhao

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

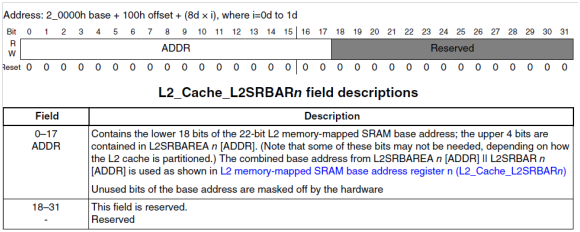

# bit 0-17 = BASE addr: 0xFFFC0000

mem [CCSR 0x20100] = 0xFFFC0000

# L2SRBAREA0

# bit 28-31 = EXTENTED BASE addr: 0x0000000f

mem [CCSR 0x20104] = 0x0000000f

Have a great day,

Yiping Wang

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

This initialization file is used in ROM version project debugging(for example debug program running on NOR Flash).

After reset, e500 cores need to run before being able to enter debug mode.

Work-around: set a HW BP at reset address and run the core; after the core hits the BP, it enters debug mode

e500 cores need to have valid opcode at the interrupt vector, so temporarily use SRAM for this purpose.

In this initialization file, internal SRAM is configured at highest memory address to cover the default 4k MMU page.

# L2CTL

# bit 0 = 0 - L2E: L2 SRAM disabled

# bit 1 = 0 - L2I: L2 invalidate

# bit 2-3 = 10 - L2SIZ: = 512K

# bit 13-15 = 010 - L2SRAM: One half is SRAM (256K)

mem [CCSR 0x20000] = 0x60020000

# L2SRBAR0

# bit 0-17 = BASE addr: 0xFFFC0000

mem [CCSR 0x20100] = 0xFFFC0000

# L2SRBAREA0

# bit 28-31 = EXTENTED BASE addr: 0x00000000

mem [CCSR 0x20104] = 0x00000000

Please refer to the following register definition.

No need to change these debug related configurations, actually I don't think this initialization file is suitable for your current task(board bringing up).

Have a great day,

Yiping Wang

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I can't find where should I modify in the rom.tcl file.

Best regards,

Min Zhao

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

# L2SRBAREA0

# bit 28-31 = EXTENTED BASE addr: 0x00000000

mem [CCSR 0x20104] = 0x00000000

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Do you mean my base address is not 0x00000000? What's my 22-bit L2 memory-mapped SRAM base address?

Best regards,

Min Zhao

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

# bit 0-17 = BASE addr: 0xFFFC0000

mem [CCSR 0x20100] = 0xFFFC0000

# L2SRBAREA0

# bit 28-31 = EXTENTED BASE addr: 0x0000000f

mem [CCSR 0x20104] = 0x0000000f

Have a great day,

Yiping Wang

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------