- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Ethernet PHY power control on MCIMX6SLEVK board

Ethernet PHY power control on MCIMX6SLEVK board

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Ethernet PHY power control on MCIMX6SLEVK board

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

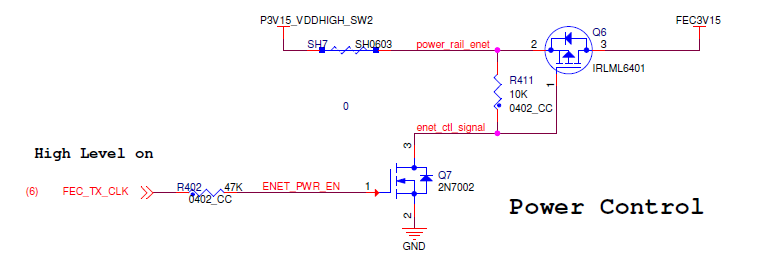

In the MCIMX6SLEVK board kit, there are an ethernet phy power control circuit using mosfet(Q6 and Q7). Which are controlled by a GPIO (FEC_TX_CLK).

I am some query regarding this.

1. Why we are controlling that circuit using GPIO.

2.What are the need of that GPIO control.

3. can we give direct power to the ethernet phy circuit.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sonu

ethernet phy consumes quite lot power so

it is convenient to switch off its power (for example in low power

modes), when not using. GPIO is most simple way to switch it.

Yes, one can give direct power to the ethernet phy circuit.

Best regards

chip

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Chip,

Thanks for your reply. When we are using this same switch circuit for ethernet phy power control, our console is hanging sometime at particular point. Here is the console log where it gets hang

U-Boot 2009.08 (May 03 2014 - 16:29:08)

CPU: Freescale i.MX6 family TO0.0 at 792 MHz

Thermal sensor with ratio = 170

Temperature: 35 C, calibration data 0x5cb5545f

mx6q pll1: 792MHz

mx6q pll2: 528MHz

mx6q pll3: 480MHz

mx6q pll8: 50MHz

ipg clock : 66000000Hz

ipg per clock : 66000000Hz

uart clock : 80000000Hz

cspi clock : 60000000Hz

ahb clock : 132000000Hz

axi clock : 198000000Hz

emi_slow clock: 99000000Hz

ddr clock : 396000000Hz

usdhc1 clock : 198000000Hz

usdhc2 clock : 198000000Hz

usdhc3 clock : 198000000Hz

usdhc4 clock : 198000000Hz

Board: MX6SoloLite-EVK:[ POR ]

Boot Device: SPI NOR

I2C: ready

DRAM: 256 MB

pinki JEDEC ID: 0x20:0xba:0x18

after querey

SF: Detected M25P32 - 16MB with block size 65536, block count 256, total 16777216 bytes

spi_nor_flash_read: from 0x000c0000, len 8192

*** Warning - bad CRC, using default environment

In: serial

Out: serial

Err: serial

i2c: I2C2 SDA is low, start i2c recovery...

I2C2 Recovery success

Found PFUZE100! deviceid=10,revid=11

Net: got MAC address from IIM: 00:00:00:00:00:00

But when we are by passing this switch circuit it is working fine. There is no console hang issue when switch is by passed and power is given directly to ethernet phy.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sonu

I think hanging does not direactly relates

to ethernet phy power control, probably it is caused

by common board power design (power spikes or glitches) or DDR errors.

I would suggest first try DDR tests

https://community.freescale.com/message/331721#331721

https://community.freescale.com/docs/DOC-96412

And then run SDK ethernet tests

i.MX 6Series Platform SDK  : Bare-metal SDK

: Bare-metal SDK

Best regards

chip