- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- Other NXP Products

- :

- MPC5125 LocalPlus Bus Question

MPC5125 LocalPlus Bus Question

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi All,

I have a project that access several devices on the LocalPlus bus and I'm having a problem accessing addresses where the extended address bits (AX3 - AX0) are set to a one. When I try (under CodeWarrior debugger control) the code crashes by making an opcode fetch from some invalid address. I'm sure that I've missed some step in setting up the LocalPlus bus, I'm just not seeing it. I'm hoping a quick comment from someone who's used this processor can shorten my discovery time ![]() ..

..

Read/Write OK (CS[0] Access Window)

0x1000_0000 to 0x10FF_FFFF (16MB)

Read / Write Causes Crash (CS[0] Access Window)

0x1100_0000

Ideas, thoughts, suggestions?

Thanks,

Tim

DDR Memory is all from:

0x0000_0000 to 0x0FFF_FFFF (256MB)

LPC Setup:

Access Windows LPBAW and LPCS0AW set for 0x1000_0000 to 0x1FFF_FFFF (256 MB):

REGIO_RegWriteWord(0x00000020, 0x10001FFF, gcNO); //LPBAW - LocalPlus Boot Access Window = 0x1000_0000 - 0x1FFF_FFFF (256MB)

REGIO_RegWriteWord(0x00000024, 0x10001FFF, gcNO); //LPCS0AW - LocalPlus CS0 Access Window=0x1100_0000 - 0x11FF_FFFF (256MB)

//Bits(31-16) - START_ADR Value specified is appended with 0x0000

//Bits(15-00) - STOP_ADR Value specified is appended with 0xFFFF

LPC_CS0BOOTC - Chip select 0 configuration register set for 8 bit access with Read and Write waitstates

REGIO_RegWriteWord(0x00010000, 0x02021010, gcNO); //LPC_CS0BOOTC - Chip select 0 configuration register

//b[31] 0000:0010:0000:0010 0001:0000:0001:0000 b[0]

//Bits(31-24) - WaitP, Wait states to insert (see bits 4,5)

//Bits(23-16) - WaitX, Base number of wait states to insert(see bits 4,5)

//Bit(15) - MX, Muxed or nonmuxed bus transactions (*0=non-muxed, 1=muxed)

//Bit(14) - ALEV, ALE level (*0=ALE is active low, 1=active high)

//Bit(13) - AA, ACK input active (*0=ACK input is not active, 1=active)

//Bit(12) - CE, Individual CS enable bit (0=External CS is disabled, *1=enabled)

//Bits(11-10) - ALEN, ALE length

// *00=ALE width is 1 LPC clock

// 01=ALE width is 2 LPC clocks

// 10=ALE width is 3 LPC clocks

// 11=ALE width is 4 LPC clocks

//Bits(9-8) - DS, Data size field (device databus size in bytes)

// *00=1 byte (8 bits)

// 01=2 bytes (16 bits)

// 10=reserved

// 11=4 bytes (32 bits)

//Bit(7) - BM, Burst mode (*0=synchronous bust mode, 1=async bust mode)

//Bit(6) - ADDRM, Address mode (*0=byte addressing(always used on 8 bit bus), 1=word addressing)

//Bits(5-4) - WTyp, Wait state type (how the WaitP and WaitX values are applied)

// 00=WaitX is applied to read & write cycles (waitP is ignored)

// *01=WaitX is applied to read cycles, WaitP is applied to write cycles

// 10=WaitX is applied to reads, WaitP/WaitX (16 bit value) is applied to writes

// 11=WaitP/WaitX (16 bit value) is applied to reads and writes

//Bit(3) - WS, Write swap bit (*0=no swapping, 1=endian byte swapping can occur)

//Bit(2) - RS, Read swap bit (*0=no swapping, 1=endian byte swapping can occur)

//Bit(1) - WO, Write only bit (*0=device is not write only, 1=device is write only)

//Bit(0) - RO, Read only bit (*0=device is not read only, 1=device is read only)

Enable the Global Output Control Bit

REGIO_RegWriteByte(0x0000A001, 0x01, gcNO); //IO_CTL_GBOBE Global Output Enable Control Register, set GB_OBE bit(0)

//This enables all output pins set to use FunctMUX[00] this includes OE, RW and CS0

Enable the Master Chip Select bit

REGIO_RegWriteWord(0x00010020, 0x01000000, gcNO); //LPC_CSC - Chip Select Control Register, Set Master Enable(ME) bit(24)

//Bits(31-28) - Unused

//Bit(27) - IE, Interrupt enable bit(*0=no, 1=yes)

//Bits(26-25) - Unused

//Bit(24) - ME, Master Enable Bit (0=register access can occur but no extern transactions, *1=extern CS active)

//Bits(23-0) - Unused

Configure the pins that support the LocalPlus Bus for their required operations (All Function[0], fast slew rate, no pull up/down, etc.)

REGIO_RegWriteByte(0x0000A009, 0x03, gcNO); //STD_PU LPC_AX03 REGIO_RegWriteByte(0x0000A00A, 0x03, gcNO); //STD_PU LPC_AX02

REGIO_RegWriteByte(0x0000A00B, 0x03, gcNO); //STD_PU LPC_AX01

REGIO_RegWriteByte(0x0000A00C, 0x03, gcNO); //STD_PU LPC_AX00

// :

//Same for all other LPC Bus pins (OE, RW, CS0, AD0-AD29)

// :

//STD_PU Register Layout Page(20-8)

//Set bits(7-0) [BIT_7] 0000_0011 [BIT_0] to enable:

//Bit(7) - Unused

//Bits(6-5) - FUNCMUX Choose pin alt function

// 00=AltFunction 1

// 01=AltFunction 2

// 10=AltFunction 3

// 11=AltFunction 4

//Bit(4) - PUD Pull up/down direction (*0=pull down enbld, 1=pull up enbld)

//Bit(3) - PUE Enable pull up/down resistors (*0=no, 1=yes)

//Bit(2) - ST Schmitt trigger enable (*0=disabled, 1=enabled) *STD_PU_ST only*

//Bits(1-0) - DS Drive slew rate

// 00=Slew Rate Config 0 (140nS)

// 01=Slew Rate Config 1 (19nS)

// 10=Slew Rate Config 2 (9.8nS)

// 11=Slew Rate Config 3 (1.4nS)*

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi TIm,

I had the same problem with MPC5125 LPC external bus access. You have to enable the new memory region in the MMU, during MQX initialization.

This is done in the MQX bsp of MPC5125, in the source file init_bsp.c. In _bsp_enable_card(), you can see _mmu_add_region() is used to add memory regions. To add a memory region you can use this function.

Example: To add region from 0x9000_0000 of size 0x1000_0000

_mmu_add_region((unsigned char *)0x90000000, 0x10000000,

E300CORE_MMU_SET_DBAT | E300CORE_MMU_CACHE_INHIBIT | E300CORE_MMU_CACHE_WRITE_THRU | E300CORE_MMU_CACHE_GUARDED | E300CORE_MMU_CACHE_COHERENT);

There number of regions is limited to 8 (8 DBAT and 8 IBAT) and the max size of region is 0x10000000

Hope this helps

- Visakhan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi All,

it's been suggested that I look at the MMU settings as a possible reason that I'm unable to read these addresses. MQX guidance on this looks pretty thin, does anyone have any experience in this area? Are we talking about configuring registers in the MPC-5125 (can't find any reference to MMU registers in the manual) or are we talking about configuring MQX to enable access to these memory areas? Is there any way to query MQX and determine which memory areas are currently enabled? Thanks!

Best,

Tim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi TIm,

I had the same problem with MPC5125 LPC external bus access. You have to enable the new memory region in the MMU, during MQX initialization.

This is done in the MQX bsp of MPC5125, in the source file init_bsp.c. In _bsp_enable_card(), you can see _mmu_add_region() is used to add memory regions. To add a memory region you can use this function.

Example: To add region from 0x9000_0000 of size 0x1000_0000

_mmu_add_region((unsigned char *)0x90000000, 0x10000000,

E300CORE_MMU_SET_DBAT | E300CORE_MMU_CACHE_INHIBIT | E300CORE_MMU_CACHE_WRITE_THRU | E300CORE_MMU_CACHE_GUARDED | E300CORE_MMU_CACHE_COHERENT);

There number of regions is limited to 8 (8 DBAT and 8 IBAT) and the max size of region is 0x10000000

Hope this helps

- Visakhan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Visakhan,

I just applied the changes you suggested and that cured the crashing problem I was having. Thanks very much for spending your time to reply, that was a great help and I appreciate it.

Best Regards,

Tim Hutchinson

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you Visakhan,

I really appreciate your reply. I will give this a try and report back here. Hope you have a great day!

Best Regards,

Tim Hutchinson

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Look at attached file. This spreadsheet shows pins assignment for different modes of the MPC512x LocalPlus bus.

Check please your LocalPlus bus mode and pin assignment for this mode using this spreadsheet.

Have a great day,

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Paul,

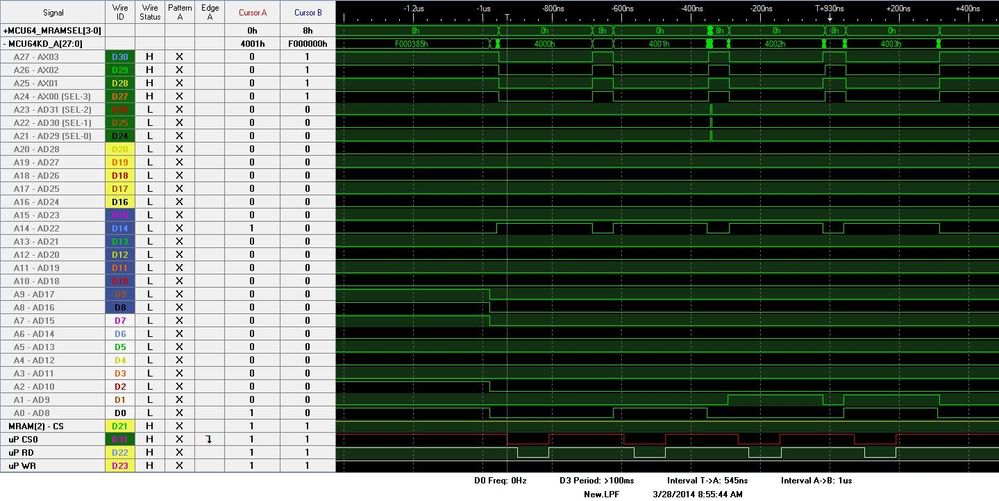

All LocalPlus bus pins are connected as shown in the spreadsheet you posted (thank you for that). And each of those pins are configured to perform the required function. Bus transactions to devices on the LocalPlus bus work properly to all address's where the EMB_AX[3-0] signals all remain 0. This screenshot from the bus analyzer shows 4 proper LocalPlus Bus reads from address's 0x1000_4000, 0x1000_4001, 0x1000_4002 and 0x1000_4003. Note that the EMB_AX[7-4] signals specifying Adr[31]-Adr[28] are not included. The problem comes when attempts to read (or write) an address where the EMB_AX[3-0] signals (address bits Adr[24] thru Adr[27]) are not all zeros. For example, an attempt to read the address 0x1100_0000 causes an immediate crash of the processor. There's got to be an LPB configuration step that I'm missing, I'm just unable to figure out what it might be. The Pins are all configured for their required functions, the access windows are defined (only really using one, CS_0) and the access window parameters (wait states, data size, muxed/not_muxed, etc) are all set. What else is there?

Thanks for your reply,

Best,

Tim