- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- MK10 clock issues

MK10 clock issues

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

My target is an MK10FN1M0VLQ12. I’ve tried using two clock options; a 25 Mhz oscillator to XTAL0 ->PLL0 with a 100Mhz and 60Mhz and the internal clock with 41,943Mhz.

I have measured the TRACE_CLKOUT at PTA6:

SIM->SOPT2 |= SIM_SOPT2_TRACECLKSEL_MASK

SIM->SCGC5 |= SIM_SCGC5_PORTA_MASK;

PORTA-> PCR[6] = PORT_PCR_MUX(0x7) | PORT_PCR_DSE_MASK;

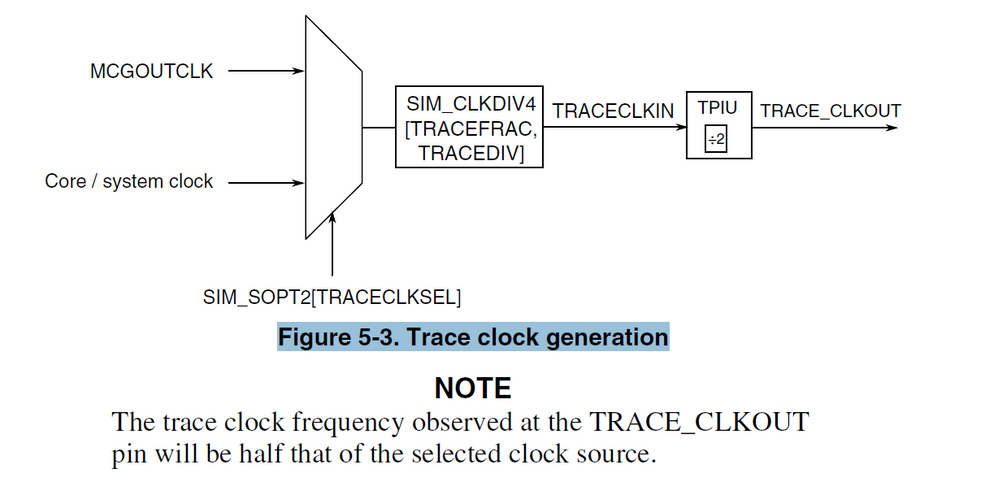

The Trace_CLKOUT shall be half of the core clock.

When the external clock is configured to 100Mhz the Trace_CLKOUT is 25MHz.

When the external clock is configured to 60Mhz the Trace_CLKOUT is 15MHz.

Also when the internal clock is configured to 41,943… Mhz the Trace_CLKOUT is 10.333MHz.

The external clock configuration:

25Mhz * (VDIV=24/ PRDIV=3)/2 = 100 Mhz and 25Mhz * (VDIV=24/ PRDIV=5) / 2 = 60Mhz

What is wrong with? My Uart gives me only gurba. When configuring the UART BDL (baud rate) according to measured value the UART gives me gurba as well. I’m using the KEIL ide.

Anny Idea what causing me this headache?

Internal CLK Config:

/* SIM_SCGC5: PORTA=1 */

SIM->SCGC5 |= (uint32_t)0x0200UL; /* Enable clock gate for ports to enable pin routing */

/* SIM_CLKDIV1: OUTDIV1=0,OUTDIV2=0,OUTDIV3=1,OUTDIV4=1,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0 */

SIM->CLKDIV1 = (uint32_t)0x00110000UL; /* Update system prescalers */

/* SIM_SOPT2: PLLFLLSEL=0 */

SIM->SOPT2 &= (uint32_t)~0x00030000UL; /* Select FLL as a clock source for various peripherals */

/* SIM_SOPT1: OSC32KSEL=0 */

SIM->SOPT1 &= (uint32_t)~0x00080000UL; /* System oscillator drives 32 kHz clock for various peripherals */

/* SIM_SCGC1: OSC1=1 */

SIM->SCGC1 |= (uint32_t)0x20UL;

/* PORTA_PCR18: ISF=0,MUX=0 */

PORTA->PCR[18] &= (uint32_t)~0x01000700UL;

/* Switch to FEI Mode */

/* MCG_C1: CLKS=0,FRDIV=0,IREFS=1,IRCLKEN=1,IREFSTEN=0 */

MCG->C1 = (uint8_t)0x06U;

/* MCG_C2: LOCRE0=0,??=0,RANGE0=2,HGO0=0,EREFS0=0,LP=0,IRCS=0 */

MCG->C2 = (uint8_t)0x20U;

/* MCG_C4: DMX32=0,DRST_DRS=1 */

MCG->C4 = (uint8_t)((MCG->C4 & (uint8_t)~(uint8_t)0xC0U) | (uint8_t)0x20U);

/* OSC0_CR: ERCLKEN=1,??=0,EREFSTEN=0,??=0,SC2P=0,SC4P=0,SC8P=0,SC16P=0 */

OSC0->CR = (uint8_t)0x80U;

/* OSC1_CR: ERCLKEN=1,??=0,EREFSTEN=0,??=0,SC2P=0,SC4P=0,SC8P=0,SC16P=0 */

OSC1->CR = (uint8_t)0x80U;

/* MCG_C7: OSCSEL=0 */

MCG->C7 &= (uint8_t)~(uint8_t)0x01U;

/* MCG_C5: PLLREFSEL0=0,PLLCLKEN0=0,PLLSTEN0=0,??=0,??=0,PRDIV0=0 */

MCG->C5 = (uint8_t)0x00U;

/* MCG_C6: LOLIE0=0,PLLS=0,CME0=0,VDIV0=0 */

MCG->C6 = (uint8_t)0x00U; /* 3 */

/* MCG_C11: PLLREFSEL1=0,PLLCLKEN1=0,PLLSTEN1=0,PLLCS=0,??=0,PRDIV1=0 */

MCG->C11 = (uint8_t)0x00U; /* 3 */

/* MCG_C12: LOLIE1=0,??=0,CME2=0,VDIV1=0 */

MCG->C12 = (uint8_t)0x00U; /* 3 */

External CLK config:

/* SIM_SCGC5: PORTA=1 */

SIM->SCGC5 |= (uint32_t)0x0200UL; /* Enable clock gate for ports to enable pin routing */

/* SIM->CLKDIV1: OUTDIV1=0,OUTDIV2=1,OUTDIV3=3,OUTDIV4=3,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0 */

SIM->CLKDIV1 = (uint32_t)0x01330000UL; /* Update system prescalers */

/* SIM->SOPT2: PLLFLLSEL=1 */

SIM->SOPT2 = (uint32_t)((SIM->SOPT2 & (uint32_t)~0x00020000UL) | (uint32_t)0x00010000UL); /* Select PLL 0 as a clock source for various peripherals */

/* PORTA_PCR18: ISF=0,MUX=0 */

PORTA->PCR[18] &= (uint32_t)~0x01000700UL;

/* Switch to FBE Mode */

/* OSC0->CR: ERCLKEN=0,??=0,EREFSTEN=0,??=0,SC2P=0,SC4P=0,SC8P=0,SC16P=0 */

OSC0->CR = (uint8_t)0x00U; /* ????????????????????????????? */

/* MCG->C7: OSCSEL=0 */

MCG->C7 &= (uint8_t)~(uint8_t)0x01U;

/* MCG->C2: LOCRE0=0,??=0,RANGE0=2,HGO0=0,EREFS0=1,LP=0,IRCS=0 */

MCG->C2 = (uint8_t)0x24U;

/* MCG->C1: CLKS=2,FRDIV=5,IREFS=0,IRCLKEN=0,IREFSTEN=0 */

MCG->C1 = (uint8_t)0xA8U;

/* MCG->C4: DMX32=0,DRST_DRS=0 */

MCG->C4 &= (uint8_t)~(uint8_t)0xE0U;

/* MCG->C5: PLLREFSEL0=0,PLLCLKEN0=1,PLLSTEN0=0,??=0,??=0,PRDIV0=1 */

MCG->C5 = (uint8_t)0x02U;//DIV3

/* MCG->C6: LOLIE0=0,PLLS=0,CME0=0,VDIV0=16(32) */

MCG->C6 = (uint8_t)0x08U;//multi24

while((MCG->S & MCG_S_IREFST_MASK) != 0x00U) { /* Check that the source of the FLL reference clock is the external reference clock. */

}

while((MCG->S & 0x0CU) != 0x08U) { /* Wait until external reference clock is selected as MCG output */

}

/* Switch to PBE Mode */

/* MCG->C6: LOLIE0=0,PLLS=1,CME0=0,VDIV0=0 */

MCG->C6 = (uint8_t)0x48U;

while((MCG->S & MCG_S_PLLST_MASK) != MCG_S_PLLST_MASK) { /* Wait until source of PLLS is PLLCS output clock */

}

while((MCG->S & MCG_S_LOCK0_MASK) != MCG_S_LOCK0_MASK) { /* Wait until PLL locked */

}

/* Switch to PEE Mode */

/* MCG->C1: CLKS=0,FRDIV=5,IREFS=0,IRCLKEN=0,IREFSTEN=0 */

MCG->C1 = (uint8_t)0x28U;

while((MCG->S & MCG_S_CLKST_MASK) != MCG_S_CLKST_MASK) { /* Wait until output of the PLL is selected */

}

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

I haven't done anything with K10/ 120MHz, however I have a clue in

SIM_CLKDIV4 field

Divider output clock = Divider input clock * ((TRACEFRAC+1)/(TRACEDIV+1))

defalut values are TRACEFRAC=0 and TRACEDIV=1

which defaults into

Divider output clock = Divider input clock * 0.5

Pavel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

probably you're missing the fixed by 2 divider at the PLL output? here's a post I seems similar to what you experiencing:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Did not miss the Fixed Divider:

25MHz * (24/3) /2 = 100 MHz MCGCLKOUT. Trace out: 25MHz

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

I haven't done anything with K10/ 120MHz, however I have a clue in

SIM_CLKDIV4 field

Divider output clock = Divider input clock * ((TRACEFRAC+1)/(TRACEDIV+1))

defalut values are TRACEFRAC=0 and TRACEDIV=1

which defaults into

Divider output clock = Divider input clock * 0.5

Pavel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Ok thanks, so the measured TRACE_CLKOUT is correct since MCGOUT/4. But then I can’t understand why my UART1 is giving me gurba and why Keil Logic Analyzer shows that the systick interrupts every 10 ms instead of 1 ms.

How can I debug this?

UART config:

SIM->SCGC5 |= SIM_SCGC5_PORTE_MASK; /* Enable PORTE gate clocking */

SIM->SCGC4 |= SIM_SCGC4_UART1_MASK; /* Enable UART 1 gate clocking */

PORTE->PCR[0] = PORT_PCR_MUX(3); /* Pin mux configured as ALT3, RX */

PORTE->PCR[1] = PORT_PCR_MUX(3); /* Pin mux configured as ALT3, TX */

uint32_t baudRate = 115200;

uint32_t moduleClock = SystemCoreClock;

uint32_t baudDivisor = 0;

uint32_t brfa = 0;

uint8_t abdh = 0;

uint8_t abdl = 0;

if ((moduleClock > 0) && (baudRate > 0))

{

baudDivisor = moduleClock / (baudRate << 4);

if (baudDivisor > 0)

{

brfa = ((((moduleClock - baudRate*(baudDivisor << 4)) << 1) + (baudRate >> 1)) / baudRate);

if (brfa >= 32) {

baudDivisor += 1;

brfa = 0;

}

}

if (baudDivisor > ((UART_BDH_SBR_MASK << 8) | UART_BDL_SBR_MASK))

{

return;

}

}

abdh = (uint8_t)((baudDivisor >> 8) & UART_BDH_SBR_MASK);

abdl = (uint8_t)(baudDivisor & UART_BDL_SBR_MASK);

pUart->BDH = abdh;

pUart->BDL = abdl;

pUart->C4 &= (~ UART_C4_BRFA_MASK);

pUart->C4 |= UART_C4_BRFA(brfa);

/* 8-bit mode. Normal operation */

pUart->C1 = 0;

/* Disable wakeups */

pUart->C2 &= (~ (UART_C2_RWU_MASK));

pUart->C4 &= (~ (UART_C4_MAEN1_MASK | UART_C4_MAEN2_MASK));

pUart->MA1 = 0;

pUart->MA2 = 0;

/* Disable all error interrupts */

pUart->C3 = 0;

/* Configure watermarks for rx and tx */

pUart->RWFIFO = UART_RWFIFO_RXWATER(1);

pUart->TWFIFO = UART_TWFIFO_TXWATER(0);

/* both RE,TE must be disabled before enable FIFO */

pUart->C2 &= ~(UART_C2_RE_MASK | UART_C2_TE_MASK);

/* Enable TX FIFO, enable RX FIFO */

pUart->PFIFO |= UART_PFIFO_TXFE_MASK | UART_PFIFO_RXFE_MASK;

/* Flush RX / TX buffers */

pUart->CFIFO |= UART_CFIFO_RXFLUSH_MASK | UART_CFIFO_TXFLUSH_MASK;

/* Transmitter and receiver enable */

pUart->C2 = UART_C2_RIE_MASK | /* RDRF interrupt or DMA transfer requests enabled. */

UART_C2_RE_MASK | /* Receiver enable */

UART_C2_TE_MASK; /* Transmitter enable */

/* Enable UART interrupts*/

NVIC_EnableIRQ(UART1_RX_TX_IRQn);