- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- how to bring up CSI_1 interface in parallel mode

how to bring up CSI_1 interface in parallel mode

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

how to bring up CSI_1 interface in parallel mode

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Now we meet a problem on CSI_1 interface of IPU_1. On our board CSI_1 is connected to adv7182 for video capture.

adv7182_HS and adv7182_VS signal are not used. and 8bit data port are connected as below

csi1 pixclk [pin H25] -> adv7182_pix_clk

csi1 data12 [pin G24] -> adv7182_data0

csi1 data13 [pin J22] -> adv7182_data1

csi1 data14 [pin G25] -> adv7182_data2

csi1 data15 [pin H22] -> adv7182_data3

csi1 data16 [pin H23] -> adv7182_data4

csi1 data17 [pin F24] -> adv7182_data5

csi1 data18 [pin J21] -> adv7182_data6

csi1 data19 [pin F25] -> adv7182_data7

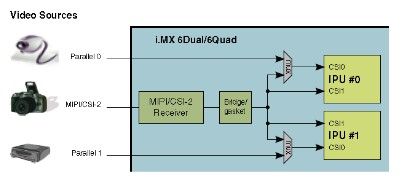

I noticed that CSI_1 is connected to IPU_1

.

So I make below patch for CSI_1 interface.

+ mxc_iomux_set_gpr_register(1, 20, 1, 1);

static struct fsl_mxc_capture_platform_data capture_data[] = {

{

.csi = 1,

- .ipu = 0,

+ .ipu = 1,

.mclk_source = 0,

- .is_mipi = 1,

+ .is_mipi = 0,

}

}

in file adv7182.c

static int adv7182_probe(struct i2c_client *client,

adv7182_data.sen.mclk = 27000000;

adv7182_data.sen.mclk_source = 0;

adv7182_data.sen.i2c_client = client;

adv7182_data.sen.streamcap.timeperframe.denominator = 30;

adv7182_data.sen.streamcap.timeperframe.numerator = 1;

adv7182_data.std_id = V4L2_STD_ALL;

video_idx = ADV7182_NOT_LOCKED;

adv7182_data.sen.pix.pixelformat = V4L2_PIX_FMT_UYVY; /* YUV422 */

adv7182_data.sen.pix.priv = 1; /* 1 is used to indicate TV in */

adv7182_data.sen.csi = 1;

adv7182_data.sen.on = true;

……

}

static int ioctl_g_ifparm(struct v4l2_int_device *s, struct v4l2_ifparm *p)

{

dev_dbg(&adv7180_data.sen.i2c_client->dev, "adv7180:ioctl_g_ifparm\n");

/* Initialize structure to 0s then set any non-0 values. */

memset(p, 0, sizeof(*p));

p->if_type = V4L2_IF_TYPE_BT656; /* This is the only possibility. */

p->u.bt656.mode = V4L2_IF_TYPE_BT656_MODE_NOBT_8BIT;

p->u.bt656.nobt_hs_inv = 0;

p->u.bt656.bt_sync_correct = 0;

p->u.bt656.clock_curr = 27000000;

p->u.bt656.clock_min = 6000000;

p->u.bt656.clock_max = 28000000;

return 0;

}

But the capture can’t work when I try to run mxc_v4l2_tvin.out application. The app pop up below message

ERROR: v4l2 capture: mxc_v4l_dqueue timeout enc_counter 0

It seems that the CSI_1 can’t capture any signal from data bus especially for pix clock.

I have measured the pix clock. it works out 27mhz clock signal as our expect.

My question are :

1. Do I need to configure the CSI data bus width and bit pos of LSB? how to configure this info for CSI_1 of IPU_1.

2. Please help to check my patch above. I don’t know whether I missed any important operations.

aa

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

In this discussion a file "adv7182.c" containing a function "adv7182_probe" is mentioned. Where to find this code?

I've checked

http://git.freescale.com/git/cgit.cgi/imx/linux-2.6-imx.git/log/?h=imx_3.0.35_4.1.0

and

http://git.freescale.com/git/cgit.cgi/imx/linux-2.6-imx.git/log/?h=imx_2.6.35_maintain

and can't find it there.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Jun,

I am also facing the same issue "ERROR: v4l2 capture: mxc_v4l_dqueue timeout enc_counter 0" while trying to capture the data using v4l2 driver.

I measured the pix clock, and found it is always high. Do we need to configure specific to pix clock in adv7182 registers? If yes, could you please provide those details. Expected output data format is 8-bit ITU BT656.

ADV7182 data lines, pix clock, HS and VS are connected to CSI0 of imx6DL. HS and VS are not required for BT 656 output as of my knowledge.

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello jun,

I also have similar problem. I am able to capture BT.656 video on IPU0/CSI0 but not on IPU1/CSI1 on sabre sd board. I made the following modifications to board-mx6q_sabresd.c

changed:

mxc_iomux_set_gpr_register(1, 19, 1, 1);

to:

mxc_iomux_set_gpr_register(1, 20, 1, 1);

changed:

static struct fsl_mxc_capture_platform_data capture_data[] = {

{

.csi = 0,

.ipu = 0,

.mclk_source = 0,

.is_mipi = 0,

}, {

.csi = 1,

.ipu = 0,

.mclk_source = 0,

.is_mipi = 1,

},

};

to:

static struct fsl_mxc_capture_platform_data capture_data[] = {

{

.csi = 1,

.ipu = 1,

.mclk_source = 0,

.is_mipi = 0,

}, {

.csi = 0,

.ipu = 1,

.mclk_source = 0,

.is_mipi = 1,

},

};

Setup mux pins to the following:

static iomux_v3_cfg_t mx6q_sabresd_csi1_sensor_pads[] = {

/* IPU2 Camera */

MX6Q_PAD_EIM_A17__IPU2_CSI1_D_12,

MX6Q_PAD_EIM_A18__IPU2_CSI1_D_13,

MX6Q_PAD_EIM_A19__IPU2_CSI1_D_14,

MX6Q_PAD_EIM_A20__IPU2_CSI1_D_15,

MX6Q_PAD_EIM_A21__IPU2_CSI1_D_16,

MX6Q_PAD_EIM_A22__IPU2_CSI1_D_17,

MX6Q_PAD_EIM_A23__IPU2_CSI1_D_18,

MX6Q_PAD_EIM_A24__IPU2_CSI1_D_19,

MX6Q_PAD_EIM_A16__IPU2_CSI1_PIXCLK,

};

But still can't get video captured. If you find a solution let me know. I will do the same for you.

Jonathan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hello jonathan,

Do you check the PAD select configuration? If want to use CSI_1, we need to modify the pad select configuration (DAISY chain) for each pin . Besides, do you check the pixel clock pin? it should output 27Mhz clock.

By the way, the reset pin and power_down pin must output high level. Finally , i think the 8bit data pin also need to check. Because the EAV and SAV signal are very important if you not use VS and HS signal. Hope above info could help you. If your design works, please let me know.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello jun,

The pad configurations I sent in the last message should also configure the daisy chain. For example, MX6Q_PAD_EIM_A16__IPU2_CSI1_PIXCLK is defined in iomux-mx6q.h as IOMUX_PAD(0x0408, 0x00F4, 2, 0x08E0, 1, 0) which will set the daisy pin configuration at address 0x08E0 to 1. I verified it is being set with memtool utility by reading register 020E08E0.

We have 27Mhz pixelclock coming from our device and input to pad H25 of the imx6. And data is present also. EAV and SAV are present. In our design our source is an HDMI receiver IC which is configured to output BT.656 8-bit with embedded synchs, not ADV7182 like you are using.

I am able to view video on IPU0/CSI0 using the same HDMI receiver configuration but not IPU1/CSI1.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hello jonathan,

We are sure that CSI_1 can work now. Formely, our design can't work is rooted by the crystal not output a stable signal. Please double check the signal quality of your hardware design.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi junsun

Would you share the adv7182.c and modifications you made for getting working with CSI0. For some reason we are not getting the INTR so not able to read the Video data from the CSI?

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hello jun,

Are you now capturing video data using mxc_4vl2_tvin?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

yes

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes,and in the ioctl_g_ifpara() must return as below if your design not use HS and VS pin static int ioctl_g_ifparm(struct v4l2_int_device *s, struct v4l2_ifparm *p)

{

dev_dbg(&adv7180_data.sen.i2c_client->dev, "adv7180:ioctl_g_ifparm\n");

/* Initialize structure to 0s then set any non-0 values. */

memset(p, 0, sizeof(*p));

p->if_type = V4L2_IF_TYPE_BT656; /* This is the only possibility. */

p->u.bt656.mode = V4L2_IF_TYPE_BT656_MODE_NOBT_8BIT;

p->u.bt656.nobt_hs_inv = 0;

p->u.bt656.bt_sync_correct = 0;

p->u.bt656.clock_curr = 0;

p->u.bt656.clock_min = 6000000;

p->u.bt656.clock_max = 28000000;

return 0;

}