- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- Kinetis UART SFIFO reserved bit becomes set during Rx underflow (using PE)

Kinetis UART SFIFO reserved bit becomes set during Rx underflow (using PE)

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

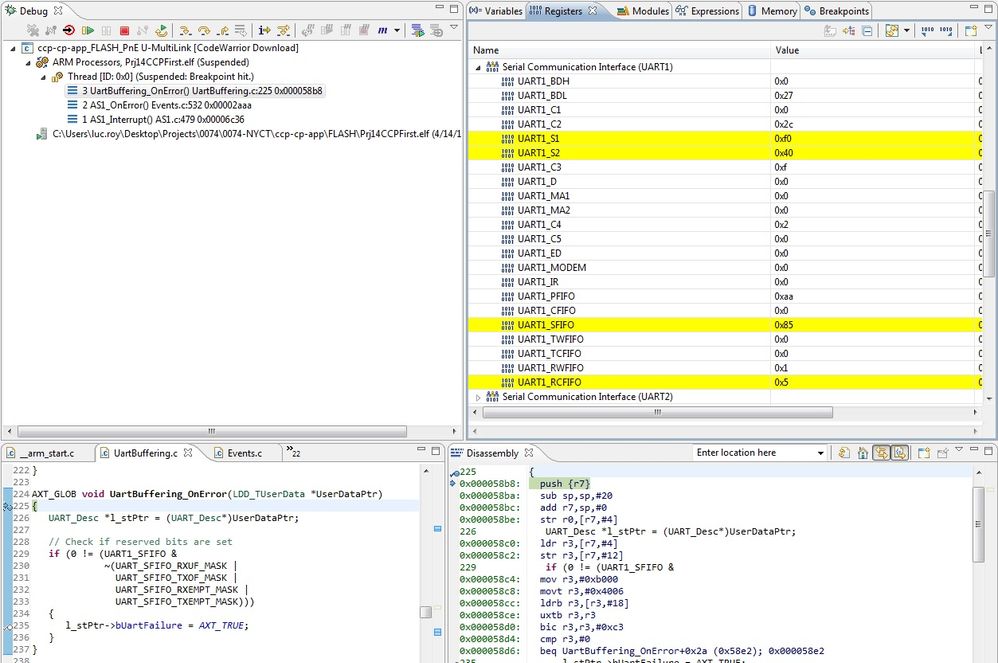

I am using the Processor Expert serial LLD component to send and receive data with UART1 on the Kinetis K10DX128VLL7.

At some point in time, the UART keeps the last character in the buffer and releases it when the next byte comes in .

To recreate the problem, I use the debugger to stop the processor, send a message longer than the uart buffer(>8), and start the processor.

This creates an overflow in the uart and the uart keeps the last character in the buffer (until the next one comes in, then the previous one is released and the new one is kept).

This also causes reserved bit in the SFIFO register to be set.

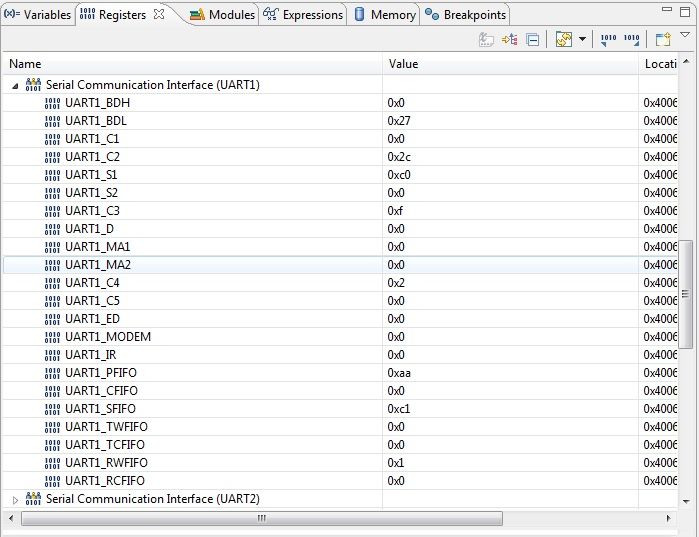

Using AS1_Init and AS1_Deinit functions, I have tried to reset the UART but that simply prevents me from receiving any data at all and the reserved bit is still there.

Questions:

What does that bit mean? (SFIFO = 85 where 0x4 bit mask is reserved)

How can I prevent that reserved bit from being set?

How can I reset the UART in this condition?

KinetisUart1RegistersAfterUnderflow

KinetisUart1RegistersAfterSystemResetAndInitialisation

Thank you

Luc

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The problem seemed to have disapeared as we fixed the collisions on the half duplex serial link

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The problem seemed to have disapeared as we fixed the collisions on the half duplex serial link

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Luc,

I have a similar problem to the one you described above and I would like to ask you to elaborate on the nature of your solution.

In my case there is an UART overflow, caused by interrupt long latency, which leaves the system with no active interrupt but with a char in the buffer.

This prevents from new char to be received. the only thing that releases the UART interface is D read.

Following this read the interface is released and the RX flow runs once again.

Tnx,

Gerry