- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- MQX Software Solutions

- :

- MQX Software Solutions

- :

- MQX and DMA

MQX and DMA

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

MQX and DMA

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Rozbergn,

please don't duplicate posts. I removed previous one and I'll add it here what was there:

In my application i need to collect information from ADC every 200us during 2 sec.

I would like to use DMA for this. Collect data in RAM and after save this information on SD card.

Anyone have such example or have another idea how to do this measurement?

Regards,

MartinK

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

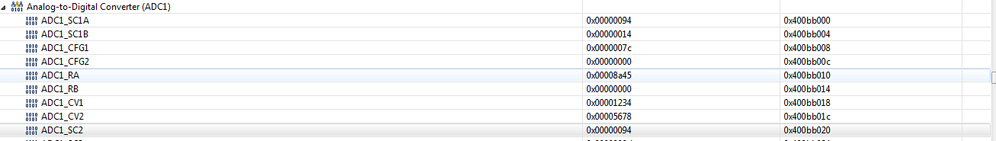

I am trying to set up the ADC1 (software trigger) with DMA tranfer. The issue is that the dma does not work properly. Bellow I show how the adc1 register is configurated:

As it can be seen, the register ADC1_RA is working and the DMAEN is enabled. Bellow I show how the dma code:

/*DMA MUX initialization*/

SIM_SCGC6 |= SIM_SCGC6_DMAMUX0_MASK | SIM_SCGC6_DMAMUX1_MASK; //enables DMA MUX clock gate

/*eDMA module initialization*/

SIM_SCGC7 |= SIM_SCGC7_DMA_MASK;//enables DMA clock gate, default value is enable

//***************************************************************

//**** DMA transfer request source – ADC0 conversion complete

//***************************************************************

DMAMUX0_CHCFG1 = 0

| DMAMUX_CHCFG_ENBL_MASK /* Enable routing of DMA request */

| DMAMUX_CHCFG_SOURCE(40); /* Channel Activation Source: AD_A Command */

DMA_CR = DMA_CR_GRP1PRI(0x00) |

DMA_CR_GRP0PRI(0x00) |

DMA_CR_EMLM_MASK |

DMA_CR_CLM_MASK |

DMA_CR_ERGA_MASK |

DMA_CR_ERCA_MASK;

//enables DMA0 request

DMA_ERQ = 0x03;

//***************************************************************

//**** Source address, ADC0_RA

//***************************************************************

DMA_TCD1_SADDR = (uint32) &ADC1_RA;

//***************************************************************

//**** Source address increment; data is still read for the same address, no increment needed

//***************************************************************

DMA_TCD1_SOFF = 0x00;

//***************************************************************

//**** Source address reload after major loop finishes, no reload needed//***************************************************************

DMA_TCD1_SLAST = 0x00;

//***************************************************************

//**** Destination address, SRAM buffer [0]

//*************************************************************

DMA_TCD1_DADDR = (uint32)&Data_Desti[0];

//***************************************************************

//**** Destination address increment in bytes, increment for next buffer address

//**** 16 bit => 2 bytes

//***************************************************************

DMA_TCD1_DOFF = 0x02;

//***************************************************************

//**** Destination address reload after major loop finishes,

//**** must be subtracted from last pointer value, sample number is 12 each and 2 bytes long,

//**** 2 × 12 = 24 and must be subtract -24

//***************************************************************

DMA_TCD1_DLASTSGA = -24;

//***************************************************************

//**** Number of bytes for minor loop (one data transfer), ADC0 result is 16 bits long, so

//**** 2-byte transfer

//***************************************************************

DMA_TCD1_NBYTES_MLNO = 0x02;

//***************************************************************

//**** Channel linking and major loop setting, linking after minor loop is enabled to

//**** channel 0 (0x0000), major loop transfers number 12 (0x0C)

//***************************************************************

DMA_TCD1_BITER_ELINKNO = (DMA_BITER_ELINKNO_ELINK_MASK|0x0000|0x0C);

//***************************************************************

//**** Channel linking and major loop setting reload value after major loop finishes,

//**** linking after minor loop is enabled, major loop transfers number 12 (0x0C).

//***************************************************************

DMA_TCD1_CITER_ELINKNO = (DMA_CITER_ELINKNO_ELINK_MASK|0x0C);

//***************************************************************

//**** Source and destination data width specification, both source and destination is 16-bit

//***************************************************************

DMA_TCD1_ATTR = 0 | DMA_ATTR_SSIZE(1)| DMA_ATTR_DSIZE(1);

//***************************************************************

//**** Common channel setting, linking after major loop enable to channel 0,

//**** IRQ request is generated after major loop complete

//***************************************************************

DMA_TCD1_CSR = (DMA_CSR_MAJORLINKCH(0) |

DMA_CSR_MAJORELINK_MASK|

DMA_CSR_INTMAJOR_MASK);

Maybe somebody knows the mistake...

Cheers.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

On ADC-DMA project , two points need to be pay attention: in ADC register enable DMA request (ADC0_SC2->DMAEN) and in DMA register enalbe peripheral request (DMA_DCR0->ERQ).