- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX RT

- :

- imx.RT1060 can't work with hyperFlash?

imx.RT1060 can't work with hyperFlash?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

imx.RT1060 can't work with hyperFlash?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

We just got today a new mimxrt1060 EVK.

It works fine with ram debug, but on configuring to spiflash it fails as following:

Wed Oct 31, 2018 17:22:14: IAR Embedded Workbench 8.30.1 (C:\Program Files (x86)\IAR Systems\Embedded Workbench 8.1\arm\bin\armproc.dll)

Wed Oct 31, 2018 17:22:14: Loaded macro file: C:\Program Files (x86)\IAR Systems\Embedded Workbench 8.1\arm\config\debugger\NXP\iMXRT.dmac

Wed Oct 31, 2018 17:22:14: Loaded macro file: C:\Program Files (x86)\IAR Systems\Embedded Workbench 8.1\arm\config\debugger\NXP\iMXRT_Trace.dmac

Wed Oct 31, 2018 17:22:14: Loading the CMSIS-DAP driver

Wed Oct 31, 2018 17:22:14: Probe: CMSIS-DAP probe SW module ver 1.13

Wed Oct 31, 2018 17:22:14: Probe: CMSIS-DAP S/N '0229000005da88a000000000000000000000000097969905' mapped to a number 97969905.

Wed Oct 31, 2018 17:22:14: Emulation layer version 4.34

Wed Oct 31, 2018 17:22:15: Notification to init-after-power-up hookup.

Wed Oct 31, 2018 17:22:15: Notification to core-connect hookup.

Wed Oct 31, 2018 17:22:15: Connected DAP v1 on SWD. Detected IDCODE=0xbd11477.

Wed Oct 31, 2018 17:22:15: Probe: ConnectSpec='CMSIS-DAP:0229000005da88a000000000000000000000000097969905:7-3A81E2DE-0-0000'.

Wed Oct 31, 2018 17:22:15: Connecting to TAP#0 DAP AHB-AP port 0 (IDR=0x4770041).

Wed Oct 31, 2018 17:22:15: Recognized CPUID=0x411fc271 Cortex-M7 r1p1 arch ARMv7-M

Wed Oct 31, 2018 17:22:15: Set cacheable access on AHB-AP port 0 (HPROT=0xeb000000).

Wed Oct 31, 2018 17:22:15: Debug resources: 8 instruction comparators, 4 data watchpoints.

Wed Oct 31, 2018 17:22:15: MultiCore: Asynchronous core execution FORCED.

Wed Oct 31, 2018 17:22:15: MultiCore: Synchronous core execution DISABLED.

Wed Oct 31, 2018 17:22:15: LowLevelReset(hardware, delay 200)

Wed Oct 31, 2018 17:22:16: Notification to init-after-hw-reset hookup.

Wed Oct 31, 2018 17:22:16: Probe: ConnectSpec='CMSIS-DAP:0229000005da88a000000000000000000000000097969905:7-3A81E2DE-0-0000'.

Wed Oct 31, 2018 17:22:16: Connecting to TAP#0 DAP AHB-AP port 0 (IDR=0x4770041).

Wed Oct 31, 2018 17:22:16: Recognized CPUID=0x411fc271 Cortex-M7 r1p1 arch ARMv7-M

Wed Oct 31, 2018 17:22:16: Set cacheable access on AHB-AP port 0 (HPROT=0xeb000000).

Wed Oct 31, 2018 17:22:16: Debug resources: 8 instruction comparators, 4 data watchpoints.

Wed Oct 31, 2018 17:22:16: CPU status - IN RESET

Wed Oct 31, 2018 17:22:17: Loaded debugee: C:\Users\ransh\Downloads\SDK_2.4.0_EVK-MIMXRT1060 (3) (1)\boards\evkmimxrt1060\demo_apps\shell\iar\flexspi_nor_debug\shell.out

Wed Oct 31, 2018 17:22:17: Download error at 0x60000000: downloading into non-writable memory.

Wed Oct 31, 2018 17:22:17: Download error at 0x60001000: downloading into non-writable memory.

Wed Oct 31, 2018 17:22:17: Download error at 0x60002000: downloading into non-writable memory.

Wed Oct 31, 2018 17:22:17: Download error at 0x60002000: memory write failed.

* In ram debugging with IAR (same project , imxrt1060, sdk 2.4.0) - no issue. Only with spiflash debug in IAR.

* With mimxrt1050 (sdk 2.4.2) no issues in spinor debug with IAR.

* It seems that xip examples is for qspi (not hyperflash) .

On trying to use the imxrt1050 hyperflash files instead of qspi, there is an error on startup !

* We also tried to change switch state - sw 7 by default is for qspi, we changed it to spiflash - 0110 - yet, no change in behaviour. Maybe it's SW5 ? Wwhy sw5 is not mentioned in MIMX1060 user guide ?

Can anyone help with this ?

ranran

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi ranran,

On the EVKB-MIMXRT1050 board, the HyperFlash is the default memory and it is required to apply a rework on the board to enable the QSPI Flash, however on the EVK-MIMXRT1060 is the opposite, the QSPI is the default memory and it is required to apply a rework on the board to enable the HyperFlash.

Hope this will be useful for you.

Best regards!

/Carlos

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Carlos,

Can you please elaborate what change in board is required if we need to work with hyperflash instead of qspi ?

Thank you,

ranran

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

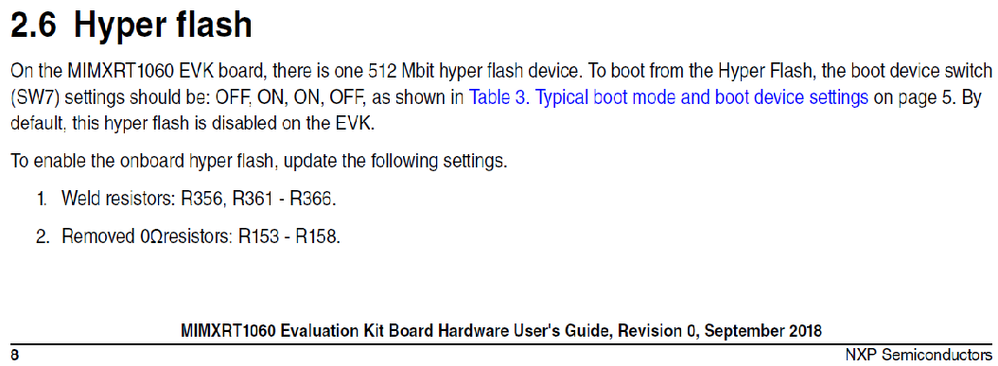

It is explained on section 2.6 of MIMXRT1060 Evaluation Kit Board Hardware User's Guide:

Hope this will be useful for you.

Best regards!

/Carlos

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------