- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- i.MX Forums

- :

- i.MX RT

- :

- iMXRT1176 MIPI-CSI2 pixel clock limitation

iMXRT1176 MIPI-CSI2 pixel clock limitation

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

As the title,

the camera inputs to MIPI-CSI.

Then, MIPI-CSI converts the data to the parallel CSI.

So, my question is, is the MIPI-CSI pixel clock limit the same as the CSI block limitation, 80MHz?

Or, can I input the 1080p camera? the pixel clock is about 125MHz.

Thanks.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Hamish1 ,

The csi pixel clock is limit to 80M. The mipi-csi input data rate must under this limit.

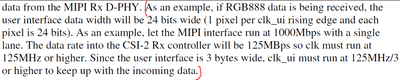

about the relation of the CSI_UI clock, there is a discription from our RM:

according to the MIPI interface freq, we can calculate the UI_clk, by:

ui_clk = MIPI_interface * datalanes / data-wide, where the MIPI_interface is 1.2/1.5Gbps, the datalanes is 2, and the data-wide is 24 for rgb888, or 16 for rgb565 from camera; so the ui_clk is 1.5G * 2 / 24(rgb888 as an example) = 125MHz, so we need to configure the ui_clk as 125MHz, then can capture the coming data. But please not that, the csi model can not support up to 125MHz pixel clk.

that means, for the rgb888, and 1.5G MIPI interface input, 2 lanes, RT1170 can not hold.

Regards,

Jing

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @jingpan

Thanks for your answer. It is helpful for me,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Hamish1 ,

The csi pixel clock is limit to 80M. The mipi-csi input data rate must under this limit.

about the relation of the CSI_UI clock, there is a discription from our RM:

according to the MIPI interface freq, we can calculate the UI_clk, by:

ui_clk = MIPI_interface * datalanes / data-wide, where the MIPI_interface is 1.2/1.5Gbps, the datalanes is 2, and the data-wide is 24 for rgb888, or 16 for rgb565 from camera; so the ui_clk is 1.5G * 2 / 24(rgb888 as an example) = 125MHz, so we need to configure the ui_clk as 125MHz, then can capture the coming data. But please not that, the csi model can not support up to 125MHz pixel clk.

that means, for the rgb888, and 1.5G MIPI interface input, 2 lanes, RT1170 can not hold.

Regards,

Jing