- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX RT

- :

- Re: iMXRT1021 ADC multi channel DMA transfer

iMXRT1021 ADC multi channel DMA transfer

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

iMXRT1021 ADC multi channel DMA transfer

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I would like to do a multichannel conversion at least 8channels, or more channels (I see the evkmimxrt1020_adc_etc_hardware_trigger_conv example).

From the Reference Manual, I see that there exists:

ETC DMA control Register (DMA_CTRL) 61.5.1.5

The only comment that's seen in the Reference Manual is this:

"DMA request or interrupts will assert according to the software configurations."

Is there any further detail available, or sample code describing the ADC multi channel DMA ?

Thanks,

Manu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jeremy,

The document points to AN4522 to get a deeper understanding of the DMA.

Reading the AN4522, I am a bit confused:

At some places the document refers to BITER as Beginning of "Major" Iteration count.

At some places, BITER is referred to as, Basic "Minor" loop count

Description #1 (2.2.8 Biter and Status/control bits) Page#12

-----------------------------------------------------------------------

If the biter.e_link field is cleared , then the content of bits 2–15 is biter (beginning 'major' iteration count)

The 'biter' field sets the initial number of the major loop counter (citer).

Description #2 (Table 7 Field descriptors) Page #13

-----------------------------------------------------------------------

biter[5:13]

Beginning “major” Iteration Count

This is the initial value copied into the citer field or citer.linkch field when the Major loop is completed. The citer fields control the iteration count and linking during channel execution.

Description #3 (2.3 Functional description of the DMA module)

-----------------------------------------------------------------------

If the Start signal in the the TCD is asserted in the corresponding channel, then the first Major loop starts. The number of the Major loops is set in the Biter field in the word 7 of the TCD. Initially, the values of the fields biter and citer are equal.

Biter specifies the number of the minor loops to be performed in one data transfer. If this loop needs peripheral request, the DMA channel is waiting for it.

After peripheral request is asserted, the Minor loop transfers nbytes of data.

2.3.4 The Major Loop (Table 10. Major loop parameters)

-----------------------------------------------------------------------

biter Basic minor loop count

I am confused, with different naming topologies for the same field. I cant think of it as a document bug, since it is not in one single place. This contradiction occurs at multiple places.

Thinking logically, both Minor and major counter existing for the same field is impossible, AFAICT.

Can you please explain, what's going on. Or what does the document mean for the BITER register field.

My head has been really tied in a knot.

Please help!

Thanks,

Manu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Manu,

Thanks for your reply.

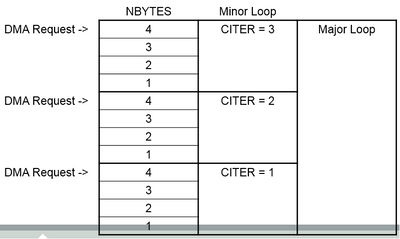

The block diagram demonstrates the DMA multiple transfer process.

The BITER is the initial iteration count and the CITER is the

current iteration count, at begin, they should be the same.

In the code of the application note: https://www.nxp.com/docs/en/application-note/AN4590.pdf, it shows how to configure them actually.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jeremy,

Uh!

I see that BITER and CITER should be the same and that they are Beginning and Current Counters.

What I dont understand is: which counter holds the "Major" count and which one holds the "Minor" count. It will need to track the Major count, while doing the Minor count ?

(ie, when there are both Major and Minor counters, where will the major counter be stored and where will the Minor counter be stored ?)

Thanks,

Manu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Manu,

Thanks for your reply.

In 《Using the DMA module in Kinetis devices》, it has illustrated the Minor loop and Major loop, you can find the below content in it and I think it's useful for beginners to understand the Minor loop and Major loop.

The control of the DMA module can be split into three levels:

- Basic transfer

- Minor loop

- Major loop

The basic transfer is the process in which the required source reads and destination writes occur in order to move the data, as well as source- and destination-address offset adjustments and decreasing of the number of bytes to be transferred happen. The minor loop is in charge of issuing another basic transfer if the number of bytes to be transferred has not been accomplished (bytes to be transferred = 0). The major loop contains the number of minor loops necessary to move the whole data. The number of minor loops in a major loop is specified by the beginning iteration count (BITER). Every time a minor loop terminates the current major loop iteration (CITER) decreases by one. Once the CITER reaches a value of 0 the whole data have been successfully transferred. These levels are illustrated in my previous reply.

Hope it helps.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jeremy,

I am trying to implement what we discussed.

In fsl_edma.c, there appears to me, 2 sets of implementations.

The first one deals with the TCD's themselves directly.

eg:

EDMA_TcdSetTransferConfig()

and there seems to be another version

eg:

EDMA_PrepareTransferConfig()

A bit of confusion, which one should be used ?

Thanks,

Manu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jeremy,

Thanks for the reply and the docs.

Let me please read the docs and then get back, once things are a bit more clear.

Thanks Again,

Manu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jeremy,

Thanks for the reply and the time.

PIT is as the hardware trigger of the ADC_ETC, when it happens, the ADC_ETC will complete 8 conversions due to the chain feature, when the conversion completes, a DMA request will arise and be assigned to a DMA channel to transfer the ADC data to the destination area

The first part of your explanation is clear and my understanding resonates with what you said. However, the second part is not quite clear to me.

after transfer finishes, take advantage of DMA link feature, it will trigger another DMA channel to write a specific data to DMA_CTRL register to disable the DMA request.

I do see CITER.LINKCH, BITER.LINKCH, MAJOR.LINKCH and MAJOR.E_LINK in the TCD structure.

The document fails to explain properly, some of the basic/fundamental concepts being used therein.

The document definitely needs a significant revision in terms of the language, explanation of the concepts described within etc. It would definitely help a lot of people.

I do not understand, what the DMA link feature is. I tried reading the documentation a few different times, from different angles altogether. But all I am getting is a headache.

Maybe you could enlighten me a bit.

I do not see any diagram. You forgot to attach something ?

Thanks,

Manu