- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- i.MX Forums

- :

- i.MX RT

- :

- i.mxrt1050, HyperFlash and Page Boundary Crossing Latency

i.mxrt1050, HyperFlash and Page Boundary Crossing Latency

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

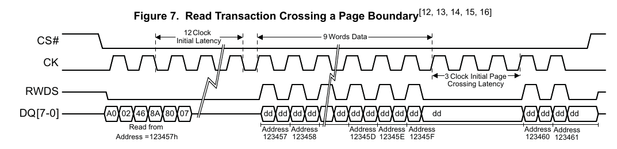

I noted that the HyperFLASH S26KS512S used on the IMXRT1050-EVKB doesn't only have a latency before the data but can also have a latency when crossing a page boundary. For that see Figure 7 on page 13 of this document: https://www.cypress.com/file/213346/download

I didn't find anything in the i.MXRT1050 reference manual that said that this case can be handled. Can the FlexSPI controller handle these Crossing Latency or is it just avoided to get into the situation by always reading whole pages?

Related question:

If I have seen it correctly, the ROM boot loader sets up a LUT that has 6 clock cycles at a frequency of about 130 MHz. In DDR mode that's only three clock cycles on the bus. Thats a lot fewer than the 13 latency clocks described in the data sheet of the HyperFlash.

I assume that the FlexSPI controller only reads data when there is activity on the RWDS line. Is that correct?

Best regards

Christian

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for your reply and clarification.

1) If I understand it correctly, that would mean that the FlexSPI is ready to receive data after 2 dummy cycles. But the flash will only start toggling the RWDS line after 10 clocks. Would the FlexSPI continue to clock the line till there is a high on RWDS (or some timeout is reached)?

-- As I know, the XIP mode usually works well even with the ’inappropriate‘ dummy cycles, so I think the FlexSPI continues to clock the line till there is a high on RWD.

2) I can just set something small and the memory will just deliver data as soon as it can, doesn't it? Is there an advantage to set the correct number of dummy cycles during read?

-- No, compared to the cache feature, and prefetch feature of FlexSPI, I don't think the fewer dummy cycles don't have such an affection as you expect.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thank you for your interest in NXP Semiconductor products and for the opportunity to serve you.

1) Can the FlexSPI controller handle these Crossing Latency or is it just avoided to get into the situation by always reading whole pages?

-- Enable cache feature to avoid the case.

2) I assume that the FlexSPI controller only reads data when there is activity on the RWDS line. Is that correct?

-- Yes, by the way, the dummy cycle had better be set to 0xB instead of 0x6.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello @jeremyzhou

thanks for the reply. I think I'm still not 100% sure about that topic.

If the FlexSPI only reads data when there is activity on RWDS (which you confirmed to my second question), why would I ever need a setting for the dummy cycles that is higher than (for example) 2 to 4 for the HyperBus? It would have just to be long enough so that the RWDS line isn't still set by the HyperBus device to signal whether there should be an additional latency or not. Is that correct? Or is there some kind of timeout that I missed?

Also for my first question you said that I should enable cache to avoid the case. But if the FlexSPI doesn't read data if there is no activity on RWDS, I shouldn't have to avoid it. Or did I understand that wrong? Of course it will make a difference in performance. But performance optimization is a different problem.

Best regards

Christian

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for your reply.

1) If the FlexSPI only reads data when there is activity on RWDS (which you confirmed to my second question), why would I ever need a setting for the dummy cycles that is higher than (for example) 2 to 4 for the HyperBus?

-- Whether you want to know the reason for inserting the latency cycles for reading operation, I'm not clear with it actually, I think you'd better contact the Flash manufactuer to learn that.

2) Also for my first question you said that I should enable cache to avoid the case. But if the FlexSPI doesn't read data if there is no activity on RWDS, I shouldn't have to avoid it. Or did I understand that wrong? Of course it will make a difference in performance. But performance optimization is a different problem.

-- In my opinion, you're right, however, I'd like to suggest you'd better use OSC to confirm that.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello @jeremyzhou

thanks again for your answer.

Regarding 1): Most likely I explained that not clearly: Assume a read transaction (writes will be different). Let's assume I set the dummy cycles to 2. Let's further assume the flash wants 10.

If I understand it correctly, that would mean that the FlexSPI is ready to receive data after 2 dummy cycles. But the flash will only start toggling the RWDS line after 10 clocks. Would the FlexSPI continue to clock the line till there is a high on RWDS (or some timeout is reached)?

From what I currently have seen, I would expect that it would do. Like I said earlier: It seems that the ROM loader sets 6 dummy cycles while the flash would expect something like 12 or 13. But in that case I'm a bit irritated why I even have to bother with selecting the right number of dummy cycles. I can just set something small and the memory will just deliver data as soon as it can, doesn't it? Is there an advantage to set the correct number of dummy cycles during read?

Note: I'm aware that write is something different. For a write, the FlexSPI controller has to drive the RWDS line and therefore the latency has to be set at least as long as necessary.

Best regards

Christian Mauderer

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for your reply and clarification.

1) If I understand it correctly, that would mean that the FlexSPI is ready to receive data after 2 dummy cycles. But the flash will only start toggling the RWDS line after 10 clocks. Would the FlexSPI continue to clock the line till there is a high on RWDS (or some timeout is reached)?

-- As I know, the XIP mode usually works well even with the ’inappropriate‘ dummy cycles, so I think the FlexSPI continues to clock the line till there is a high on RWD.

2) I can just set something small and the memory will just deliver data as soon as it can, doesn't it? Is there an advantage to set the correct number of dummy cycles during read?

-- No, compared to the cache feature, and prefetch feature of FlexSPI, I don't think the fewer dummy cycles don't have such an affection as you expect.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------