- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX RT

- :

- Re: i.MX1060 SDRAM issue

i.MX1060 SDRAM issue

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

i.MX1060 SDRAM issue

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I want to change the setting of “DLL delay chain clock“.

In Rev 1 of the IMXRT1060RM, this can be done via DLLSEL and DQSSEL field of MCR register.

However, they are removed from Rev 2 of the reference manual.

Please advise where we can set SDRAM read clock source to “DLL delay chain clock” and add more delay? thanks !

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thank you for your interest in NXP Semiconductor products and for the opportunity to serve you.

1) However, they are removed from Rev 2 of the reference manual.

Please advise where we can set the SDRAM read clock source to “DLL delay chain clock” and add more delay? thanks!

-- Actually, the SEMC module doesn't contain the DLLSEL and DQSSEL bits area, so they're removed in the updated version of RM.

Hope this is clear.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi jeremyzhou,

Thank you for your quick reply.

if so, how to add more delay?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for your reply.

1) Please check the datasheet to figure the impact of DSQ mode on the SEMC timing specification.

1) How to add more delay?

-- What kind of delay or time do you want to add?

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

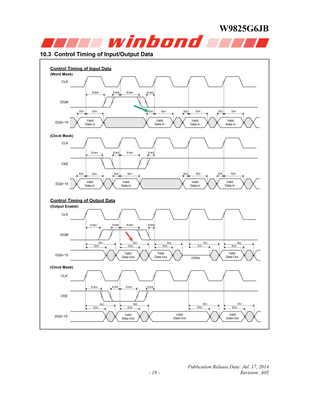

We are looking at delaying of DQS similar to FlexSPI input operation shown 1.jpg.

For SEMC/SDRAM input operation, the datasheet only specified the data input setup and hold time. It does not mentioned how to configure the delay of DQS. I cannot find any text on the capacitor connected to the DQS pad.

Please point me to the right paragraph that explain how the capacitor works when DQSMD = 0x01.

We hope to add delay of 1 to 3 ns to SEMC_DQS by using the right value of capacitor.

thanks !

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for your reply.

Actually, NXP recommends Flexspi_DQS and SEMC_DQS pads both be floating and do not used for other functions if external memory has not this DQS dedicated pin, and it's useless to connect the capacitor to the DQS pad of the above memory chip to add the delay time.

So I think you'd better refer to the datasheet of the external memory which has the DQS pin if you want to try to add the delay time, it may provide some guides to make it.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Our design and SDRAM selection were done based on the design of NXP RT1060 EVB. Both SDRAM from ISSI and Winbond selected by NXP do not have DQS pin.

When DQS pin of i.MX RT1060 is recommended to be left floating, please confirm DQSMD should be set to 0x1 or 0x0?

We need to check the TIS spec accordingly. When DQSMD = 0x0, TIS of 8.67ns (> Tclk166mHz 6.01ns) does not make sense.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for your reply.

1) When DQS pin of i.MX RT1060 is recommended to be left floating, please confirm DQSMD should be set to 0x1 or 0x0?

-- You can set the DQSMD to 0x01 to achieve the maximum speed.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Setting DQSMD to 0x01 will not work with our design using the Winbond SDRAM at all. Note that the same SDRAM was also used in i.MX RT106F vision solution.

About 8-10 months back, it was NXP FAE who told us to set DQSMD to 0x0 when we first tried to turn on this Winbond SDRAM.

Lastly, please comment that on TIS of 8.67ns when DQSMD is set 0x0. How will 8.67ns work with Tac (5 to 5.4ns) of any SDRAM in CAS 3 read operation?

The timings do not tally on paper but it worked with Winbond SDRAM when DQSMD is set to 0x0.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for your reply.

TIS is used to demonstrate the input timing, so it's not fit for reading operation actually (as Fig 1 shows).

Fig 1

In further, after checking, the pins of W9825G6JB-6I is almost compatible with IS42S16160J-6BLI, and the SEMC can access the IS42S16160J-6BLI successful when DQSMD is set to 0x1, maybe you can give a try.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------