- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX RT

- :

- i.MX RT1176 boot from flash but execute from SRAM

i.MX RT1176 boot from flash but execute from SRAM

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

i.MX RT1176 boot from flash but execute from SRAM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I'm evaluating an i.MX RT1176 MCU on a TQMa117xL base board (from TQ Systems).

At the moment I'm working on some network speed tests with the lwip lperf code.

Using release code I get datarates on the 1 GB-port around 60-90 MBit/s, which is not enough for us. Even the mentioned optimizations on the lwip web site have no or negative effects on the performance. But then I switched on the option "link application to ram" and the performance was boosted to 340 MBit/s running debug code with a segger jlink lite probe.

Now I want to test the release code speed while booting from the on-board SPI flash. With the "link application to ram" option on it is not possible to flash the .axf with the Secure Provisioning tool anymore.

The error message is: "ERROR: Start address of the application must be greater or equal to 0x20002000, because bootable image contains Image Vector Table, Boot Data and DCD at 0x20001000-0x20001FFF"

I think this is correct as the program (booted from the SPI flash) has no idea how to copy the program into the SRAM without any additional code.

So is it correct that the option "link application to ram" makes only sense when using it with a debugger probe?

Is there an application note or example for this MCU how to copy the code from flash to SRAM and to start the code from there for production purposes?

I read a lot of documentation and posts but it is still not clear how to go on with this. I'm using MCUXpresso v11.7.0 [Build 9198] and the 2.13.0 SDK for MIMXRT1176.

Thanks and bye,

Oliver

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello

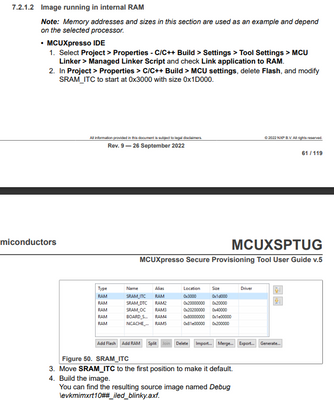

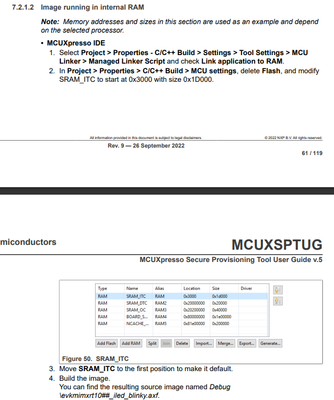

To be able to load the image to SRAM through Provisioning Tool it is needed to offset your application as your error suggests. To do this, please follow the steps from the Tool User Guide.

This document can also be helpful: Generating a Bootable Image for the RT1050 - NXP Community

Best regards,

Omar

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Omar, thanks for your answer!

In the meantime I managed to boot from RAM (release code, no debug probe) as mentioned in the Provisioning Tool documentation. But one fact is missing in both the IDE and Provisioning Tool documentation: How the boot process works in that case.

From the IDE documentation:

There are two important considerations when developing with RAM based projects:

1. They require support from the debug environment to be run and so may not execute in the

exactly the same manner as a true application running from an MCU reset.

What's missing here is the fact that it is possible to boot from RAM without a debug environment (and there are good reasons for it, see my first post).

So the boot process seems to work in the following way:

1. POR

2. ROM bootloader starts

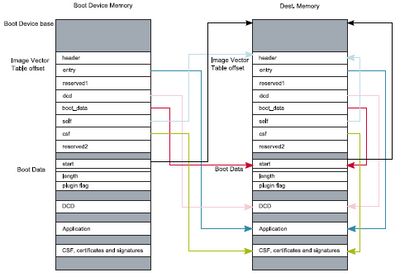

3. ROM bootloader copies the program from flash to ITC RAM with offset 0x3000 (IVT and DCD before)

4. Bootloader starts the image at IVT+0x3000

I don't find much information about these four steps. So the option "link application to RAM" is not enough, we need the Provisioning Tool which does some additionally steps for us.

Can you please describe these steps in more detail? Are my assumptions correct?

Unfortunately, the article for the RT1050 is rather outdated as there are tools mentioned which already have successors, working in a different way.

I have one problem left: I'd like to boot from the OC1 SRAM. I read a different thread, where this could be resolved with an additional offset. But I have no clue what that means and how to feed the Provisioning Tool with this information.

Thanks and bye,

Oliver

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The offset is required to reserve the space for the flashloader and the configurations for the image. In this image, you can find the bootflow for the image

The IVT contains information for a successful boot as the entry address:

To reserve this OCRAM space used in ROM you need modify the start and size of the SRAM on MCUXpresso as step 2 on the User Guide suggests.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Omar,

I think now it's clear. But the mentioned User Guide describes booting from the ITC SRAM, which works fine for me. But as the space is limited there to 256 KiB, I'd like to use the SRAM_OC1.

For this the 0x3000 offset is not enough as a part of the SRAM_OC1 is used in the bootup process as mentioned in this post:

https://community.nxp.com/t5/i-MX-RT/iMXRT1170-boot-from-OCRAM/td-p/1561956

So, is my assumption right that I need to put the program in SRAM_OC1 at location 0x2025000?

In this case I will loose 64 KiB of program space and the maximum size for my program in SRAM_OC1 is 448 KiB. Is this correct?

Thanks and bye,

Oliver

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

This is correct. Since the offset needs to be bigger then the remaining OCRAM space will be smaller.

Best regards,

Omar