- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX RT

- :

- Re: Why would a DSB instruction never complete?

Why would a DSB instruction never complete?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Why would a DSB instruction never complete?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi All,

MIMXRT1021DAF5A, IAR compiler, FreeRTOS, code in Serial Flash (SQPI)

I have a DSB instruction that never completes. This causes a processor 'lockup'. This is the sequence of events:

1. Code executing normally

2. SysTick interrupt occurs.

3. System 'stops'. (I do not know why it stops - I guess the pipeline has just fetched the DSB instruction)

4. Using J-Link Commander, I 'halt' and read register contents. I can confirm PC = first instruction of SysTick handler. Stack & registers OK, and consistent.

5. Using J-Link Commander, I 'single step' :

6. PUSH {R7,LR} - OK

7. MOVS R0,#32 - OK

8. MSR BASEPRI,R0 - OK

9. DSB #15 - Any J-Link Commander command after this reports 'CPU is not halted!'. Trying to 'halt' the CPU says 'WARNING: CPU could not be halted'

I think this means the DSB instruction never completed. I think the CPU is waiting for an input to allow DSB to complete which never comes.

Why would a DSB instruction never complete?

Thanks,

Chris.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kerry,

Are you saying that all memory should be changed to DEVICE_MEMORY or STRONGLY_ORDERED? This will stop the prefetch?

But it also stops the Cache right?

Thanks,

Chris.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

For example

LDR R0,#0

LDR R1,=0x40000000 ;No memory at this address

TST R0,#0

BEQ jump ;will always branch

LDR R0,[R1] ; will attempt to read an invalid memory location if speculatively executed, will cause a fault?

.jump

Will that cause a fault?

How can I stop it causing a fault?

Is the only fix to disable speculative fetching?

Chris.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Can you simplify your question, and reproduce your issue with the SDK and the NXP MIMXRT1020EVK board?

Take an example, when you use some of your asm examples, then enter the fault or the lockup issue, and let me reproduce that issue and check more details about it, it may be more visually discuss your problems. Even I meet some issues after reproducing your issue, I also can check it with our internal side, otherwise, just some asm code piece, I am also a little confused about the detail speculate result, sorry about it.

Best Regards,

Kerry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kerry,

I think I have fixed it. I found the MPU was incorrectly configured. I had taken a reference project for the EVK, but now I understand it better, I found the setup was wrong.

I have no idea why that would cause instructions to not complete in the Debugger though!!

But my system appears stable now... I hope!

Chris.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Chris Cowdery,

Do you mean the SDK MPU configuration is incorrect, or your own project?

Could you please also share your detail MPU configuration and the detail root point which will cause your issues?

Thanks a lot for your contribution.

Best Regards,

Kerry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

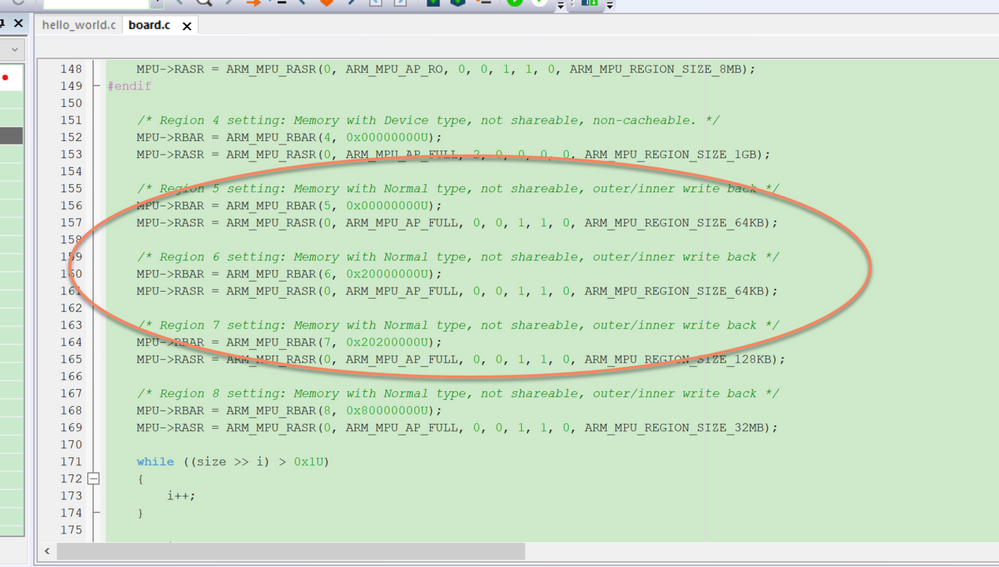

Hi Kerry,

I mean all the Example Projects in the SDK that I have looked at are wrong. Here is one from evkmimx1020->rtos_examples->freertos_generic.

I think I used this as my base project.

board.c:

/* MPU configuration. */

void BOARD_ConfigMPU(void)

{

/* Disable I cache and D cache */

if (SCB_CCR_IC_Msk == (SCB_CCR_IC_Msk & SCB->CCR)) {

SCB_DisableICache();

}

if (SCB_CCR_DC_Msk == (SCB_CCR_DC_Msk & SCB->CCR)) {

SCB_DisableDCache();

}

/* Disable MPU */

ARM_MPU_Disable();

/* Region 0 setting */

MPU->RBAR = ARM_MPU_RBAR(0, 0xC0000000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 2, 0, 0, 0, 0, ARM_MPU_REGION_SIZE_512MB);

/* Region 1 setting */

MPU->RBAR = ARM_MPU_RBAR(1, 0x80000000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 2, 0, 0, 0, 0, ARM_MPU_REGION_SIZE_1GB);

/* Region 2 setting */

#if defined(XIP_EXTERNAL_FLASH)

MPU->RBAR = ARM_MPU_RBAR(2, 0x60000000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 0, 0, 1, 1, 0, ARM_MPU_REGION_SIZE_512MB);

#else

MPU->RBAR = ARM_MPU_RBAR(2, 0x60000000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 2, 0, 0, 0, 0, ARM_MPU_REGION_SIZE_512MB);

#endif

/* Region 3 setting */

MPU->RBAR = ARM_MPU_RBAR(3, 0x00000000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 2, 0, 0, 0, 0, ARM_MPU_REGION_SIZE_1GB);

/* Region 4 setting */

MPU->RBAR = ARM_MPU_RBAR(4, 0x00000000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 0, 0, 1, 1, 0, ARM_MPU_REGION_SIZE_128KB);

/* Region 5 setting */

MPU->RBAR = ARM_MPU_RBAR(5, 0x20000000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 0, 0, 1, 1, 0, ARM_MPU_REGION_SIZE_128KB);

/* Region 6 setting */

MPU->RBAR = ARM_MPU_RBAR(6, 0x20200000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 0, 0, 1, 1, 0, ARM_MPU_REGION_SIZE_256KB);

/* The define sets the cacheable memory to shareable,

* this suggestion is referred from chapter 2.2.1 Memory regions,

* types and attributes in Cortex-M7 Devices, Generic User Guide */

#if defined(SDRAM_IS_SHAREABLE)

/* Region 7 setting, set whole SDRAM can be accessed by cache */

MPU->RBAR = ARM_MPU_RBAR(7, 0x80000000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 0, 1, 1, 1, 0, ARM_MPU_REGION_SIZE_32MB);

#else

/* Region 7 setting, set whole SDRAM can be accessed by cache */

MPU->RBAR = ARM_MPU_RBAR(7, 0x80000000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 0, 0, 1, 1, 0, ARM_MPU_REGION_SIZE_32MB);

#endif

/* Region 8 setting, set last 2MB of SDRAM can't be accessed by cache, glocal variables which are not expected to be accessed by cache can be put here */

MPU->RBAR = ARM_MPU_RBAR(8, 0x81E00000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 1, 0, 0, 0, 0, ARM_MPU_REGION_SIZE_2MB);

/* Enable MPU */

ARM_MPU_Enable(MPU_CTRL_PRIVDEFENA_Msk);

/* Enable I cache and D cache */

SCB_EnableDCache();

SCB_EnableICache();

}

You can see that the memory sizes for ITCM, DTCM and OCRAM are incorrect.

I found a few other things that I thought were incorrect.

This is my version:

/* MPU configuration. */

void BOARD_ConfigMPU(void)

{

/* Disable I cache and D cache */

if (SCB_CCR_IC_Msk == (SCB_CCR_IC_Msk & SCB->CCR)) {

SCB_DisableICache();

}

if (SCB_CCR_DC_Msk == (SCB_CCR_DC_Msk & SCB->CCR)) {

SCB_DisableDCache();

}

/* Disable MPU */

ARM_MPU_Disable();

// Document AN12042 'Using the i.MXRT L1 Cache'

// page 5 gives the default configuration, which is overlaid with this one

// where differences exist (i.e. if a region is not specified below,

// it retains it's default configuration)

// ARM_MPU_RASR(DisableExec, AccessPermission, TypeExtField, IsShareable, \

// IsCacheable, IsBufferable, SubRegionDisable, Size)

// 0x80000000-0xDFFFFFFF is external memory like SDRAM etc. Not used.

/* Region 0 setting */ // give external memories no access (1.5Gb total 0x80000000-0xdfffffff)

MPU->RBAR = ARM_MPU_RBAR(0, 0xC0000000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_NONE, 0, 0, 0, 0, 0, ARM_MPU_REGION_SIZE_512MB);

/* Region 1 setting */ // give external memories no access

MPU->RBAR = ARM_MPU_RBAR(1, 0x80000000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_NONE, 0, 0, 0, 0, 0, ARM_MPU_REGION_SIZE_1GB);

/* Region 2 setting */

// External flash at 0x60000000-0x7fffffff. Cacheable and executable.

MPU->RBAR = ARM_MPU_RBAR(2, 0x60000000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 0, 0, 1, 1, 0, ARM_MPU_REGION_SIZE_512MB);

/* Region 3 setting */

// This is all of RAM, which we will disable, then make sub-regions with the

// appropriate attributes. 0x00000000-0x3fffffff

MPU->RBAR = ARM_MPU_RBAR(3, 0x00000000U); // default = no access

MPU->RASR = ARM_MPU_RASR(1, ARM_MPU_AP_NONE, 2, 0, 0, 0, 0, ARM_MPU_REGION_SIZE_1GB);

/* Region 4 setting I-TCM */

// 0x00000000-0x0000ffff, Executable, cacheable

MPU->RBAR = ARM_MPU_RBAR(4, 0x00000000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 0, 0, 1, 1, 0, ARM_MPU_REGION_SIZE_64KB);

/* Region 5 setting D-TCM */

// 0x20000000-0x2000ffff, Not executable, cacheable

MPU->RBAR = ARM_MPU_RBAR(5, 0x20000000U);

MPU->RASR = ARM_MPU_RASR(1, ARM_MPU_AP_FULL, 0, 0, 1, 1, 0, ARM_MPU_REGION_SIZE_64KB);

/* Region 6 setting OCRAM */

// 0x20200000-0x2021ffff, Not executable, cacheable

MPU->RBAR = ARM_MPU_RBAR(6, 0x20200000U);

MPU->RASR = ARM_MPU_RASR(1, ARM_MPU_AP_FULL, 0, 0, 1, 1, 0, ARM_MPU_REGION_SIZE_128KB);

/* Enable MPU */

ARM_MPU_Enable(MPU_CTRL_PRIVDEFENA_Msk);

/* Enable I cache and D cache */

SCB_EnableDCache();

SCB_EnableICache();

}

I have no external SDRAM.

I would like somebody who understands the MPU to check for me. For example, ITCM and DTCM do not use the cache, but if I disable the cache in those regions, it does not work!

Many thanks,

Chris.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Seems you are using the old SDK, do you try the SDK2.8.0?

I checked the SDK2.8.0,the ITCM, DTCM and OCRAM size is correct:

Now, on your side, if you modify the related RAM size, do you still have issues or not?

You can download the newest SDK from this link:

Welcome | MCUXpresso SDK Builder

You also can try the newest SDK on your side, whether after you disable the cache, you still have issues or not?

Best Regards,

Kerry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kerry,

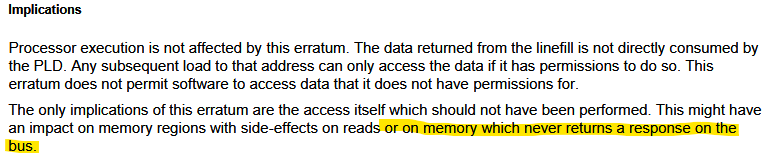

Thankyou!, that is very interesting. I see the MPU configuration has changed a lot because of Errata 1013783!

Does the RT1021 lock-up because of the yellow highlighted text above? And this why the default memory map must be ARM_MPU_AP_NONE?

I am going to merge in the changes from SDK2.8.0 and test.

Chris.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Seems related to the Arm errata 1013783-b, that's why the sdk MPU configuration also have modified the related code, just workaround speculative prefetch.

you can test the SDK2.8.0 to check it, as I know, our SDK2.8.0 code for RT fixed a lot of bugs.

Best Regards,

Kerry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kerry,

I believe this has fixed the problem. Impossible to prove, but the system has not crashed / locked up for 2 weeks.

Thankyou for your help.

Chris.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Do you have the MIMXRT1020-EVK board?

And can you reproduce the issue in the official board with the SDK?

Best Regards,

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------