- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX RT

- :

- Re: Why is RamFunction located in SRAM_DTC and not SRAM_ITC

Why is RamFunction located in SRAM_DTC and not SRAM_ITC

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The MCUxpresso generated linker section for SRAM_DTC looks like the following:

/* Main DATA section (SRAM_DTC) */

.data : ALIGN(4)

{

FILL(0xff)

_data = . ;

PROVIDE(__start_data_RAM = .) ;

PROVIDE(__start_data_SRAM_DTC = .) ;

*(vtable)

*(.ramfunc*)

KEEP(*(CodeQuickAccess))

KEEP(*(DataQuickAccess))

*(RamFunction)

*(.data*)

. = ALIGN(4) ;

_edata = . ;

PROVIDE(__end_data_RAM = .) ;

PROVIDE(__end_data_SRAM_DTC = .) ;

} > SRAM_DTC AT>PROGRAM_FLASH

The equivalent SRAM_ITC section does have some ramfunc.*, but not the main *(RamFunction).

Wondering why that is?

ITC is otherwise not used for anything. Seems wasteful.

Thanks,

Paul.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi p_shep,

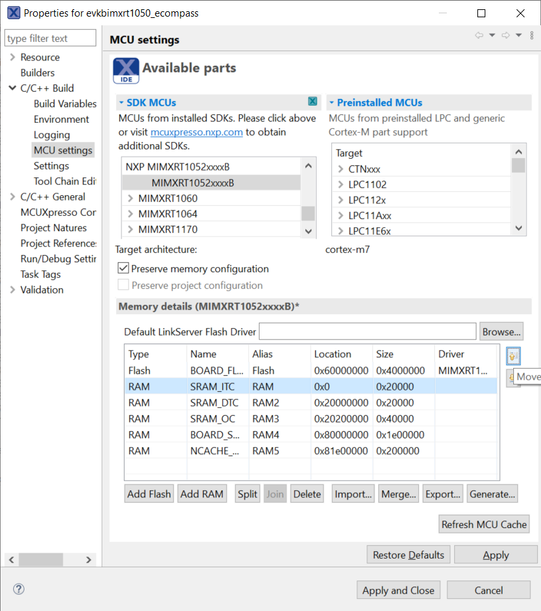

The examples in SDK default use flash and DTCM. Because DTCM is data TCM, ITCM is instruction TCM. If you want to put code or data into ITCM you can set in MCUXpresso. Then IDE will update .ld file.

Click the yellow up arrow to move selected memory up in the table.

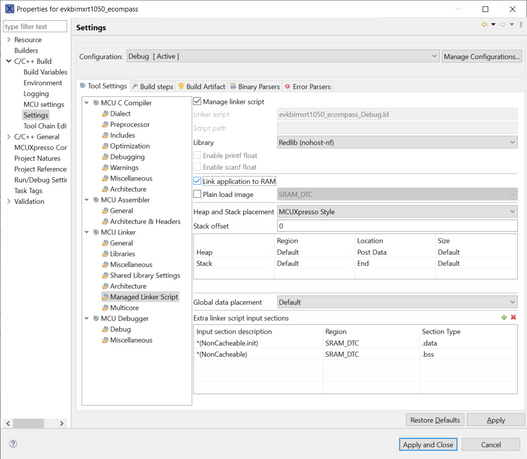

Link application to RAM or change Heap and Stack placement.

Regards,

Jing

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

OK, so I've just tried, and now I know why.... it doesn't work.

Hit this issue:

Essentially, since ITC is located at 0x00000000, the jump from Flash (0x70000000) is too great and you get a linker failure.

So that 128K of RAM is wasted?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I don't understand what you mean. But jump from flash to ITCM is no problem. You can have the bootloader to copy code from flash and jump to there, or you can copy and jump by yourself. There isn't any address restriction to ARM CPU.

Regards,

Jing

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

OK, so no technological reason for it, just the way the SDK has it set up.

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi p_shep,

The examples in SDK default use flash and DTCM. Because DTCM is data TCM, ITCM is instruction TCM. If you want to put code or data into ITCM you can set in MCUXpresso. Then IDE will update .ld file.

Click the yellow up arrow to move selected memory up in the table.

Link application to RAM or change Heap and Stack placement.

Regards,

Jing