- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- i.MX フォーラム

- :

- i.MX RT

- :

- SRAM base address should be set as 0xA000_0000

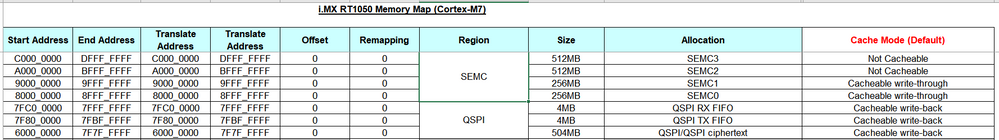

SRAM base address should be set as 0xA000_0000

オプション

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

解決済み

10-11-2019

02:02 AM

1,169件の閲覧回数

george

Senior Contributor II

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Dear All,

Does the NOR interface behave the same as the SRAM interface with respect to “set SRAM base address as 0xA000_0000 to avoid this behavior” ?

And does it happen in 8bit data widht mode?

BR,

George

解決済! 解決策の投稿を見る。

1 解決策

11-01-2019

01:17 AM

939件の閲覧回数

NXP Employee

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi George,

It is not about SEMC, it is up to ARM arch, so PRAM interface should have the same limitation, and for PNOR, it doesn't support AXI write.

Best Regards,

Jay

3 返答(返信)

10-15-2019

11:27 PM

939件の閲覧回数

NXP Employee

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi George,

What kind of NOR do you mean? Parallel NOR over SEMC or Serial NOR over FlexSPI?

Best Regards,

Jay

10-16-2019

05:21 AM

939件の閲覧回数

george

Senior Contributor II

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

11-01-2019

01:17 AM

940件の閲覧回数

NXP Employee

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi George,

It is not about SEMC, it is up to ARM arch, so PRAM interface should have the same limitation, and for PNOR, it doesn't support AXI write.

Best Regards,

Jay