- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX RT

- :

- SPI using DMA with a Scatter/Gather (MIMXRT1020)

SPI using DMA with a Scatter/Gather (MIMXRT1020)

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

SPI using DMA with a Scatter/Gather (MIMXRT1020)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We are facing the following problem when using the SPI in DMA (Slave) mode with Scatter/Gather.

We are filling 100 frames (each frame has 28 Bytes length) read from SPI SLAVE. And in another asynchronous timer callback, we occasionally get TCD[channel].DADDR destination address and evaluate the values written by the DMA. But we are having issues getting this destination address periodically. In a fixed 14.6 seconds period the destination address (TCD[channel].DADDR) returns a wrong value. By the way the 14.6 seems constant for each buffer size or read period configurations.

So far we couldn't find any solution for this issue. What might be the reason?

Thanks in advance

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Could you try the system application only with SPI slave working with eDMA module?

If in this application situation, there still has the same issue?

Have a great day,

Mike

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

seems like there is something like a dirty read. We have tried without SPI (edma scatter/gather example) and we observed the same issue periodically. Please try the code attached which is modified from the original driver examples (edma_scatter_gather.c) to see the issue.

We read TCD[channel].DADDR in an asynchronous loop (every 5ms), independent from the eDMA's loop. We guess that when we try to read DADDR while eDMA is changing its content (it is probably when at the end of TCD), we read a meaningless value.

We would be glad if you can address this issue, since it affects our application design decisions seriously. regards...

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

First of all, really sorry for the delay reply.

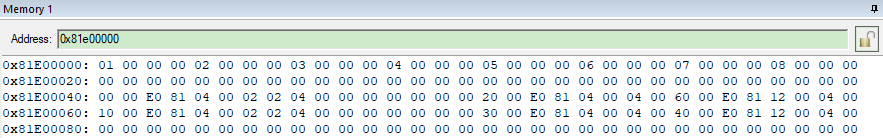

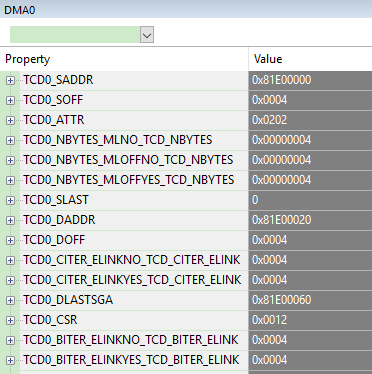

During debug, I could find there with below eDMA TCD transfer configurations at SDRAM address: 0x81e00060 & 0x81e00040:

eDMA channel 0 will dynamic scatter/gather TCD configurations from SDRAM address: 0x81e00060 & 0x81e00040

From you tested code, the core will change source address value.

There could exists eDMA and core access SDRAM memory range at the same time, so it will arbitrated SDRAM access with NIC-301. Please set eDMA priority higher than core to access external SDRAM memory.

Thank you for the attention.

best regards,

Mike