- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX RT

- :

- Re: QSPI flash chip addressing

QSPI flash chip addressing

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

QSPI flash chip addressing

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

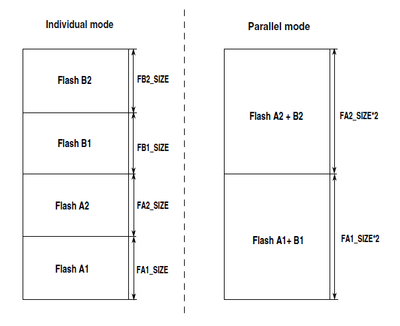

I have a new design and need clarification on how QSPI flash units are addressed. I have two 128Mb flash chips running on the Flexspi unit of a iMXRT1062. One is tied to SPI-A-SS0-B and the other is tied to SPI-A-SS1-B, the rest of the signals are shared. Would I be able to access 0x60000000 to 0x60010000 with the second chip automatically selected at the rollover point?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thank you for your interest in NXP Semiconductor products and for the opportunity to serve you.

1)Would I be able to access 0x60000000 to 0x60010000 with the second chip automatically selected at the rollover point?

-- No, I'm afraid not, and I'd like to suggest you go through the 27.5.5 Flash memory map section in the RM to learn the memory assignment.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Is there sample driver code for setting up individual QSPI flash on A1 and A2. I have tried to mod the sdk flexspi_nor program but it seems to fail anytime I set the flash size for A2 like it is conflicting with A1. I get bogus vendor ID and the erase verify fails. The only change I made was adding the second SetFlashConfig call for A2. This first flash is on SPI-A-SS0-B and the second on SPI-A-SS1-B.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for your reply.

To provide the fastest possible support, I'd highly recommend you to refer to the application note, moreover, the attachment is its demo code.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I just need some clarification. In the sample code I see A2Port being set to quad mode but not A1Port. Also, there are other commands that set A1Port but not A2Port. Should not both ports be set or does the proc do that for you?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- 1)Would I be able to access 0x60000000 to 0x60010000 with the second chip automatically selected at the rollover point?

-- No, I'm afraid not, and I'd like to suggest you go through the 27.5.5 Flash memory map section in the RM to learn the memory assignment.

Hm, my answer is yes, of course. Provided FAx_SIZE and FBx_SIZE settings are programmed correctly and do match memory chip sizes, QSPI memory area should be contiguous like it is shown in your picture, chip selects will act accordingly. Memory chips, which are not used may have their settings FAx_SIZE or FBx_SIZE equal zero and that would be still contiguous memory area.

Regards,

Edward