- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX RT

- :

- Problem with SPEED field in SW PAD Control Register when using flexio2

Problem with SPEED field in SW PAD Control Register when using flexio2

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Problem with SPEED field in SW PAD Control Register when using flexio2

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi All,

I'm using Flexio2 of imxrt1064 for transfer display data to LCD module via Intel 8080 bus.

I set Pin Mux for these pins( LCD Pins ) as Flexio2, and then set Pin Config called SW PAD Control

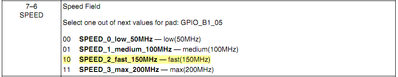

Register with SPEED field is 「10 : SPEED_2_fast_150MHz — fast(150MHz)」

With this speed, outgoing data lost, and LCD displayed incorrect.

If I change speed to 「00」or 「01」, this problem does not occur, and LCD displays correct.

My setting of Core clock frequency and AHB is 132Mhz, Flexio2 frequency is 120Mhz.

【Questions】

1. What does SPEED mean?

2. Mhz of Speed is based on what ( AHB or Flexio2 frequency, or other? )

3. When a pin set MUX as a flexio2 pin (120Mhz), and set speed of PAD 50Mhz, How does this pin frequency become?

Thanks & Best regards!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

See Operating Frequency section of GPIO chapter in latest RM (v1) for DSE/SRE/SPEED configuration.

1.Speed means the max toggle frequency supported in the PAD

2.Final output is based on FlexIO

3.In this case, it is 50MHz, so we need to increase speed value

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @jay_heng and All

Could you support me this issue?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @jay_heng

Thanks for your reply. I still have some questions.

>>3. When a pin set MUX as a flexio2 pin (120Mhz), and set speed of PAD 50Mhz, How does this pin frequency become?

>3.In this case, it is 50MHz, so we need to increase speed value

If pin set MUX as a flexio2 pin (120Mhz), and set speed of PAD 150Mhz, How does this pin frequency become? I think it is 120Mhz, is it right ?

And as description of my problem,

>AHB is 600Mhz, Flexio2 is 120Mhz, PAD of SPEED is 150Mhz, operation would be OK.

if Final output is based on FlexIO, why operation is not OK when AHB have been changed to 132Mhz?

All these cases have the same VDD_SOC (DCDC.REG3.TRG = 0x0E ) is 1.15v.

Could you explain detail the cause of my problem?

Thanks & Best regards!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

See my two blogs for GPIO speed topic

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello

Hope you are well.

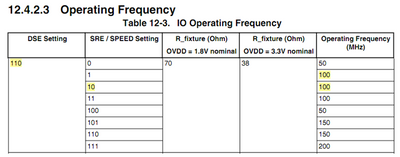

SPEED is a selectable bit field that sets electrical characteristics of a pin in a given frequency range. This field provides additional 2-bit slew rate control. These options can either increase the output driver current in the higher frequency range or reduce the switching noise in the lower frequency range.

The operational frequency on GPIO pads is dependent on slew rate (SRE), speed (SPEED), and supply voltage (OVDD). See Operating Frequency table in the GPIO block guide for more details (table 12-2).

If you have more questions do not hesitate to ask me.

Best regards,

Omar

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have seen Operating Frequency table as you recommended.

As my issue, 2 cases of setting (SPEEDーDSEーSRE)

0xB0 0111 0000

0x70 1011 0000

have the same Operating Freq, but the results are different when I change AHB clock (see my description and questions). I think something (not only Flexio, but also AHB clock?) is influencing it.

What do you think about this?

Btw, could you explain about R_fixture and OVDD ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I apologize for my delayed reply.

AHB clock has an impact on modules that are fed by that source so if this value is changed we expect different behavior.

R_Fixture is the resistance of the pad while OVDD is the IO supply.

If you have more questions do not hesitate to ask me.

Best regards,

Omar