- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX RT

- :

- Power up failure of internal 1.1V core voltage

Power up failure of internal 1.1V core voltage

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi NXP engineers,

MIMXRT1064CVJ5B is used in our product. The internal 1.1V core voltage is powered by on-chip DC/DC module with PSWTICH RC delay.

It is found that if system power 3.3V power down and then power up immediately, the internal 1.1V core voltage would not be generated and stays at 0V. The internal 1.1V core voltage starts up properly when system power 3.3V power down for a longer time, e.g. 1s, and then power up.

What is the reason and how to solve this issue?

Thanks

Guanmian Xu

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @geem-guanmian_x ,

Why do you need so frequent and quick power on and power off?

To your issue, the root reason is the RC circuit didn't fully discharged, whether, the hardware can consider some discharged circuit and which not influence the RC delay time during POR?

Best Regards,

Kerry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Tested and update: this problem looks like RC delay not long enough?

1) Original HW same as EVK: 30k resistor + 0.22uF capacitor: 1.1V core voltage can not be generated if 3.3V system voltage does not drop to 0 and immediately power up.

2) Change the 30k resistor to 130k, then 1.1V core voltage starts up correctly in this case.

If 3.3V system voltage does not power up from 0V in some cases, e.g. from 2V, what is the requirement of the RC delay time?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @geem-guanmian_x ,

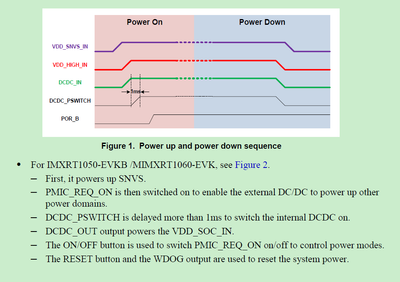

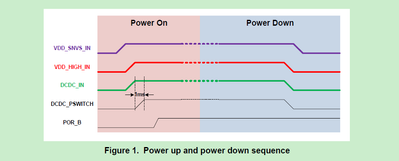

Please refer to the hardware design guide, the POR sequence is very important:

https://www.nxp.com/webapp/Download?colCode=MIMXRT105060HDUG

Another important case:

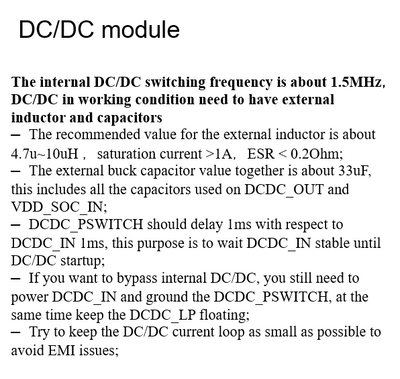

Need to ensure DCDC_IN ramps to 3.0 V within 0.2 x RC, RC is from external delay circuit used

for DCDC_PSWITCH and must be longer than 1 ms.

An RC delay circuit is recommended for providing the delay between DCDC-IN stable and DCDC_PSWITCH. the total RC delay should be 5-15ms.

Delay from DCDC_IN stable at 3V min to DCDC-PSWITHCH reaching 0.5*DCDC_IN(1.5v) must be at least 1ms.

Please check your own board again, the delay is very important.

Best Regards,

Kerry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi NXP engineer,

Thanks for reply.

Ramp rate of DCDC_IN will be checked and PSWITCH RC delay time will be matched accordingly.

You mentioned: Delay from DCDC_IN stable at 3V min to DCDC-PSWITCH reaching 0.5*DCDC_IN(1.5v) must be at least 1ms.

Now the case does not meet this requirement: if DCDC_IN voltage dipped for a short time, this voltage does not fall to 0 (e.g. just falling to 2V) and goes to 3.3V immediately, internal 1.1V core voltage falls to 0 and will not be generated again due to PSWITCH does not raising from 0. This case is possible in application, how to ensure the PSWITCH RC delay time? Do you have any suggestions?

Best regards

Guanmian Xu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

So, you need to make sure your DCDC_IN stable at first, then the RC circuit will help you get the delay time.

To better talking about your issues, please also provide your power sequency like this:

So, your delay time should count begin from your DCDC_IN =3V, then delay at least 1ms.

BTW, you mentioned : system power 3.3V power down and then power up immediately.

Your issue is caused by your RC circuit didn't fully discharged, as you know, power off, RC circuit discharge to low level also need time, so to make it works, you can detect your PSWITHCH, make sure it is 0V, then you do another power on, it should works.

Best Regards,

Kerry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi NXP engineer,

Yes, the PSWITCH signal does not fall to 0 in voltage dip scenario. Please see waveforms attached.

So which voltage level (<1V?) should the PSWITCH signal be discharged?

Simple RC delay design like EVK board would be not enough in this case, Do NXP have any design guide?

Best regards

Geem Xu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @geem-guanmian_x ,

Your Power off should still not enough to discharge the voltage, seems you in 1V, but do you check, the 1ms delay between 3.3V DCDC_IN to the DCDC-PSWITCH reaching 0.5*DCDC_IN(1.5v) is guaranteed or not?

About the design guide, refer to MIMXRT105060HDUG.pdf

https://www.nxp.com/webapp/Download?colCode=MIMXRT105060HDUG&location=null

Best Regards,

Kerry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi NXP engineer,

Thank you for the quick reply.

The 1ms delay between 3.3V DCDC_IN to the DCDC-PSWITCH reaching 0.5*DCDC_IN(1.5v) can not be guaranteed in voltage dip case, since the 3.3V DCDC_IN may drop in any voltage (e.g. >1.5V) and start up immediately (this could happen in industrial site), the DCDC-PSWITCH is falling to the same voltage due to the RC delay is connected with 3.3V DCDC_IN.

We will think of a hardware update, let me know if you have a good idea.

Best regards

Guanmian Xu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @geem-guanmian_x ,

Why do you need so frequent and quick power on and power off?

To your issue, the root reason is the RC circuit didn't fully discharged, whether, the hardware can consider some discharged circuit and which not influence the RC delay time during POR?

Best Regards,

Kerry