- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX RT

- :

- Not working "power down counter" in WDOG1

Not working "power down counter" in WDOG1

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi All,

I am testing the correct function of the "power down counter" in #WDOG1 on my device. There was never a restart using the "power down counter" in WDOG1.The "Time-Out Counter" in WDOG1 works correctly.

Pin J11 is set as WDOG1_B and connected to Reset pin M07 (POR_B).

Test procedure: After reset, the WDOG1_init(); function is called. Then I switch the DIP switch, which causes the unit to jump into an infinite loop the next time the unit is turned on and does not call the WDOG1_init (); function.

I reset the processor. I am waiting for a processor reset after 16 seconds. The processor reset will never occur.

1 - Why doesn't the processor restart with the "power down counter" after 16 seconds?

2 - Is pin J11 configured as WDOG1_B after start?

I'm using MIMXRT1061CVJ5B, #MCUXpresso IDE 11.5.0, SDK_2.x_MIMXRT1060-EVK

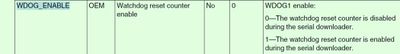

The settings in MCUXpresso are listed below:

Thank you for answer.

Jaroslav C.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

1.- in the example, you find the next code

void SystemInit (void) {

#if ((__FPU_PRESENT == 1) && (__FPU_USED == 1))

SCB->CPACR |= ((3UL << 10*2) | (3UL << 11*2)); /* set CP10, CP11 Full Access */

#endif /* ((__FPU_PRESENT == 1) && (__FPU_USED == 1)) */

#if defined(__MCUXPRESSO)

extern uint32_t g_pfnVectors[]; // Vector table defined in startup code

SCB->VTOR = (uint32_t)g_pfnVectors;

#endif

/* Disable Watchdog Power Down Counter */

WDOG1->WMCR &= ~(uint16_t) WDOG_WMCR_PDE_MASK;

WDOG2->WMCR &= ~(uint16_t) WDOG_WMCR_PDE_MASK;

so the WDOG is disable by the systeminit

2.-no, this macro is used by ROM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I tried the example for WDOG01. It only shows the TIMEOUT COUNTER functionality. The example does not show the POWERDOWN COUNTER functionality. In the datasheet IMXRT1060RM.pdf it is written that the PDE bit is set to 1 (default)(for POWERDOWN COUNTER). I always have a value of 0 after starting.

I have three questions:

1 - Is the PDE bit reset by the bootloader in ROM?

2 - Do I have to burn the WDOG_ENABLE fuse so that the CPU is still protected by WDOG1? Does the bootloader first stop the POWERDOWN COUNTER and then turn on the TIME-OUT COUNTER in WDOG1 if the WDOG_ENABLE fuse is set? I am using the "FlexSPI (Serial NOR) boot fusemap" boot according to IMXRT106XSRM.pdf.

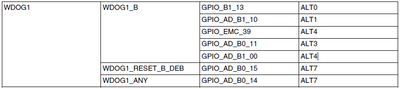

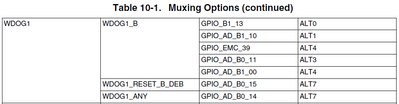

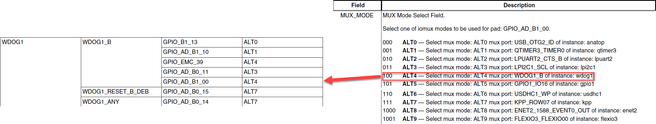

3 - Muxing Options allows setting to 1 of 5 pins for external signal WDOG1_B according to datashee IMXRT1060RM.pdf. I use GPIO_AD_B1_00 ALT4. When WDOG1 reaches zero in the bootloader, which pin does it pull to zero? Am I able to select the pin for which it pulls from the bootloader (WDOG_B signal)?

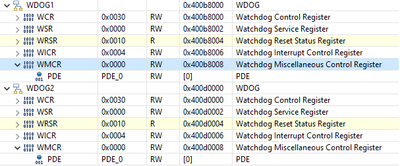

WDOG1 registers after startup:

WDOG1 Muxing Options:

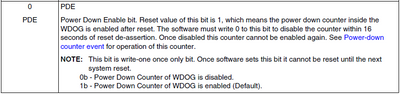

Watchdog Miscellaneous Control (WMCR) register:

I am using a custom board. I have EVK board with i.MXRT1052. I tested WDOG on EVK board too.

Thank you for your help.

Jaroslav C.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @cerma The IMXRT106XSRM.pdf is a Rev v1, we have a newer Rev v3, so I recommend checking it, I share the link https://www.nxp.com/webapp/sps/download/preDownload.jsp?render=true

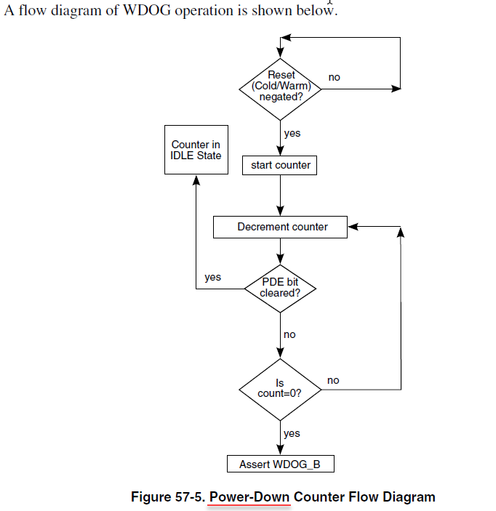

The WDOG modules operate as follows:

• If servicing does not take place, the timer times out and the wdog_rst_b signal is

activated (low)

• Interrupt can be generated before the counter actually times out

• The wdog_rst_b signal can be activated by software

• There is a power-down counter which gets enabled out of any reset. This counter has

a fixed timeout period of 16 seconds upon which it will assert the ipp_wdog_b

signal.

The WDOG asserts WDOG_B in the following scenarios:

• Software write to WDA bit of Watchdog Control (WCR). WDOG_B signal remains

asserted as long as the WDA bit is "0".

• WDOG timeout condition, WDT bit of Watchdog Control (WCR) must be set for

this scenario. A description of the timeout condition can be found in the Timeout

event. WDOG_B (ipp_wdog) signal remains asserted until a power-on reset (POR)

occurs. It gets cleared after the POR occurs (not due to any other system reset).

Figure 57-4 shows the timing diagram of WDOG_B (ipp_wdog) due to timeout

condition.

• WDOG power-down counter timeout, PDE bit of Watchdog Miscellaneous Control

(WMCR) should not be cleared for this scenario. A description of this counter can be

found in the Power-down counter event. WDOG_B (ipp_wdog) signal remains

asserted for one clock cycle of low frequency reference clock (ipg_clk_32k).

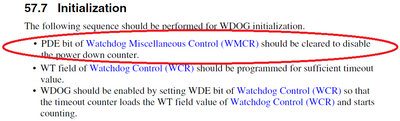

Initialization

The following sequence should be performed for WDOG initialization.

• PDE bit of Watchdog Miscellaneous Control (WMCR) should be cleared to disable

the power down counter.

Initialization

i.MX RT1060 Processor Reference Manual, Rev. 3, 07/2021

3260 NXP Semiconductors

• WT field of Watchdog Control (WCR) should be programmed for sufficient timeout

value.

• WDOG should be enabled by setting WDE bit of Watchdog Control (WCR) so that

the timeout counter loads the WT field value of Watchdog Control (WCR) and starts

counting.

Configuring the Watchdog Once

All watchdog control bits, timeout value, and window value are write-once after

reset . This means that after a write has occurred they cannot be changed unless a

reset occurs. This is guaranteed by the user configuring the window and timeout value

first, followed by the other control bits, and ensuring that CS[UPDATE] is also set to 0.

This provides a robust mechanism to configure the watchdog and ensure that a runaway

condition cannot mistakenly disable or modify the watchdog configuration after

configured.

The new configuration takes effect only after all registers except CNT are written after

reset. Otherwise, the WDOG uses the reset values by default. If window mode is not used

(CS[WIN] is 0), writing to WIN is not required to make the new configuration take

effect.

Have a good day

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Carlos,

You dont understand me.

I have red it in the datasheet (IMXRT1060RM.pdf).

I claim that the datasheet does not correspond to reality.

You wrote (according to the datasheet):

This initialization sequence is not correct for me as a customer. I claim that when my code is starting, the PDE bit is already clear (=0)! I also verified it on EVK board with example WDOG.

I think the PDE bit already clears the bootloader in the ROM (from NXP). The bootloader does many things before jumping into my application (described in MCUBOOTRM_MCU Bootloader v2.5.0 Reference.pdf - Figure 2-1. MCU bootloader start-up flowchart).

Can you explain what exactly is going on with WDOG1 before jumping into my application?

In the last post, I referred to Security Reference Manual IMXRT106XSRM.pdf, not Reference Manual IMXRT106XRM.pdf.

Thank you for your help.

Best regards, Jaroslav

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Ok, in that case, thanks for your feedback, we review the datasheet in that point, and we modify it in case it is necessary.

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Carlos,

None of my questions were answered. I have a device in operation that is freezing. I need to know what is the real initialization sequence WDOG1. I can't wait for the new version of the datasheet.

1 - Is the PDE bit reset by the bootloader in ROM?

2 - Do I have to burn the WDOG_ENABLE fuse so that the CPU is still protected by WDOG1? Does the bootloader first stop the POWERDOWN COUNTER and then turn on the TIME-OUT COUNTER in WDOG1 if the WDOG_ENABLE fuse is set? I am using the "FlexSPI (Serial NOR) boot fusemap" boot according to IMXRT106XSRM.pdf.

3 - Muxing Options allows setting to 1 of 5 pins for external signal WDOG1_B according to datashee IMXRT1060RM.pdf. I use GPIO_AD_B1_00 ALT4. When WDOG1 reaches zero in the bootloader, which pin does it pull to zero? Am I able to select the pin for which it pulls from the bootloader (WDOG_B signal)?

4 - What is the real initialization sequence of WDOG1? The processor must be constantly protected by WDOG1 from connecting power.

Thank you for your help.

Best regards, Jaroslav.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We release a new version of MCUXpresso and SDK, did you check your error with this new version?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I checked my error in the latest version of MCUXpresso and SDK on EVK Board. The error also appears in the latest version.

Can someone answer my questions?

1 - Is the PDE bit reset by the bootloader in ROM?

2 - Do I have to burn the WDOG_ENABLE fuse so that the CPU is still protected by WDOG1? Does the bootloader first stop the POWERDOWN COUNTER and then turn on the TIME-OUT COUNTER in WDOG1 if the WDOG_ENABLE fuse is set? I am using the "FlexSPI (Serial NOR) boot fusemap" boot according to IMXRT106XSRM.pdf.

3 - Muxing Options allows setting to 1 of 5 pins for external signal WDOG1_B according to datashee IMXRT1060RM.pdf. I use GPIO_AD_B1_00 ALT4. When WDOG1 reaches zero in the bootloader, which pin does it pull to zero? Am I able to select the pin for which it pulls from the bootloader (WDOG_B signal)?

4 - What is the real initialization sequence of WDOG1? The processor must be constantly protected by WDOG1 from connecting power.

Thank you for your help.

Best regards, Jaroslav.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

1.- in the example, you find the next code

void SystemInit (void) {

#if ((__FPU_PRESENT == 1) && (__FPU_USED == 1))

SCB->CPACR |= ((3UL << 10*2) | (3UL << 11*2)); /* set CP10, CP11 Full Access */

#endif /* ((__FPU_PRESENT == 1) && (__FPU_USED == 1)) */

#if defined(__MCUXPRESSO)

extern uint32_t g_pfnVectors[]; // Vector table defined in startup code

SCB->VTOR = (uint32_t)g_pfnVectors;

#endif

/* Disable Watchdog Power Down Counter */

WDOG1->WMCR &= ~(uint16_t) WDOG_WMCR_PDE_MASK;

WDOG2->WMCR &= ~(uint16_t) WDOG_WMCR_PDE_MASK;

so the WDOG is disable by the systeminit

2.-no, this macro is used by ROM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Carlos,

That is the problem. Power down counter WDOG1 with fixed timeout period of 16 seconds is disable in SystemInit(). Timeout counter WDOG1 is inicialize much later (by void WDOG_Init(WDOG_Type *base, const wdog_config_t *config)).

There will be a big gap when the processor is not protected by WDOG1. So I commented Disable Watchdog Power Down Counter in void SystemInit (void). Power down counter will be disabled by WDOG_Init().

Is signal of Watchdog Power Down Counter routed to external pin of the chip? Wich of pin is it.

Thank you very much.

Jaroslav.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @cerma

On this case, you need to configure the mux in order to select the output as you can see on RM for this example, we have the pin wich you are searching is GPIO_AD_B0_11

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Carlos,

Yes I know. I have already set the pin. I want to know if there is a default value? Does the PowerDown counter set any pin when it expires? Or does the PowerDown counter only do an internal reset (before I assign any pin)?

Best regards, Jaroslav

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

By default, wdogConfig->enablePowerdown = false; you can find more information about the wdog on this excellent blog https://www.cnblogs.com/henjay724/p/16176908.html