- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX RT

- :

- NCache Region Overflow Error

NCache Region Overflow Error

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hı ı am working on imxrt 1052 with custom board. Using Mcuxpresso 11.1.1 and SDK_2.7.0_MIMXRT1052xxxxB . I encountered an error during debug session and ı can not understand what the problem is . I tried to optimize (properties -> setings ->MCU C compiler -> optimization -> optimization level -> optimize for size , optimize for debug (ı tried both)) but error messages not change, only the numberof bytes changed.

void BOARD_ConfigMPU(void)

{

#if defined(__CC_ARM) || defined(__ARMCC_VERSION)

extern uint32_t Image$$RW_m_ncache$$Base[];

/* RW_m_ncache_unused is a auxiliary region which is used to get the whole size of noncache section */

extern uint32_t Image$$RW_m_ncache_unused$$Base[];

extern uint32_t Image$$RW_m_ncache_unused$$ZI$$Limit[];

uint32_t nonCacheStart = (uint32_t)Image$$RW_m_ncache$$Base;

uint32_t size = ((uint32_t)Image$$RW_m_ncache_unused$$Base == nonCacheStart) ?

0 :

((uint32_t)Image$$RW_m_ncache_unused$$ZI$$Limit - nonCacheStart);

#elif defined(__MCUXPRESSO)

extern uint32_t __base_NCACHE_REGION;

extern uint32_t __top_NCACHE_REGION;

uint32_t nonCacheStart = (uint32_t)(&__base_NCACHE_REGION);

uint32_t size = (uint32_t)(&__top_NCACHE_REGION) - nonCacheStart;

#elif defined(__ICCARM__) || defined(__GNUC__)

extern uint32_t __NCACHE_REGION_START[];

extern uint32_t __NCACHE_REGION_SIZE[];

uint32_t nonCacheStart = (uint32_t)__NCACHE_REGION_START;

uint32_t size = (uint32_t)__NCACHE_REGION_SIZE;

#endif

uint32_t i = 0;/* Disable I cache and D cache */

if (SCB_CCR_IC_Msk == (SCB_CCR_IC_Msk & SCB->CCR))

{

SCB_DisableICache();

}

if (SCB_CCR_DC_Msk == (SCB_CCR_DC_Msk & SCB->CCR))

{

SCB_DisableDCache();

}/* Disable MPU */

ARM_MPU_Disable();/* Region 0 setting: Memory with Device type, not shareable, non-cacheable. */

MPU->RBAR = ARM_MPU_RBAR(0, 0x80000000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 2, 0, 0, 0, 0, ARM_MPU_REGION_SIZE_512MB);/* Region 1 setting: Memory with Device type, not shareable, non-cacheable. */

MPU->RBAR = ARM_MPU_RBAR(1, 0x60000000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 2, 0, 0, 0, 0, ARM_MPU_REGION_SIZE_512MB);#if defined(XIP_EXTERNAL_FLASH) && (XIP_EXTERNAL_FLASH == 1)

/* Region 2 setting: Memory with Normal type, not shareable, outer/inner write back. */

MPU->RBAR = ARM_MPU_RBAR(2, 0x60000000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_RO, 0, 0, 1, 1, 0, ARM_MPU_REGION_SIZE_64MB);

#endif/* Region 3 setting: Memory with Device type, not shareable, non-cacheable. */

MPU->RBAR = ARM_MPU_RBAR(3, 0x00000000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 2, 0, 0, 0, 0, ARM_MPU_REGION_SIZE_1GB);/* Region 4 setting: Memory with Normal type, not shareable, outer/inner write back */

MPU->RBAR = ARM_MPU_RBAR(4, 0x00000000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 0, 0, 1, 1, 0, ARM_MPU_REGION_SIZE_128KB);/* Region 5 setting: Memory with Normal type, not shareable, outer/inner write back */

MPU->RBAR = ARM_MPU_RBAR(5, 0x20000000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 0, 0, 1, 1, 0, ARM_MPU_REGION_SIZE_128KB);/* Region 6 setting: Memory with Normal type, not shareable, outer/inner write back */

MPU->RBAR = ARM_MPU_RBAR(6, 0x20200000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 0, 0, 1, 1, 0, ARM_MPU_REGION_SIZE_256KB);/* Region 7 setting: Memory with Normal type, not shareable, outer/inner write back */

MPU->RBAR = ARM_MPU_RBAR(7, 0x80000000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 0, 0, 1, 1, 0, ARM_MPU_REGION_SIZE_32MB);while ((size >> i) > 0x1U)

{

i++;

}if (i != 0)

{

/* The MPU region size should be 2^N, 5<=N<=32, region base should be multiples of size. */

assert(!(nonCacheStart % size));

assert(size == (uint32_t)(1 << i));

assert(i >= 5);/* Region 8 setting: Memory with Normal type, not shareable, non-cacheable */

MPU->RBAR = ARM_MPU_RBAR(8, nonCacheStart);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 1, 0, 0, 0, 0, i - 1);

}/* Enable MPU */

ARM_MPU_Enable(MPU_CTRL_PRIVDEFENA_Msk);/* Enable I cache and D cache */

SCB_EnableDCache();

SCB_EnableICache();

}

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

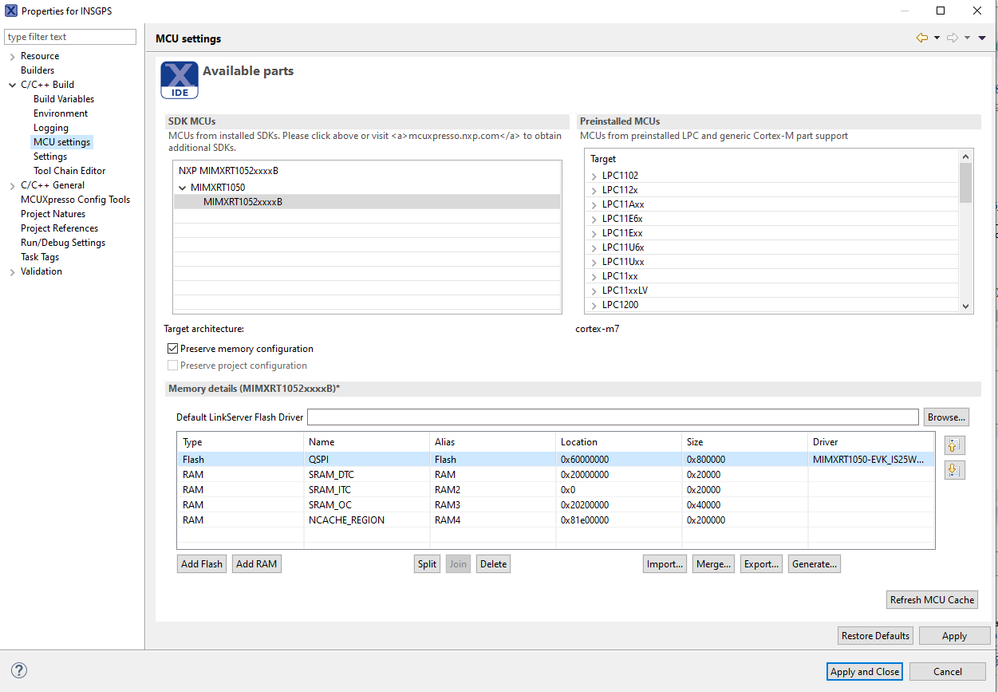

Hi Omer,

It seems you put to much things in NCACHE_REGION. This region is at the end of SDRAM. You can enlarge its size.

Regards,

Jing

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Omer,

It seems you put to much things in NCACHE_REGION. This region is at the end of SDRAM. You can enlarge its size.

Regards,

Jing

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content