- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- i.MX Forums

- :

- i.MX RT

- :

- Moving stack and heap on to SDRAM on IMXRT1021

Moving stack and heap on to SDRAM on IMXRT1021

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Moving stack and heap on to SDRAM on IMXRT1021

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am using imxrt1021 mcu.

IDE: MCUXpresso IDE v11.4.1_6260

SDK: 2.10.0

I am using FreeRTOS. Using a sd card demo example

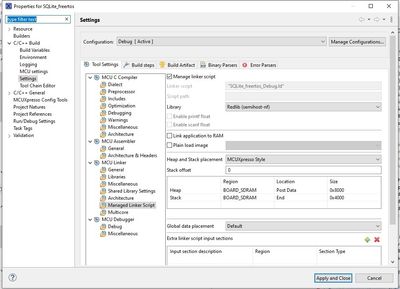

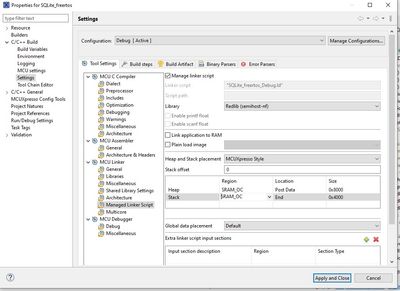

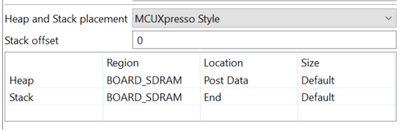

I am trying to move the heap and stack for my project on to SDRAM as i need more heap space.Have changed it in the linker script settings as below

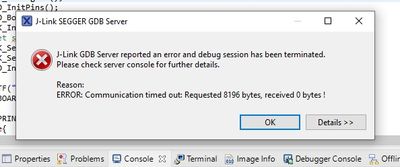

I am able to move it to SRAM_OC this works fine. When i change it to SD_RAM it fails and i get a timeout error.

Did a lot of search but could not find a proper solution for this.

Do i need to set up any other settings?

Can any one please give me some pointers/ reference to some documents on how to change it?

Any help would be much appreciated.

Thanks in advance.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @FelipeGarcia any updates on this. Please do let me know if I have missed out something.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Did you enabled SDRAM before trying to use it? Please check this thread for more details: https://community.nxp.com/t5/i-MX-RT/heap-and-the-stack-on-the-SDRAM-on-MIMXRT1064-Evaluation-Boar/m...

Best regards,

Felipe

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thank you for the response.

Attached is my setting screen shot and BOARD_ConfigMPU configuration.

Please do let me know if i need to modify anything

/* MPU configuration. */

void BOARD_ConfigMPU(void)

{

#if defined(__CC_ARM) || defined(__ARMCC_VERSION)

extern uint32_t Image$$RW_m_ncache$$Base[];

/* RW_m_ncache_unused is a auxiliary region which is used to get the whole size of noncache section */

extern uint32_t Image$$RW_m_ncache_unused$$Base[];

extern uint32_t Image$$RW_m_ncache_unused$$ZI$$Limit[];

uint32_t nonCacheStart = (uint32_t)Image$$RW_m_ncache$$Base;

uint32_t size = ((uint32_t)Image$$RW_m_ncache_unused$$Base == nonCacheStart) ?

0 :

((uint32_t)Image$$RW_m_ncache_unused$$ZI$$Limit - nonCacheStart);

#elif defined(__MCUXPRESSO)

extern uint32_t __base_NCACHE_REGION;

extern uint32_t __top_NCACHE_REGION;

uint32_t nonCacheStart = (uint32_t)(&__base_NCACHE_REGION);

uint32_t size = (uint32_t)(&__top_NCACHE_REGION) - nonCacheStart;

#elif defined(__ICCARM__) || defined(__GNUC__)

extern uint32_t __NCACHE_REGION_START[];

extern uint32_t __NCACHE_REGION_SIZE[];

uint32_t nonCacheStart = (uint32_t)__NCACHE_REGION_START;

uint32_t size = (uint32_t)__NCACHE_REGION_SIZE;

#endif

volatile uint32_t i = 0;

/* Disable I cache and D cache */

if (SCB_CCR_IC_Msk == (SCB_CCR_IC_Msk & SCB->CCR))

{

SCB_DisableICache();

}

if (SCB_CCR_DC_Msk == (SCB_CCR_DC_Msk & SCB->CCR))

{

SCB_DisableDCache();

}

/* Disable MPU */

ARM_MPU_Disable();

/* MPU configure:

* Use ARM_MPU_RASR(DisableExec, AccessPermission, TypeExtField, IsShareable, IsCacheable, IsBufferable,

* SubRegionDisable, Size)

* API in mpu_armv7.h.

* param DisableExec Instruction access (XN) disable bit,0=instruction fetches enabled, 1=instruction fetches

* disabled.

* param AccessPermission Data access permissions, allows you to configure read/write access for User and

* Privileged mode.

* Use MACROS defined in mpu_armv7.h:

* ARM_MPU_AP_NONE/ARM_MPU_AP_PRIV/ARM_MPU_AP_URO/ARM_MPU_AP_FULL/ARM_MPU_AP_PRO/ARM_MPU_AP_RO

* Combine TypeExtField/IsShareable/IsCacheable/IsBufferable to configure MPU memory access attributes.

* TypeExtField IsShareable IsCacheable IsBufferable Memory Attribtue Shareability Cache

* 0 x 0 0 Strongly Ordered shareable

* 0 x 0 1 Device shareable

* 0 0 1 0 Normal not shareable Outer and inner write

* through no write allocate

* 0 0 1 1 Normal not shareable Outer and inner write

* back no write allocate

* 0 1 1 0 Normal shareable Outer and inner write

* through no write allocate

* 0 1 1 1 Normal shareable Outer and inner write

* back no write allocate

* 1 0 0 0 Normal not shareable outer and inner

* noncache

* 1 1 0 0 Normal shareable outer and inner

* noncache

* 1 0 1 1 Normal not shareable outer and inner write

* back write/read acllocate

* 1 1 1 1 Normal shareable outer and inner write

* back write/read acllocate

* 2 x 0 0 Device not shareable

* Above are normal use settings, if your want to see more details or want to config different inner/outter cache

* policy.

* please refer to Table 4-55 /4-56 in arm cortex-M7 generic user guide <dui0646b_cortex_m7_dgug.pdf>

* param SubRegionDisable Sub-region disable field. 0=sub-region is enabled, 1=sub-region is disabled.

* param Size Region size of the region to be configured. use ARM_MPU_REGION_SIZE_xxx MACRO in

* mpu_armv7.h.

*/

/*

* Add default region to deny access to whole address space to workaround speculative prefetch.

* Refer to Arm errata 1013783-B for more details.

*

*/

/* Region 0 setting: Instruction access disabled, No data access permission. */

MPU->RBAR = ARM_MPU_RBAR(0, 0x00000000U);

MPU->RASR = ARM_MPU_RASR(1, ARM_MPU_AP_NONE, 2, 0, 0, 0, 0, ARM_MPU_REGION_SIZE_4GB);

/* Region 1 setting: Memory with Device type, not shareable, non-cacheable. */

MPU->RBAR = ARM_MPU_RBAR(1, 0x80000000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 2, 0, 0, 0, 0, ARM_MPU_REGION_SIZE_512MB);

/* Region 2 setting: Memory with Device type, not shareable, non-cacheable. */

MPU->RBAR = ARM_MPU_RBAR(2, 0x60000000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 2, 0, 0, 0, 0, ARM_MPU_REGION_SIZE_512MB);

#if defined(XIP_EXTERNAL_FLASH) && (XIP_EXTERNAL_FLASH == 1)

/* Region 3 setting: Memory with Normal type, not shareable, outer/inner write back. */

MPU->RBAR = ARM_MPU_RBAR(3, 0x60000000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_RO, 0, 0, 1, 1, 0, ARM_MPU_REGION_SIZE_8MB);

#endif

/* Region 4 setting: Memory with Device type, not shareable, non-cacheable. */

MPU->RBAR = ARM_MPU_RBAR(4, 0x00000000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 2, 0, 0, 0, 0, ARM_MPU_REGION_SIZE_1GB);

/* Region 5 setting: Memory with Normal type, not shareable, outer/inner write back */

MPU->RBAR = ARM_MPU_RBAR(5, 0x00000000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 0, 0, 1, 1, 0, ARM_MPU_REGION_SIZE_64KB);

/* Region 6 setting: Memory with Normal type, not shareable, outer/inner write back */

MPU->RBAR = ARM_MPU_RBAR(6, 0x20000000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 0, 0, 1, 1, 0, ARM_MPU_REGION_SIZE_64KB);

/* Region 7 setting: Memory with Normal type, not shareable, outer/inner write back */

MPU->RBAR = ARM_MPU_RBAR(7, 0x20200000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 0, 0, 1, 1, 0, ARM_MPU_REGION_SIZE_128KB);

/* Region 8 setting: Memory with Normal type, not shareable, outer/inner write back */

MPU->RBAR = ARM_MPU_RBAR(8, 0x80000000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 0, 0, 1, 1, 0, ARM_MPU_REGION_SIZE_32MB);

while ((size >> i) > 0x1U)

{

i++;

}

if (i != 0)

{

/* The MPU region size should be 2^N, 5<=N<=32, region base should be multiples of size. */

assert(!(nonCacheStart % size));

assert(size == (uint32_t)(1 << i));

assert(i >= 5);

/* Region 9 setting: Memory with Normal type, not shareable, non-cacheable */

MPU->RBAR = ARM_MPU_RBAR(9, nonCacheStart);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 1, 0, 0, 0, 0, i - 1);

}

/* Region 10 setting: Memory with Device type, not shareable, non-cacheable */

MPU->RBAR = ARM_MPU_RBAR(10, 0x40000000);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 2, 0, 0, 0, 0, ARM_MPU_REGION_SIZE_4MB);

/* Enable MPU */

ARM_MPU_Enable(MPU_CTRL_PRIVDEFENA_Msk);

/* Enable I cache and D cache */

// SCB_EnableDCache();

// SCB_EnableICache();

}- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thank you for the information provided. However, please make sure SDRAM is enabled in the project first. Are you enabling SDRAM in your project? If so, please share the steps you are following.

Best regards,

Felipe

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I have enabled SDRAM with the MACROS:

XIP_BOOT_HEADER_DCD_ENABLE=1

SKIP_SYSCLK_INIT

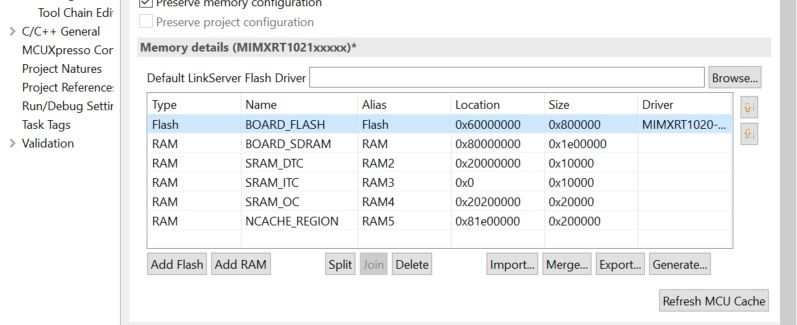

Then have moved the SDRAM to first location after BOARD_FLASH in MCU settings.

And in managed linker script-> have selected SDRAM as region for heap and stack.

Please let me know if i need to enable it in some other locations.

If these steps are not proper please do let me know the flow / please point me to some documentation which i can follow.

Thanks in Advance.!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

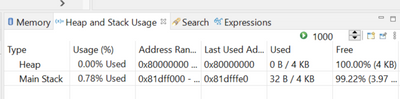

I tested the same and enable SDRAM by adding following compiler options in sdcard_freertos example:

XIP_BOOT_HEADER_DCD_ENABLE=1

SKIP_SYSCLK_INIT

I changed heap and stack to SDRAM.

And I was able to see heap and stack moved to SDRAM location as you can see below

Have a great day,

Felipe

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored. Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am trying out with sdcard_fatfs_freertos sdk demo code.

IDE Version: MCUXpresso IDE v11.4.1_6260

SDK Version: 2.10.0

Detailed Error description:

ERROR: Could not connect to target.

SEGGER J-Link GDB Server V7.54b Command Line Version

JLinkARM.dll V7.54b (DLL compiled Sep 14 2021 16:07:10)

Command line: -nosilent -swoport 2334 -select USB=801036300 -telnetport 2335 -singlerun -endian little -noir -speed auto -port 2336 -vd -device MIMXRT1021DAG5A -if SWD -halt -reportuseraction

-----GDB Server start settings-----

GDBInit file: none

GDB Server Listening port: 2336

SWO raw output listening port: 2334

Terminal I/O port: 2335

Accept remote connection: localhost only

Generate logfile: off

Verify download: on

Init regs on start: off

Silent mode: off

Single run mode: on

Target connection timeout: 0 ms

------J-Link related settings------

J-Link Host interface: USB

J-Link script: none

J-Link settings file: none

------Target related settings------

Target device: MIMXRT1021DAG5A

Target interface: SWD

Target interface speed: auto

Target endian: little

Connecting to J-Link...

J-Link is connected.

Device "MIMXRT1021XXX5A" selected.

Firmware: J-Link EDU Mini V1 compiled Aug 10 2021 11:19:22

Hardware: V1.00

S/N: 801036300

Feature(s): FlashBP, GDB

Checking target voltage...

Target voltage: 3.30 V

Listening on TCP/IP port 2336

Connecting to target...

$$UserActionStart$$: Terms of use

$$UserActionEnd$$: Terms of use

Found SW-DP with ID 0x0BD11477

DPIDR: 0x0BD11477

Scanning AP map to find all available APs

AP[1]: Stopped AP scan as end of AP map has been reached

AP[0]: AHB-AP (IDR: 0x04770041)

Iterating through AP map to find AHB-AP to use

AP[0]: Core found

AP[0]: AHB-AP ROM base: 0xE00FD000

ERROR: DAP error while reading AIRCR.

ERROR: Could not connect to target.

---------------------------------

I noticed that when i import lwip_httpsrv_freertos i see that heap and stack is using SDRAM and the code runs without any error. but when we do this with fatfs_sdcard_freertos this code doesnot get uploaded, I get the above error.

I am also finding out what the issue might be.

Any pointers on this would be much appreciated.

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @FelipeGarcia Could you please share your project so I can test it on my machine and compare the settings?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you.!

will try it out

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

For this you will need to disable the cache, please check this thread for more information.

heap and the stack on the SDRAM on MIMXRT1064 Eval... - NXP Community

Best regards,

Felipe

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored. Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thank you for your response.

I made the changes as mentioned and disabled the cache.

But still getting the same error.