- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX RT

- :

- LCD frame buffer in HyperRAM

LCD frame buffer in HyperRAM

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am using my own design with IMXRT1062. I have connected S70KS1281 hyperram chip to FLEXSPI2 interface. All initialization of hyperram is based on AN12239SW example project.

Hyperram is working, I am able to do read/write test on address range 0x70000000 - 0x71000000 without any errors. But I have problem with LCD frame buffer located in hyperram address range. If I am displaying static picture on the display, it is working well. But if I draw some points and lines to frame area, Image on the display is shifted to the side. I tried to change frame buffer location from hyperram to OC ram, and inside OC ram, the same source code is working well.

I think this is somehow related to switching between read and write operations on flexspi. I am doing a write operations inside main loop. And LCD driver is doing DMA read operations on backgroud.

My function for drawing pixels in main loop is looking like this:

#define LCD_FRAME 0x70800000

void Point(uint16_t color, uint16_t x, uint16_t y)

{

uint32_t addr = LCD_FRAME + (2 * x) + (y * 800 * 2);

*(uint16_t*)addr = color;

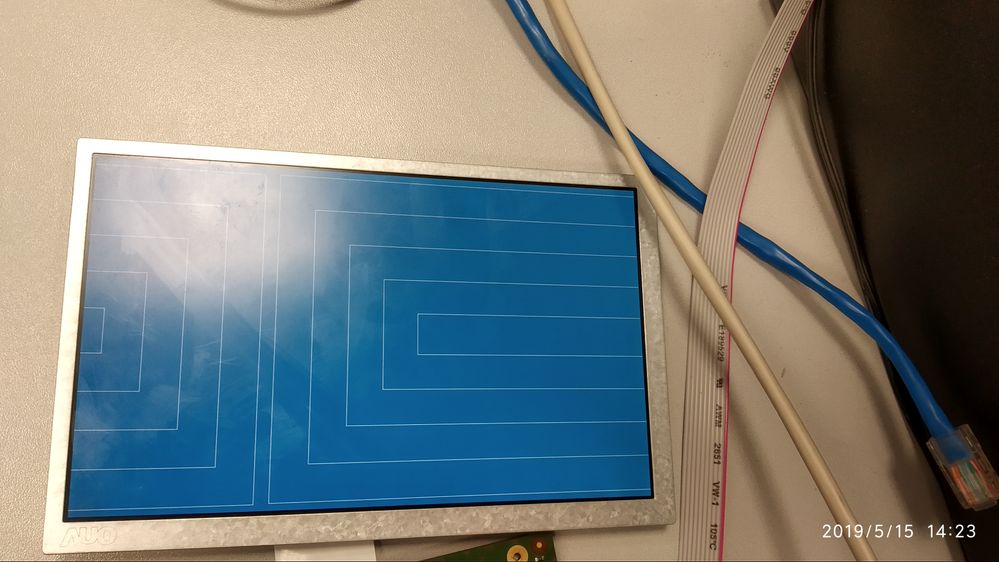

}And I have this result on display:

Then I modified draw function like this:

#define LCD_FRAME 0x70800000

void Point(uint16_t color, uint16_t x, uint16_t y)

{

while (!FLEXSPI_GetBusIdleStatus(FLEXSPI2))

{

}

uint32_t addr = LCD_FRAME + (2 * x) + (y * 800 * 2);

*(uint16_t*)addr = color;

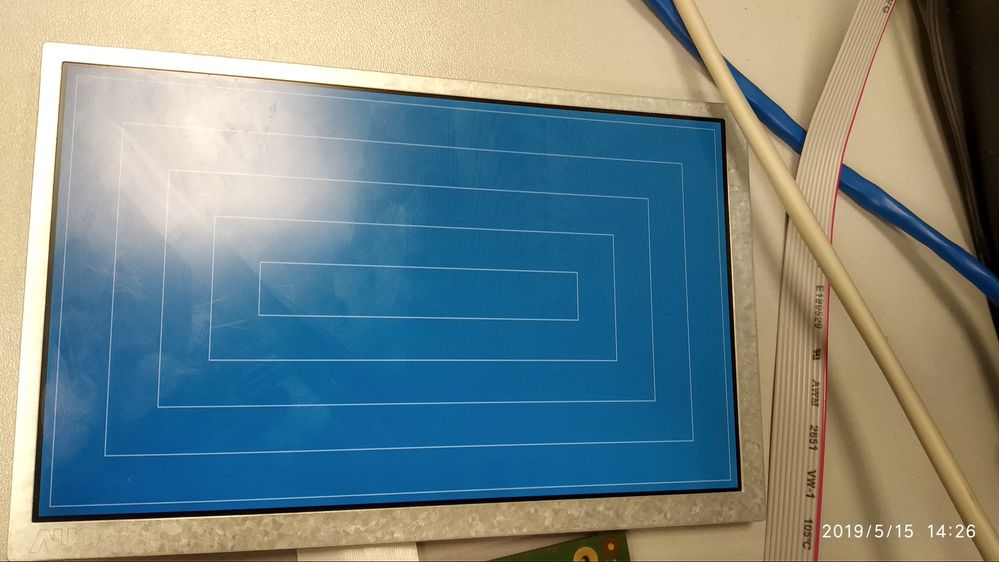

}And it solved the problem:

But I think this is not good solution. I think DMA controller should take care about this conflicts automatically...

This is my MPU configuration, maybe there is a problem, I donk know. I tried all permutations of MPU settings without luck. Region 8 is hyperram nocache area used for frame buffer:

/* MPU configuration. */

void BOARD_ConfigMPU(void)

{

/* Disable I cache and D cache */

if (SCB_CCR_IC_Msk == (SCB_CCR_IC_Msk & SCB->CCR))

{

SCB_DisableICache();

}

if (SCB_CCR_DC_Msk == (SCB_CCR_DC_Msk & SCB->CCR))

{

SCB_DisableDCache();

}

/* Disable MPU */

ARM_MPU_Disable();

/* MPU configure:

* Use ARM_MPU_RASR(DisableExec, AccessPermission, TypeExtField, IsShareable, IsCacheable, IsBufferable,

* SubRegionDisable, Size)

* API in core_cm7.h.

* param DisableExec Instruction access (XN) disable bit,0=instruction fetches enabled, 1=instruction fetches

* disabled.

* param AccessPermission Data access permissions, allows you to configure read/write access for User and

* Privileged mode.

* Use MACROS defined in core_cm7.h:

* ARM_MPU_AP_NONE/ARM_MPU_AP_PRIV/ARM_MPU_AP_URO/ARM_MPU_AP_FULL/ARM_MPU_AP_PRO/ARM_MPU_AP_RO

* Combine TypeExtField/IsShareable/IsCacheable/IsBufferable to configure MPU memory access attributes.

* TypeExtField IsShareable IsCacheable IsBufferable Memory Attribtue Shareability Cache

* 0 x 0 0 Strongly Ordered shareable

* 0 x 0 1 Device shareable

* 0 0 1 0 Normal not shareable Outer and inner write

* through no write allocate

* 0 0 1 1 Normal not shareable Outer and inner write

* back no write allocate

* 0 1 1 0 Normal shareable Outer and inner write

* through no write allocate

* 0 1 1 1 Normal shareable Outer and inner write

* back no write allocate

* 1 0 0 0 Normal not shareable outer and inner

* noncache

* 1 1 0 0 Normal shareable outer and inner

* noncache

* 1 0 1 1 Normal not shareable outer and inner write

* back write/read acllocate

* 1 1 1 1 Normal shareable outer and inner write

* back write/read acllocate

* 2 x 0 0 Device not shareable

* Above are normal use settings, if your want to see more details or want to config different inner/outter cache

* policy.

* please refer to Table 4-55 /4-56 in arm cortex-M7 generic user guide <dui0646b_cortex_m7_dgug.pdf>

* param SubRegionDisable Sub-region disable field. 0=sub-region is enabled, 1=sub-region is disabled.

* param Size Region size of the region to be configured. use ARM_MPU_REGION_SIZE_xxx MACRO in

* core_cm7.h.

*/

/* Region 0 setting: Memory with Device type, not shareable, non-cacheable. */

MPU->RBAR = ARM_MPU_RBAR(0, 0xC0000000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 2, 0, 0, 0, 0, ARM_MPU_REGION_SIZE_512MB);

/* Region 1 setting: Memory with Normal type, not shareable, non-cacheable. */

MPU->RBAR = ARM_MPU_RBAR(1, 0x70000000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 0, 0, 1, 1, 0, ARM_MPU_REGION_SIZE_1GB);

/* Region 2 setting */

#if defined(XIP_EXTERNAL_FLASH) && (XIP_EXTERNAL_FLASH == 1)

/* Setting Memory with Normal type, not shareable, outer/inner write back. */

MPU->RBAR = ARM_MPU_RBAR(2, 0x60000000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_RO, 0, 0, 1, 1, 0, ARM_MPU_REGION_SIZE_8MB);

#else

/* Setting Memory with Device type, not shareable, non-cacheable. */

MPU->RBAR = ARM_MPU_RBAR(2, 0x60000000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_RO, 2, 0, 0, 0, 0, ARM_MPU_REGION_SIZE_8MB);

#endif

/* Region 3 setting: Memory with Device type, not shareable, non-cacheable. */

MPU->RBAR = ARM_MPU_RBAR(3, 0x00000000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 2, 0, 0, 0, 0, ARM_MPU_REGION_SIZE_1GB);

/* Region 4 setting: Memory with Normal type, not shareable, outer/inner write back */

MPU->RBAR = ARM_MPU_RBAR(4, 0x00000000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 0, 0, 1, 1, 0, ARM_MPU_REGION_SIZE_128KB);

/* Region 5 setting: Memory with Normal type, not shareable, outer/inner write back */

MPU->RBAR = ARM_MPU_RBAR(5, 0x20000000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 0, 0, 1, 1, 0, ARM_MPU_REGION_SIZE_128KB);

/* Region 6 setting: Memory with Normal type, not shareable, outer/inner write back */

MPU->RBAR = ARM_MPU_RBAR(6, 0x20200000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 0, 0, 1, 1, 0, ARM_MPU_REGION_SIZE_512KB);

/* Region 7 setting: Memory with Normal type, not shareable, outer/inner write back */

MPU->RBAR = ARM_MPU_RBAR(7, 0x20280000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 0, 0, 1, 1, 0, ARM_MPU_REGION_SIZE_256KB);

/* Region 8 setting: Memory with Normal type, noncache, */

MPU->RBAR = ARM_MPU_RBAR(8, 0x70800000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 1, 0, 0, 0, 0, ARM_MPU_REGION_SIZE_8MB);

/* Enable MPU */

ARM_MPU_Enable(MPU_CTRL_PRIVDEFENA_Msk);

/* Enable I cache and D cache */

SCB_EnableDCache();

SCB_EnableICache();

}Does anyone understand this problem? It is possible to use hyperram for LCD frame buffer?

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

First of all, sorry for the later reply.

It looks ARM Core and DMA arbitrate FlexSPI2 memory resource at same time.

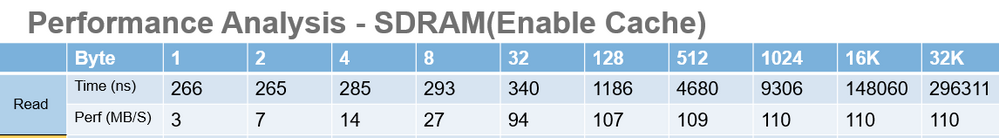

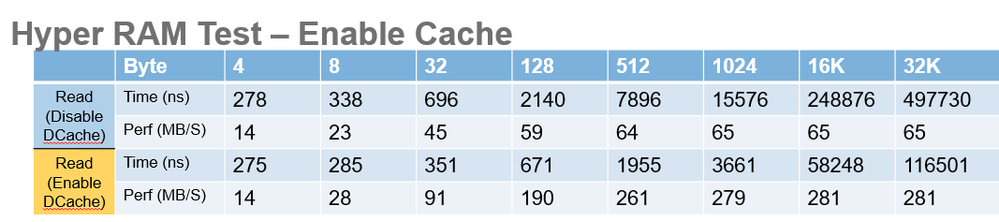

From memory performance benchmark, SDRAM/Hyper RAM/Hyper Flash/Octal Flash nearly has the similar performance.

So, using hyper ram as LCD frame buffer should be ok.

It need to balance ARM core and DMA access hyper ram time slot.

Customer also could change NIC-301 SIM-M7 register to set ARM core and DMA access priority.

Wish it helps.

Have a great day,

Mike

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am using RT1060 EVKB + HyperRAM (S27KS0642) + emWin. SDK 2.13.0

HyperRAM works, but issue the same: evkmimxrt1060_emwin_slide_show compiled to run from HypeRAM and screen buffers in HyperRAM - results in shifted screen content. Besides during animation there are even more distractions.

So far I founs out that if emWin library shifted by multiple of 4 bytes (depends on code amount before libemWin_M7.a code in final binary) within 32 byte range hits the "lucky" address, then there is no shift but animation frame rate is very low (~3fps).

And I tried everything described above and more. I suspect that this is something to do with FlexSPI configuration though.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

First of all, sorry for the later reply.

It looks ARM Core and DMA arbitrate FlexSPI2 memory resource at same time.

From memory performance benchmark, SDRAM/Hyper RAM/Hyper Flash/Octal Flash nearly has the similar performance.

So, using hyper ram as LCD frame buffer should be ok.

It need to balance ARM core and DMA access hyper ram time slot.

Customer also could change NIC-301 SIM-M7 register to set ARM core and DMA access priority.

Wish it helps.

Have a great day,

Mike

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

thanks for answer.

Dafault priority settings after reset is (higher number is higher priority):

LCD 1

PXP 2

CSI 4

Cortex-M7 4

DMA 3

I change LCD priority from 1 to 5 and it solve the problem. Or decreasing Cortex-M7 form 4 to 0 also solve the problem.

But why is default priority of LCD lowest of them?

And why is the default setting funcional with SDRAM but not with Hyperram?

I want to use LCD and also CSI in my project. What priority settings do you reccomend? Higher for LCD or higher for CSI?

And I also enabled RECOVER_ON_UNDERFLOW configuration bit in LCDIF_CTRL1 register.

If this bit is disabled, problem with LCD priority make permanent shift of the picture on display.

With this bit enabled, picture on display is corrected in the next frame.

Regards,

Peter.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Peter,

The NIC-301 default master priority setting is just for reference.

Customer can change related master priority level based on real application.

The default LCD with lowest priority, for not every RT1060 application with LCD display.

The default function with SDRAM, not HyperRAM, which is also just for a reference.

If there using both CSI and LCD with HyperRAM interface, we would recommend to set CSI with lower priority than LCD to access Hyperram memory.

The reason is we tested hyperram write speed is higher than read operation with cache disabled.

The RECOVER_ON_UNDERFLOW bit enabled in LCDIF_CTRL1 register will load LCD frame buffer data again when underflow issue happened. That will recover LCD display if Hyperram bandwidth is arbitrated by LCD and ARM core.

Thanks for the attention.

Have a great day,

Mike

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

unfortunately this problem is still not solved. It looks like some problem with priority arbiter or something like that. Combination of LCD and CSI in hyperram is working very badly.

My actual configuration is:

LCD priority = 6, CSI priority = 5, Cortex-M7 priority = 4,

MPU cache is disabled,

FLEXSPI2 1KB prefetch buffer enabled and splitted into 4 separate buffers (4 x 256B) for each master ID.

So, I should have separate prefetch buffer for LCD and separate prefetch buffer for memcpy (Cortex-M7). If I am doing memcpy read from hyperram to OC ram, LCD ans CSI is enabled at this time, it gives me AHBCMDERR flag and LCD_BM_ERROR flag. Picture on display is corrupted.

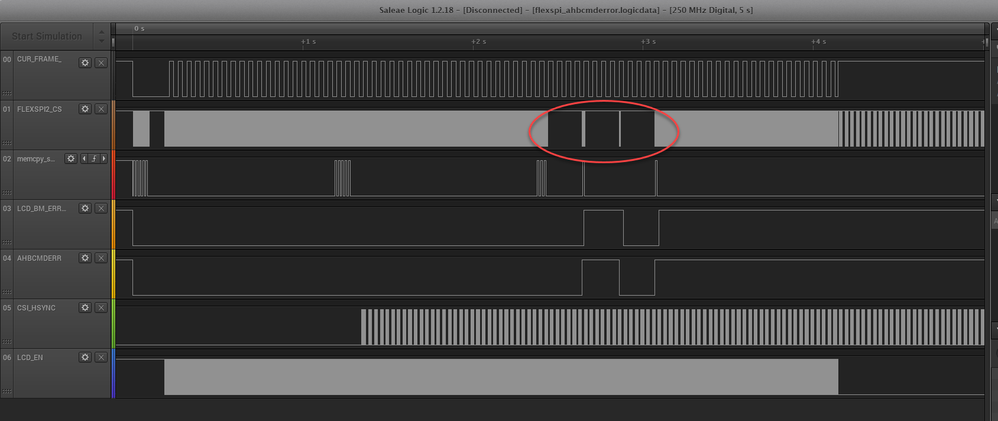

Please look at my captured data (using saleae logic analyzer) and source code:

Test routine is called "lcd_test()". Signals FLEXSPI2_CS, CSI_HSYNC, LCD_EN are signals taken directly from PCB. Rest of signals are toggled by my software in interrupt handlers. As you can see in captured data, there is 200ms empty space (located 2.4second from begin) of FLEXSPI2_CS signal. This is the point when errors are ocurred.

Regards,

Peter

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Peter,

First of all, sorry for the later reply.

What's the FlexSPI Flash operation frequency?

There are some configurations could affect HyperRAM performance:

- Cache Impact

RT1050/60 support max 32K DCACHE and 32KICACHE, it can improve the performance more after enable cache.

- Prefetch Buffer Impact

RT1050/60 support 1024KB prefetch buffer, its policy as below:

- available to configure buffer to specified master or multiply master share the same buffer.

- Automatically prefetch data to buffer till buffer is full.

- Try to check if hit prefetched address range , if it is out of range, trigger the new read operation from FlexSPI device, otherwise, if it has been in prefetch buffer, read it from AHB buffer, if not, waiting for prefetching data to buffer.

So it has the different configuration base on application.

- if each data access is small size and access address is not continuous, suggest set smaller prefetch buffer size.

- If it is continuous address access, suggest to set big prefetch buffer size.

From our internal HyperRAM test performance, we with below recommendation:

- Enabling cache to improve Hyper RAM performance more.

Wish it helps.

Have a great day,

Mike

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I already do alot of tests with enabling/disablig DCACHE and configuring prefetch buffers. It is fast enough for my purpose. Speed is not the main problem.

I am using setting with 4 separate prefetch buffers for each master ID. So, I have separate prefetch buffer for LCD reading and separate buffer for "memcpy" reading from RAM.

As you can see in my attachment in file "flexspi_ahbcmderror.logicdata". It is working fine at the begin, where I am using only LCD. Later I activate LCD (reading from RAM), CSI (writing to RAM) and memcpy (reading from RAM) and there is 200ms empty space where whole hyperram just did not work. CS signal is in inactive state but memcpy function in main loop is running at this point. Also AHBCMDERR errog flag is active in this time.

Regards,

Peter

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

First of all, I am sorry for the so later reply.

Could you provide FlexSPI2 all registers value during test?

And please using below register setting with FlexSPI2 module:

AHB Bus Control Register (AHBCR)'s bit 6 [READADDROPT] set to 1b;

Flash Control Register 4 (FLSHCR4)'s bit 0 [WMOPT1] clear to 0b;

bit 2 [WMENA] set to 1b;

bit 3 [WMENB] set to 1b;

Wish it helps.

Have a great day,

Mike

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

original values are:

READADDROPT = 0, WMOPT1 = 0, WMENA = 1, WMENB = 0,

There is memory image started at 0x402a400:

30 30 FF FF FF FF FF FF F7 01 08 20 38 00 00 00 00 00 00 00 50 08 00 00 F0 5A F0 5A 01 00 00 00

20 00 00 80 20 00 01 80 20 00 02 80 20 00 03 80 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

00 40 00 00 00 00 00 00 00 00 00 00 00 00 00 00 04 1C 02 00 63 00 00 00 63 00 00 00 63 00 00 00

00 01 00 00 00 00 00 00 00 00 00 00 00 00 00 00 0C 0C 00 0D 04 00 00 00 00 00 00 00 00 00 00 00

00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

79 00 00 00 00 01 00 00 02 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

03 00 00 00 00 0E 00 00 2B 09 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

0D 81 0D 81 00 00 00 00 23 8A 60 4E 18 11 0C D9 68 E1 37 C0 3D 41 78 8F C7 92 7A 78 A5 FE 11 AA

FF 63 CE F8 5D 86 6E 73 8F 7D B0 AC 88 0B 18 F5 61 8F 1C 72 8F F9 B9 9D 51 FF BD 23 09 CC 7E 6B

EE 72 C1 30 04 2F 31 C5 CC 98 FE C1 60 B9 DD 12 89 09 12 82 98 49 0A E2 57 68 48 A7 21 A0 21 A4

07 31 B7 E6 27 C8 E3 FA C4 0D 8E 5F 20 F0 CE C6 4D 8F 6B 8E 36 08 51 A5 69 85 77 D1 1D E2 7F 9C

00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00I change configuration to this:

READADDROPT = 1, WMOPT1 = 0, WMENA = 1, WMENB = 1,

But problem still persist.

Didi you think that this have a solution?

I need to decide if I should continue with Hyperram or change my design to SDRAM and then use some secondary procesor to expand GPIO pins.

Regards,

Peter.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

This thread is super old, but I wanted to ask if you ever got this working smoothly?

I'm working on a very similar application where I have a video source that I need to capture, buffer, maybe do some simple operations on like adding an overlay and finally displaying it on an LCD. I'm also using hyperram in order to save pins on the SoC.

Configuring the read / write QoS in NIC-301 sim registers solved the first major issue I had, but right now I'm only generating test patterns and not yet using the CSI. So I was wondering if you ever got that to work, because I feel like I'm already pushing it without even using the CSI.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Peter,

From our internal test result, the HyperRAM performance versus SDRAM, which SDRAM read throughput rate (ARM core read) is slower than HyperRAM:

HyperRAM MPU config:

non-shareable

Cacheable

Write back

Enable Dcache

best regards,

Mike

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Peter,

First of all, sorry for the later reply.

From your provide "flexspi_ahbcmderror.logicdata", the HyperRAM stop working during the third memcpy.

I am checking with i.MXRT product team about this issue.

Thanks for the patience.

best regards,

Mike