- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX RT

- :

- Re: Is the performance of FlexSPI better if we connect one flash to Port A and one to Port B?

Is the performance of FlexSPI better if we connect one flash to Port A and one to Port B?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I have already asked a question about FlexSPI here: Can we use a XIP flash and a data flash at the same FlexSPI controller?

The answer there was that using XIP on port A and saving data on port B will not reduce the performance a lot.

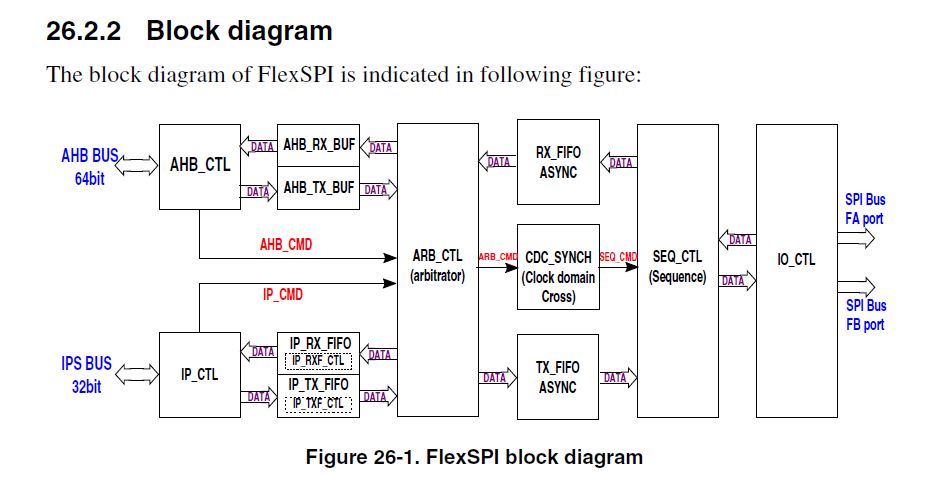

The block diagram from RT1020 Reference Manual

looks like port A and port B share the complete FlexSPI logic.

There is only one ARB_CTL block and only one SEQ_CTL block so even if reading is done with AHB bus and writing with IP bus it is only possible to communicate with port A flash or port B flash at a time and not with both at the same time right?

If we now connect the data flash from port B as a second flash on port A we would only need the additional FLEXSPI_A_SS1_B Pin and save pins from port B.

Will connecting both flashes at port A reduce the performance compared to XIP on port A and data on port B?

Kind regards,

Stefan

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for your reply.

1) Did they give you an explanation of why it is recommended to use port A and port B for RWW?

-- It would the software more complicated, it's not friendly to the developer.

2) Does ROM configure flash B1 on boot? If yes which chip select pin does it use?

-- No.

3) & )4

-- No.

5) In AN12564 page 4 is written that "the common code for flash erase API function is also available for RWW implement, it is available in SDK package". Where can I find this API for RT1020 - I can not find it in the SDK documentation for RT1020.

-- In the flexspi (~\SDK_2.7.0_EVK-MIMXRT1020\boards\evkmimxrt1020\driver_examples\flexspi)demo project.

6) Why does a CPU transfer result in a hard fault?

-- The CPU prefetch the code via 64bit AHB Bus (i.e. AHB command), code program calls FlexSPI driver to erase or program Data Flash via 32bit IPS Bus (i.e. IP IP command).

The ARB_CTL arbitrator will determine which kind of command will preemptive the control to be the ARB command when they both want to handle the flash. And only one command is serviced at that time.

7) Is it possible to let the CPU do other stuff (e.g. interrupt handling, calculations,...) while DMA is transferring page data to flash B1 for programming? AN12564 page 5 figure 5 flash program flowchart disables interrupts until FlexSPI bus is idle again.

-- Yes, it's possible. However, it needs to remap the code to RAM to execute.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for your interest in NXP Semiconductor products and for the opportunity to serve you.

1) There is only one ARB_CTL block and only one SEQ_CTL block so even if reading is done with AHB bus and writing with IP bus it is only possible to communicate with port A flash or port B flash at a time and not with both at the same time right?

-- Yes.

2) If we now connect the data flash from port B as a second flash on port A we would only need the additional FLEXSPI_A_SS1_B Pin and save pins from port B.

-- No, I'm afraid it's impossible.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jeremy,

thank you for you answer.

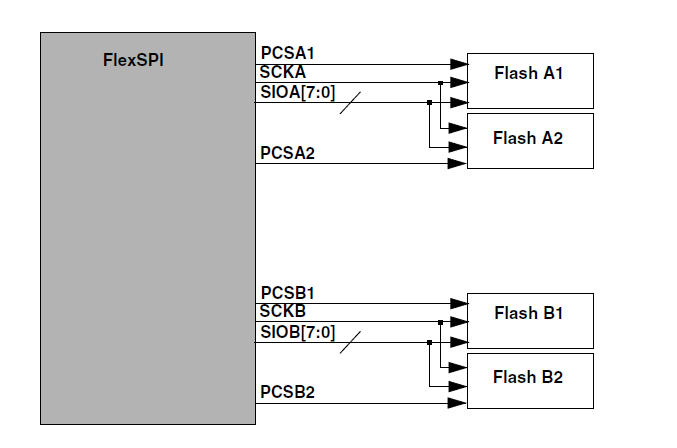

In the reference manual you can find this diagram

which looks like you can connect two flash devices to port A and two to port B.

Why is it not possible to connect two QSPI flashes to port A?

If it is possible: Will connecting both flashes at port A reduce the performance compared to XIP on port A and data on port B?

Kind regards,

Stefan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Stefan,

Thanks for your reply.

The FlexSPI port can connect the two external flash chips when code runs in neither of them.

Hope this is clear.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jeremy,

so you are saying:

- Flash A1 for XIP and A2 for data will not work?

- Does Flash A1 for XIP and B1 for data work?

- Is it possible to XIP from Hyperflash if you use Cypress Hyperflash and additionally Cypress Hyperram on FlexSPI?

Kind regards,

Stefan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Stefan,

Thanks for your reply.

1) Flash A1 for XIP and A2 for data will not work?

-- Yes.

2) Does Flash A1 for XIP and B1 for data work?

-- Yes.

3) Is it possible to XIP from Hyperflash if you use Cypress Hyperflash and additionally Cypress Hyperram on FlexSPI?

-- Yes, however they shouldn't connect the same port of the FlexSPI.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jeremy,

The software of Application Note AN12564 shows how to implement 2 QSPI Flash on port A of RT1060 and it seems that it is also working on RT1020 (partly, I think there are some bugs in the example e.g. always waiting for busy flash A1 instead of the programmed flash A2).

Could you please explain why you think that we can not use XIP on A1 and data on A2?

3) Is it possible to XIP from Hyperflash if you use Cypress Hyperflash and additionally Cypress Hyperram on FlexSPI?

-- Yes, however they shouldn't connect the same port of the FlexSPI.

This would mean that you never can use both with RT1020 and RT1050 at the same time because to get the Cypress Hyperflash/ram working on these processors you have to combine port A and port B to Octal Mode -> no separate ports left.

Kind regards,

Stefan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for your reply.

1) Could you please explain why you think that we can not use XIP on A1 and data on A2?

-- After confirming with the AE team, the AN12564 actually provides a way to implement RWM function when connecting Flash A1 and Flash A2 to port A of FlexSPI, and it should due to the DMA transmit function.

However, the AE team recommend to the developer to connect flash A1 and flash B1 to port A and port B respectively to implement the RWW function.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Jeremy,

thank you for your help. I have still some questions.

- Did they give you an explanation why it is recommended to use port A and port B for RWW? The separation needs more PINs of the MCU (additional data strobe for pad loopback and clock)?

- Does ROM configure flash B1 on boot? If yes which chip select pin does it use?

- Is there a way to set flash device configuration

flexspi_device_config_t deviceconfig = {

during boot instead of updating FlexSPI in main() which requires a FlexSPI reset and RAM for function allocation?

.flexspiRootClk = 133000000,

.flashSize = FLASH_SIZE,

.CSIntervalUnit = kFLEXSPI_CsIntervalUnit1SckCycle,

.CSInterval = 2,

.CSHoldTime = 3,

.CSSetupTime = 3,

.dataValidTime = 0,

.columnspace = 0,

.enableWordAddress = 0,

.AWRSeqIndex = 0,

.AWRSeqNumber = 0,

.ARDSeqIndex = NOR_CMD_LUT_SEQ_IDX_READ_FAST_QUAD,

.ARDSeqNumber = 1,

.AHBWriteWaitUnit = kFLEXSPI_AhbWriteWaitUnit2AhbCycle,

.AHBWriteWaitInterval = 0,

}; - Is there a way to set these settings

/*Get FLEXSPI default settings and configure the flexspi. */

FLEXSPI_GetDefaultConfig(&config);

/*Set AHB buffer size for reading data through AHB bus. */

config.ahbConfig.enableAHBPrefetch = true;

config.ahbConfig.enableAHBBufferable = true;

config.ahbConfig.enableReadAddressOpt = true;

config.ahbConfig.enableAHBCachable = true;

config.rxSampleClock = kFLEXSPI_ReadSampleClkLoopbackFromDqsPad;

config.enableSameConfigForAll = true;

FLEXSPI_Init(base, &config);

during boot by boot-ROM instead of calling the function in main (which again requires FlexSPI reset)? - In AN12564 page 4 is written that "the common code for flash erase API function is also available for RWW implement, it is available in SDK package". Where can I find this API for RT1020 - I can not find it in the SDK documentation for RT1020.

- In AN12564 page 4 is written

"For flash programming, as it only has one FlexSPI interface, so if the CPU transfers the data, it generates the hard fault. To avoid this issue, one way is to use DMA for data transfer instead CPU."

Why does a CPU transfer result in a hard fault? What are other ways instead of using DMA? - Is it possible to let the CPU do other stuff (e.g. interrupt handling, calculations,...) while DMA is transferring page data to flash B1 for programming? AN12564 page 5 figure 5 flash program flowchart disables interrupts until FlexSPI bus is idle again.

Kind regards,

Stefan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for your reply.

1) Did they give you an explanation of why it is recommended to use port A and port B for RWW?

-- It would the software more complicated, it's not friendly to the developer.

2) Does ROM configure flash B1 on boot? If yes which chip select pin does it use?

-- No.

3) & )4

-- No.

5) In AN12564 page 4 is written that "the common code for flash erase API function is also available for RWW implement, it is available in SDK package". Where can I find this API for RT1020 - I can not find it in the SDK documentation for RT1020.

-- In the flexspi (~\SDK_2.7.0_EVK-MIMXRT1020\boards\evkmimxrt1020\driver_examples\flexspi)demo project.

6) Why does a CPU transfer result in a hard fault?

-- The CPU prefetch the code via 64bit AHB Bus (i.e. AHB command), code program calls FlexSPI driver to erase or program Data Flash via 32bit IPS Bus (i.e. IP IP command).

The ARB_CTL arbitrator will determine which kind of command will preemptive the control to be the ARB command when they both want to handle the flash. And only one command is serviced at that time.

7) Is it possible to let the CPU do other stuff (e.g. interrupt handling, calculations,...) while DMA is transferring page data to flash B1 for programming? AN12564 page 5 figure 5 flash program flowchart disables interrupts until FlexSPI bus is idle again.

-- Yes, it's possible. However, it needs to remap the code to RAM to execute.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for your answer jeremy!

Kind regards,

Stefan