- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX RT

- :

- Re: IMXRT1050 noncached RAM above 0x20240000 for DMA

IMXRT1050 noncached RAM above 0x20240000 for DMA

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

IMXRT1050 noncached RAM above 0x20240000 for DMA

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

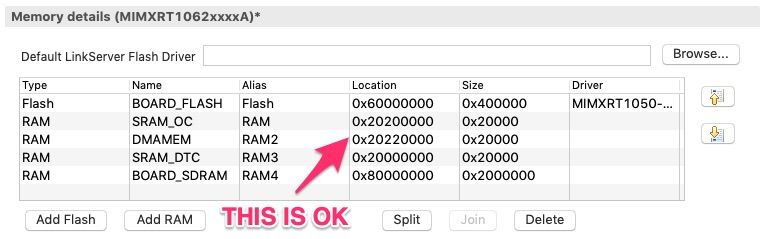

I am trying to configure an area of FlexRAM for DMA buffers in MCUXpresso IDE 11.0 for the i.MXRT1050/1060

When I choose the starting address as 0x20220000 and a size of 0x20000 it works as expected (for DMA).

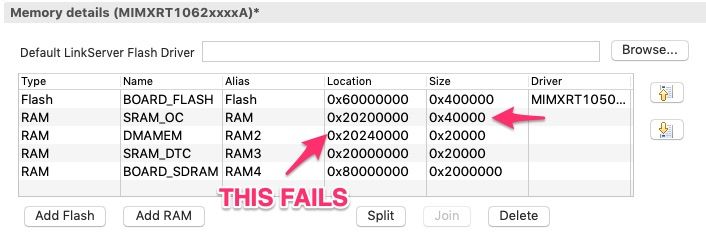

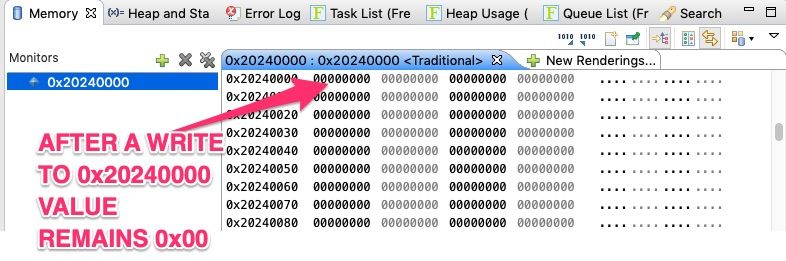

If I choose to start the region at 0x20240000 (size 0x20000), it seems that any writes to the region don't succeed, but no errors are thrown. Looking in the memory monitor, the locations are all 0x00 (initialized).

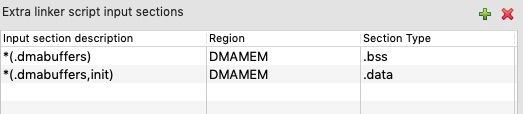

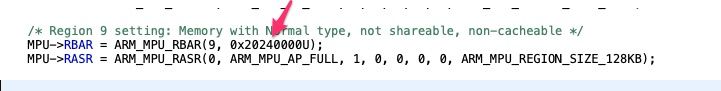

I also make the appropriate changes to the MPU config for the region and the section definition in the linker:

Then I assign the buffer to the DMA region with the following:

DMAMEM_ALIGN( uint8_t buffer[3200], 4);with:

#define DMAMEM_ALIGN(var, alignbytes) \

__attribute__((section(".dmabuffers"))) var __attribute__((aligned(alignbytes)))Again, this all works if the region is at address 0x20220000...

Any ideas?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jack King ,

Thank you for your interest in NXP Semiconductor products and

for the opportunity to serve you.

It seems a bit weird, I'd like to know more information about the phenomenon, so I was wondering if you can share the demo project, in addition, introduce the complete testing process in details.

Looking forward to your reply.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Jeremy,

Sure, here are two identical basic projects from MCUXpresso 11.0 that test WRITE/READ to the memory region.

One uses 0x20220000 and the other uses 0x20240000

The one using 0x20240000 fails to read back what was written (memory remains 0x00).

The one using 0x20220000 succeeds.

I am using an Embedded Artists board, so you may need to change the XIP flash driver.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jack King ,

Thanks for your reply.

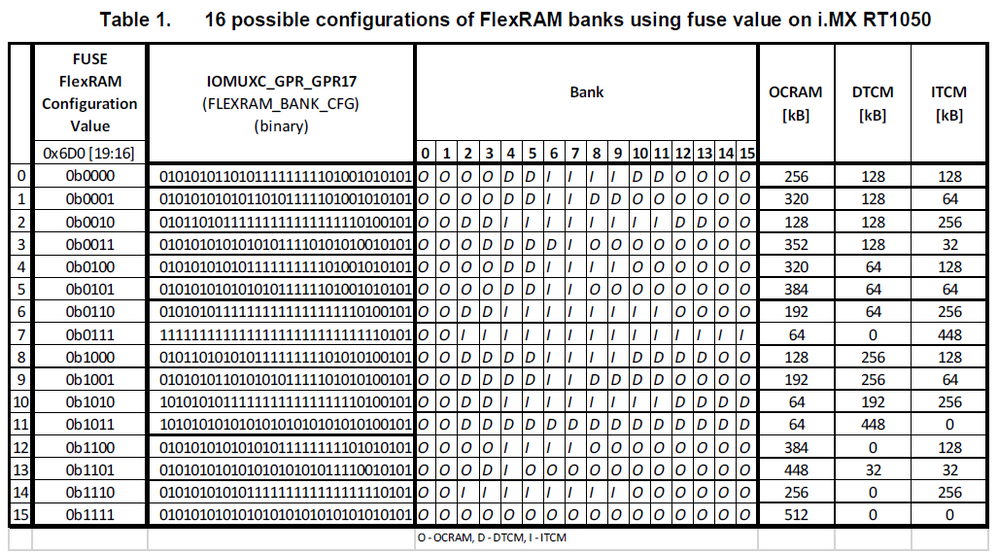

In the RT series, the FlexRAM is a highly configurable and flexible RAM memory array. This memory array contains

memory banks which can be independently configured to be accessed by a different type of interfaces, such as I-TCM (Instruction-Tightly Coupled Memory), D-TCM (Data- Tightly Coupled Memory), or

AXI (system). The memory bank can act as an ITCM, DTCM, or OCRAM memory.

Table 1 illustrates the different configurations of FlexRAM banks.

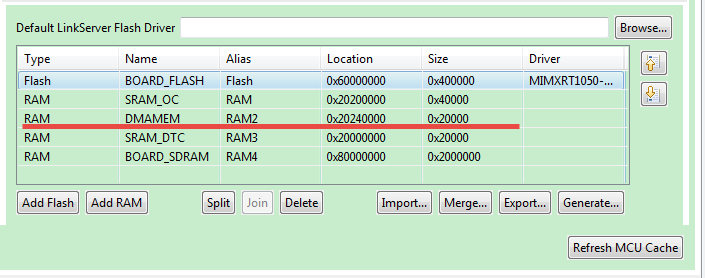

According to Table 1, we can find that the default size of the OCRAM is 256 KB which is equal to 0x40000, so the DMAMEM area is definitely beyond the range of the OCRAM as the Fig 1 shows.

Fig 1

I think it's the root cause of your issue.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

That table states that OCRAM can be as large as 384kB, so 0x40000 + 0x20000 should be ok for the total OCRAM size.

EDIT: Oh WOW... I think I totally misunderstand some fundamental things about FlexRAM... It looks like the default behaviour is to use the FUSE settings for FlexRAM configuration. Which is:

I thought that changing the MCU settings for memory details in MCUXpresso actually *reconfigured* FlexRAM... apparently it does NOT.

The MCU settings only reconfigure memory within the FlexRAM sizes set by the fuses (by default).

To change the defined FlexRAM sizes, either the fuses have to be set differently or the FlexRAM has to be explicitly reconfigured in software.

I see that there is an SDK example that shows actually reconfiguring FlexRAM with software, I will try this example and see if I can get past my original issue. But this fundamental misunderstanding has caused many hours of frustration with other issues as well!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

OK, so I tested again after doing a software reconfiguration of FlexRAM with the following:

static status_t OCRAM_Reallocate(void)

{

flexram_allocate_ram_t ramAllocate = {

.ocramBankNum = 12,

.dtcmBankNum = 0,

.itcmBankNum = 4,

};

if (FLEXRAM_AllocateRam(&ramAllocate) != kStatus_Success)

{

return kStatus_Fail;

}

return kStatus_Success;

}

...

#if defined(__DCACHE_PRESENT) && __DCACHE_PRESENT

SCB_DisableDCache();

#endif

/* reallocate ram */

OCRAM_Reallocate();

/* init flexram */

FLEXRAM_Init(FLEXRAM);

#if defined(__DCACHE_PRESENT) && __DCACHE_PRESENT

SCB_EnableDCache();

#endifThis works, although the J-Link debugger fails to connect every second launch when doing this. I have to wipe the XIP flash and reconnect the debugger to get it working again, then it will fail on the second launch again... This is using MCUX 11.0.1 and J-Link V651b, but it happens on MCUX 11.0.0 and J-Link V646k as well.