- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- i.MX Forums

- :

- i.MX RT

- :

- IMXRT LPSPI. How to reduce delay between FIFO transfers?

IMXRT LPSPI. How to reduce delay between FIFO transfers?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi all,

I have to transmit a big data burst through LPSPI (76800 transfers, each transfer contains 4 9-bit packets). To get all data sent as fast as possible, I am writting in the FIFO as quick as possible (as far as I know though):

do

{

/*Fill the FIFO with 4 frames*/

LPSPI_WriteData(LPSPI1_PERIPHERAL, (uint16_t)(0x22)); //COMMAND Byte

LPSPI_WriteData(LPSPI1_PERIPHERAL, (uint16_t)(0x0100 + (uint8_t)(logoData[logoIndex] >> 8))); //RED

LPSPI_WriteData(LPSPI1_PERIPHERAL, (uint16_t)(0x0100 + (uint8_t)(logoData[logoIndex] >> 3))); //GREEN

LPSPI_WriteData(LPSPI1_PERIPHERAL, (uint16_t)(0x0100 + (uint8_t)(logoData[logoIndex] << 3))); //BLUE

}

while(logoIndex++ < NUM_OF_BITS);

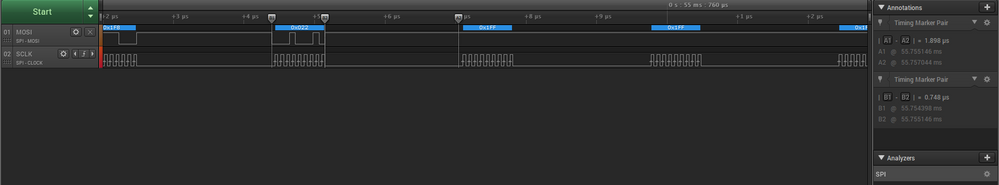

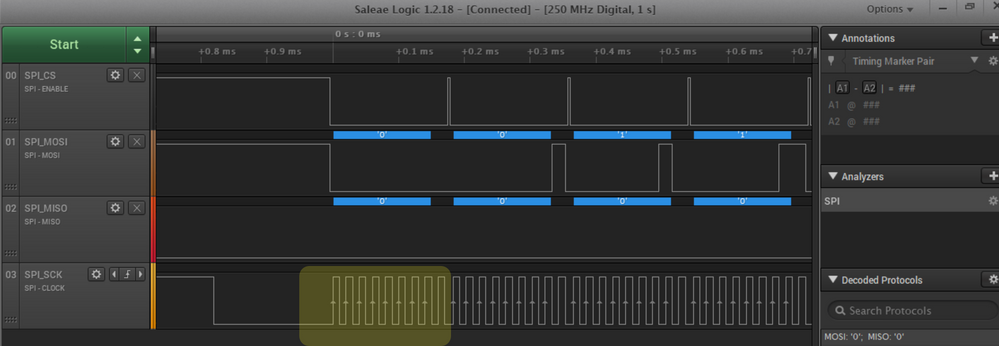

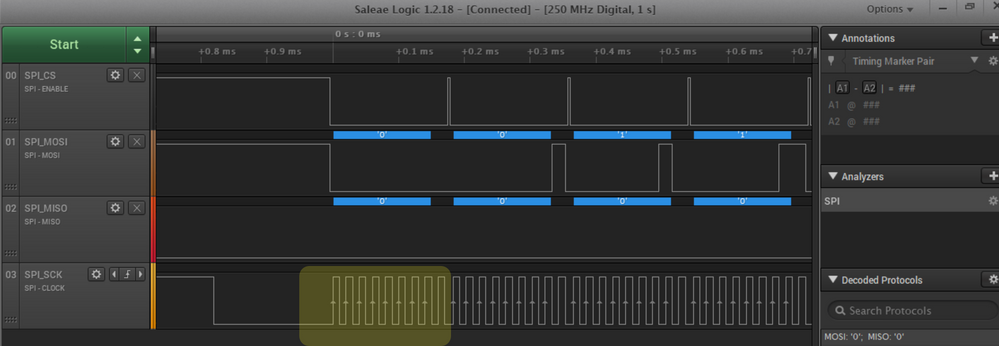

However, I think the FIFO is not being filled as fast as I need. As you can see in the picture below, there are "big" blanks between frames:

(B1-B2 is a frame's length, and B2-A2 is the length of the blank space)

I assume the LPSPI bus is sending the data at a faster pace than the FIFO is being filled. That's why the blanks appear.

How could I further reduce this blank space in order to get a better throughput? Is there any way I can fill the FIFO quicker?

Is there any limit of minimum delay between transfers?

Thanks and regards,

Juanjo

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

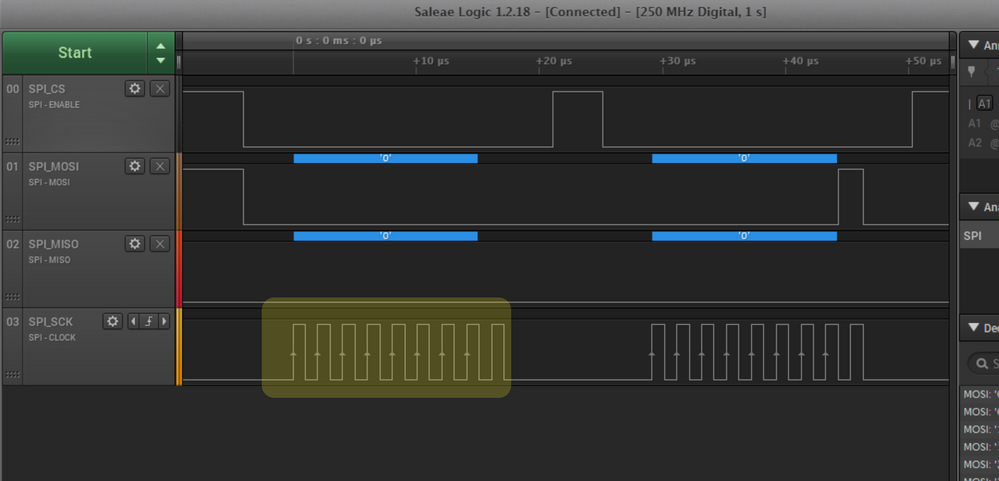

Today, I do the LPSPI interrupt testing on my MIMXRT1050-EVKB board, with the SDK2.8.0:

SDK_2.8.0_EVKB-IMXRT1050\boards\evkbimxrt1050\driver_examples\lpspi\interrupt_b2b\master

I think your issue is not caused by the FIFO fill 0, it should caused by the quick baudrate and the code execution.

Please let me tell you my test result:

1. use 500Kbps baudrate with 9 bit frame datasize

You can find, even use 32bit FIFO fill 0, the duration between each bit is smaller than 32-9 bit.

2. use 50Kbps baudrate with 9 bit frame datasize

3. use 30Mbps baudrate with 9bit frame datasize

You can find, the duration is very large.

As you know, in fact, the code execution and enter and exit the interrupt all need the code execution time.

So, if you want to get the small durtion, still need to minimize each send code execution time, and the ISR code should as simple as possible, you even can do the register control directly instead of calling the API, enter the API function also need time.

Wish it helps you!

If you still have questions about it, please kindly let me know.

Best Regards,

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

----------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Juan Jose Vicente ,

Do you try to use the interrupt method to transfer your LPSPI data?

Then the gap between each byte should be minimized.

From your code, your code is using the polling mode, is it right?

The polling code will also consume the execution time, so you can try the interrupt to send the data, then when the FIFO is finished, the data will be loaded automatically.

Wish it helps you!

If you still have questions about it, please kindly let me know.

Best Regards,

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kerry,

Yes, I've tried using the interrupt method and the blank space is still there.

I think I know where this blank space comes from. Let me explain it a bit so you can tell whether I am correct or not.

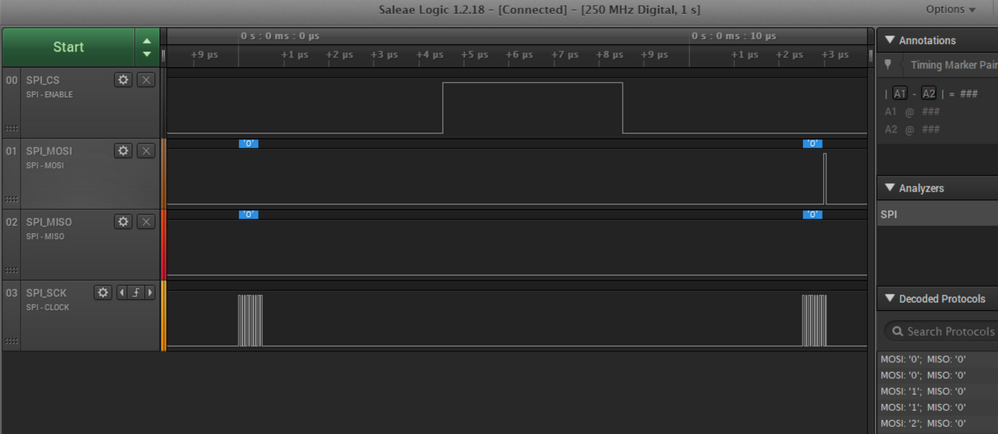

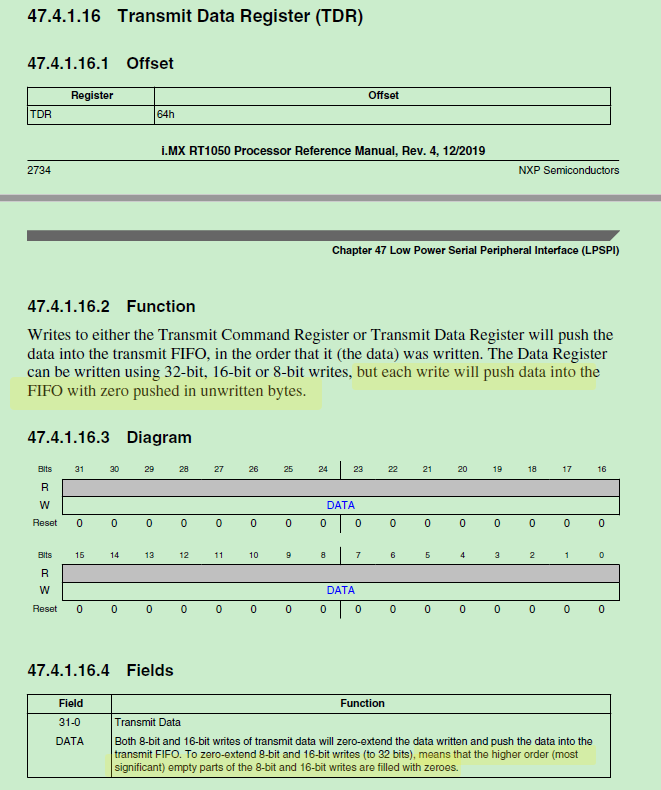

I think it is not a "blank" space. As each FIFO position is 32bit wide and I am tranferring only the least significant 9 bits, this "blank" space are the rest of the 23 most significant bits which are 0s. I have measured the timing parameters and it makes me go "mhhhh":

The bit period is ~84ns and the frame period is ~2.668ns (I am assuming some timing inaccuracy from my logic analyzer). The frame period is about 32x a bit period.

Assuming this is correct, Is there any way I can make the LPSPI peripheral to transmit only a certain quantity of bits per FIFO position?

Kind regards,

Juanjo

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for your test result and the thought sharing.

This information from the RT reference manual may demonstrate your thought.

Wish it helps you!

If you still have questions about it, please kindly let me know.

Best Regards,

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kerry,

Is there any way I can transmit only a portion (9bits) of each FIFO position and then, inmediately send the 9bits of the next FIFO position without transmitting that 0 padding?

I thought it is achieved by using the FRAMEZ bits:

const lpspi_master_config_t LPSPI1_config = {

.baudRate = 30000000,

.bitsPerFrame = 9,

.cpol = kLPSPI_ClockPolarityActiveHigh,

.cpha = kLPSPI_ClockPhaseFirstEdge,

.direction = kLPSPI_MsbFirst,

.pcsToSckDelayInNanoSec = 1,

.lastSckToPcsDelayInNanoSec = 1,

.betweenTransferDelayInNanoSec = 1,

.whichPcs = kLPSPI_Pcs2,

.pcsActiveHighOrLow = kLPSPI_PcsActiveLow,

.pinCfg = kLPSPI_SdiInSdoOut,

.dataOutConfig = kLpspiDataOutRetained

};

LPSPI_MasterInit(LPSPI1_PERIPHERAL, &LPSPI1_config, LPSPI1_CLOCK_FREQ);

However it seems it doesn't work...

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Today, I do the LPSPI interrupt testing on my MIMXRT1050-EVKB board, with the SDK2.8.0:

SDK_2.8.0_EVKB-IMXRT1050\boards\evkbimxrt1050\driver_examples\lpspi\interrupt_b2b\master

I think your issue is not caused by the FIFO fill 0, it should caused by the quick baudrate and the code execution.

Please let me tell you my test result:

1. use 500Kbps baudrate with 9 bit frame datasize

You can find, even use 32bit FIFO fill 0, the duration between each bit is smaller than 32-9 bit.

2. use 50Kbps baudrate with 9 bit frame datasize

3. use 30Mbps baudrate with 9bit frame datasize

You can find, the duration is very large.

As you know, in fact, the code execution and enter and exit the interrupt all need the code execution time.

So, if you want to get the small durtion, still need to minimize each send code execution time, and the ISR code should as simple as possible, you even can do the register control directly instead of calling the API, enter the API function also need time.

Wish it helps you!

If you still have questions about it, please kindly let me know.

Best Regards,

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

----------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi:

I am seeking similiar issue, and find when set CONT=1, then set masterConfig.betweenTransferDelayInNanoSec to desired value could solve this issue.

default masterConfig.betweenTransferDelayInNanoSec setting is masterConfig->betweenTransferDelayInNanoSec = 1000000000U / masterConfig->baudRate * 2U;

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kerry,

Ok, understood. Thank you for your help!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You are welcome!

If you have any new questions in the future, welcome to create the new case.

Best Regards,

Kerry