- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX RT

- :

- How to configure OCRAM into non-cacheable

How to configure OCRAM into non-cacheable

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear all

I use RT1024, and configured OCRAM to 64K, I understand it is cacheable by default and would like to configure it to be non-cacheable by modify void BOARD_ConfigMPU(void) function as below:

/* Region 7 setting: Memory with Normal type, not shareable, outer/inner write back */

MPU->RBAR = ARM_MPU_RBAR(7, 0x20200000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 0, 0, 0, 1, 0, ARM_MPU_REGION_SIZE_64KB);

But it ends up a hard fault, what else do I need to do in addition to this please? Or does it need to leave some area as cacheable?

Regards!

Ping

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @ping1

Seems your modification is wrong:

/* Region 7 setting: Memory with Normal type, not shareable, outer/inner write back */

MPU->RBAR = ARM_MPU_RBAR(7, 0x20200000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 1, 0, 0, 0, 0, ARM_MPU_REGION_SIZE_64KB);

Please try this one, and test it again.

If you still have issues about it, please kindly let me know.

Best Regards,

kerry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

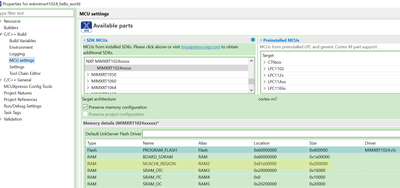

I have Helloworld example open, but OCRAM there is like this:

/* Region 7 setting: Memory with Normal type, not shareable, outer/inner write back */

MPU->RBAR = ARM_MPU_RBAR(7, 0x20200000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 0, 0, 1, 1, 0, ARM_MPU_REGION_SIZE_128KB);

Anything here I can do to change it to non-cacheable? sorry, I am new to cache. My target board doesn't have external RAM, I need to use OCRAM as data RAM, but doesn't want it to change any values randomly for me.

Regards!

Ping

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @ping1

Helloworld or the USB code, the SDRAM area is the noncache

You can check this area related configuration, in the ld and related code.

If you still have issues, just kindly let me know.

BTW, if your ITCM, DTCM is enough, it is the noncache area ,can you directly.

Best Regards,

kerry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for reply, Kerry

My target doesn't have external RAM, and my DTC and ITC are not enough for my project, so I have to use OCRAM, my goal is to configure all OCRAM into non-cacheable, but when I change the memory configuration flags in the functions, it ends up in hard fault. Is this possible or not?

Regards!

Ping

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @ping1

Seems your modification is wrong:

/* Region 7 setting: Memory with Normal type, not shareable, outer/inner write back */

MPU->RBAR = ARM_MPU_RBAR(7, 0x20200000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 1, 0, 0, 0, 0, ARM_MPU_REGION_SIZE_64KB);

Please try this one, and test it again.

If you still have issues about it, please kindly let me know.

Best Regards,

kerry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Kelly

Thanks you for looking at my modification finally! It doesn't end up with hard fault now.

One more question please - how can I tell it is non-cacheable now? The original configuration code has no difference between ITC, DTC and OCRAM.

Regards!

Ping

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @ping1

Thanks for your updated information.

After you set it, your OCRAM is the noncacheable area, you can use it directly, even you enable the cache, the MPU will not consider the OCRAM as cacheable area. You just take it as the normal memory to use, no other special to process.

Wish it helps you!

Best Regards,

kerry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for reply, Kerry

I followed the first link and changed OCRAM to 64K on my RT1024. and it seems working, but in BOARD_ConfigMPU(void) , memory region ITC, DTC, and OCRAM are configured same except size, how can I tell OCRAM is cacheable or not? May i simply change the value as above to make it non-cacheable?

Regards!

Ping

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hI @ping1

BTW, in our SDK also have a lot of SDK contains the non cache code, you also can refer to it.

Eg, some USB code, helloworld should also have it.

Best Regards,

Kerry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @ping1

About the flexRAM recofiguration, please check this link:

https://community.nxp.com/t5/i-MX-RT-Knowledge-Base/Reallocating-the-FlexRAM/ta-p/1117649

Make sure you configure it correctly.

Debug, without issues.

Then, you can modify the noncache modification.

About the cache, please check this application note:

https://www.nxp.com/docs/en/application-note/AN12042.pdf

If you still have issues about it, please kindly let me know.

Best Regards,

Kerry