- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX RT

- :

- Re: FlexSPI boot from serial flash

FlexSPI boot from serial flash

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

FlexSPI boot from serial flash

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I've been working with custom hardware derived from the iMXRT1060EVK which boots from QuadSPI IS25LP064 (same as EVK). For our application, we need more boot flash, so on one of the boards we swapped out the IS25LP064 for IS25LP01G. This forces me to get a better grip on the evkmimxrt1060_flexspi_nor_config.c that comes with the SDK...

const flexspi_nor_config_t qspiflash_config = {

.memConfig = {

.tag = FLEXSPI_CFG_BLK_TAG,

.version = FLEXSPI_CFG_BLK_VERSION,

.readSampleClksrc=kFlexSPIReadSampleClk_LoopbackFromDqsPad,

.csHoldTime = 3u,

.csSetupTime = 3u,

.sflashPadType = kSerialFlash_4Pads,

.serialClkFreq = kFlexSpiSerialClk_100MHz,

.sflashA1Size = 8u * 1024u * 1024u,

.lookupTable = {

FLEXSPI_LUT_SEQ(CMD_SDR, FLEXSPI_1PAD, 0xEB, RADDR_SDR, FLEXSPI_4PAD, 0x18),

FLEXSPI_LUT_SEQ(DUMMY_SDR, FLEXSPI_4PAD, 0x06, READ_SDR, FLEXSPI_4PAD, 0x04),

},

},

.pageSize = 256u,

.sectorSize = 4u * 1024u,

.blockSize = 256u * 1024u,

.isUniformBlockSize = false,

};

Is there any text/document that explains the LUT in decent detail?

Thanks to some good answers on the forum I've gained some insight, but still can't boot with this new (larger but compatible) device. For example, in this post it explains that the 0x18 indicates a 24-bit address. It also mentions that 0x20 is used for larger addresses (32-bit such as mine); but where did that information come from? I've read through section 9.6.3.1 (FlexSPI Configuration Block) as well as the LUT section (27.5.7) in the reference manual, but can't find that level of detail. What am I missing?

UPDATE:

Is the text in section 27.5.8 (Programmable Sequence Engine) the only thing available with regard to describing the Instruction structure (OPCODE|NUM_PADS|OPERAND) of LUT entries?

All I want to do is update evkmimxrt1060_flexspi_nor_config.c to allow me to boot with the IS25LP01G (instead of the IS25LP064); after 8-10 hours of digging I've made very little progress.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

I believe you can use the same setup for your chip since it boots up in 3-byte addressing mode (as the fast quad read command uses) and is suitable for up to 128Mb.

You can then command it to 4-byte addressing mode once the application is up.

Regards

Mark

[uTasker project developer for Kinetis and i.MX RT]

Contact me by personal message or on the uTasker web site to discuss professional training, solutions to problems or rapid product development requirements

For professionals searching for faster, problem-free Kinetis and i.MX RT 10xx developments the uTasker project holds the key: https://www.utasker.com/iMX/RT1060.html

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yea, that's what I would have expected as well... No beans...

Maybe I need to go back to the lab and verify clean connections on this modified board...

Tx

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi EdSutter,

Do you use the 4 bytes address commander on your side, whether that works or not?

Wish it helps you!

If you still have questions about it, please kindly let me know!

Best Regards,

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-----------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Kerry,

Thanks for responding...

Sorry, I don't know what the "4 bit address commander" is...

Please explain.

Ed

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi EdSutter

Sorry, my mistyping, 4Bytes command.

I mean, in the LUT, modify the read command from 3byte command to 4Bytes:

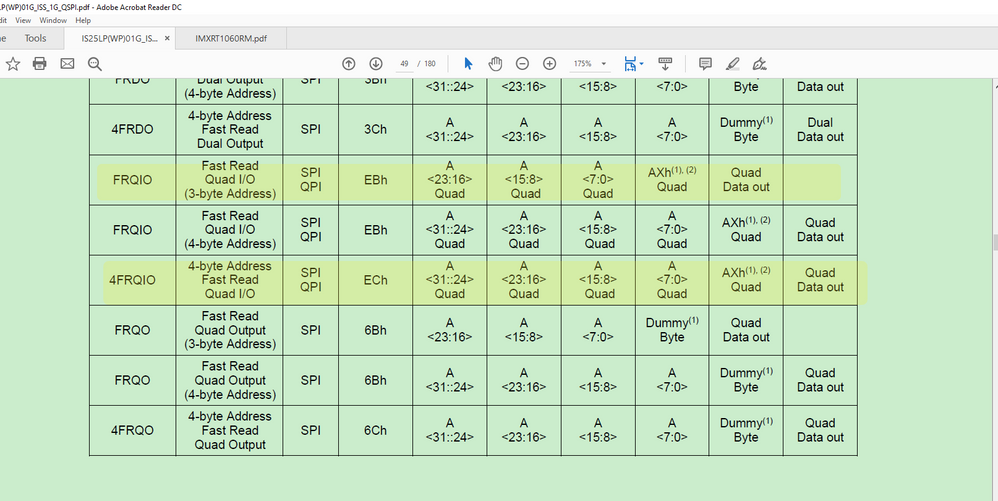

More details, you need to check the ISSI flash chip datasheet:

You can use the ECH, address from 0X18 to 0X20(24 bit address to 32bit address).

Do you try it on your side?

Any issues or not?

Best Regards,

Kerry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kerry,

I agree with all your saying, but keep in mind I've been debugging the initial bootup, not downloaded code that is later used to operate on the flash. My application (once downloaded) already uses the API for operations; the issue has been getting it to boot (i.e. start executing from that flash).

The strange part of all this is that after I installed and ran the application you suggested from the SDK, the board has been booting pretty consistently. It almost seems like the flash device needed to be "tickled" and now its happy (makes no sense, but that is the empirical data).

Things just don't make sense right now, because the same code (that started working after I ran the app out of internal ram) is now booting consistently.

Again, thanks for your help on this; I have to conclude at this point that there is something very strange about the hardware.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi EdSutter,

Thanks for your information sharing.

If you have any other board, you also can solder a new IS25LP01G chip, then use MCUBootutility tool to download the code, whether that is running, then you can debug it again, whether your strange hardware issues happens or not. If you have time, just do more testing. Just make sure, whether it is the hardware stable issue or the new QSPI flash QE bit issues.

Or, when you meet the issues, you also can use the MCUBootutility tool to erase the external flash at first, then do the debug again. As I know, when the external flash code is abnormal, it will caused the boot issues or even the debug connection issues.

Wish it helps you!

Best Regards,

Kerry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Kerry,

The timing constraints on the IS25LP01 are a bit tighter than those of the IS25LP064 (i.e. the '01 is a bit slower than the '064).

There are a lot of other parameters in the flexspi_mem_config_t structure (which is part of the flash config structure). What parameters in the flexspi_mem_config_t structure are actually used by the bootrom?

Ed

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi EdSutter,

Please test this flexspi nor flash code:

SDK_2.8.6_EVK-MIMXRT1060\boards\evkmimxrt1060\driver_examples\flexspi\nor\polling_transferr

Whether you can read and write the chip or not?

Please run this code in the internal TCM.

You mentioned:The timing constraints on the IS25LP01 are a bit tighter than those of the IS25LP064

Please also give me the related time screenshot, I will help you to check it.

Best Regards,

Kerry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Well, this is totally unexplainable...

After running the polling_transfer application from ITCM those few times (most of which the results were inconsistent, but then it ran a few times with everything succeeding...

So I went back to my original code (with same LUT values in flash_config) AND THE BOARD IS BOOTING! I have no clue why, so I have to step back and really think now... possibly a footprint problem on the board that cleans itself up (slight expansion on solder joint) if left on for a few hours???

If I come to any real conclusion I will certainly post my results...

Ed

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi EdSutter,

Thanks for your effort!

Do you mean, after the recommended polling_transfer application, now all works OK?

If yes, it should related to the QE bit, as you know this bit is the Non-Volatile bit, to the new chip, it should be enabled at first.

Please do more testing, any updated information, just kindly let me know.

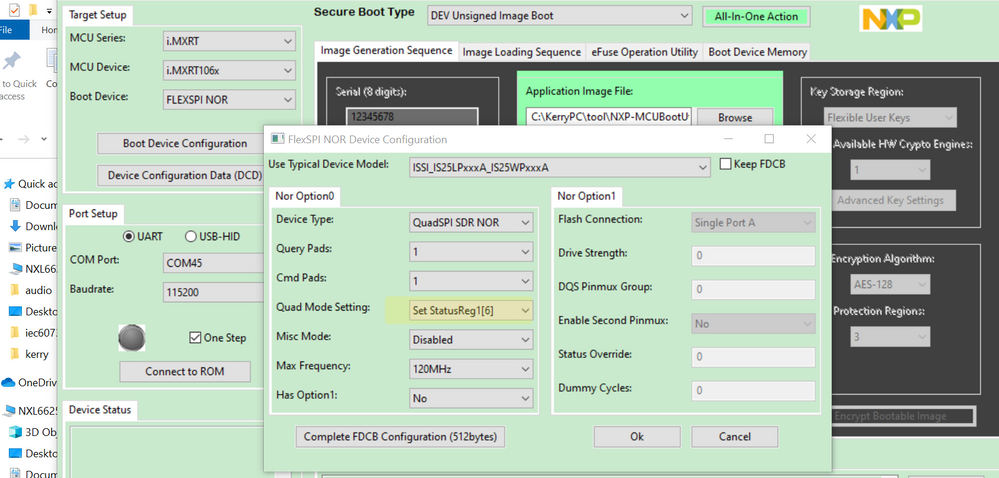

BTW, you also can use the MCUBootUtility tool to download the code to the new chip:

https://github.com/JayHeng/NXP-MCUBootUtility/archive/v2.4.0.zip

the related user manual is:

https://github.com/JayHeng/NXP-MCUBootUtility

Wish it helps you!

Best Regards,

Kerry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kerry,

Not sure I understand how the QE bit explains any of this. That bit is used to put the device in quad mode; which causes the WP, HOLD and SI pins to be used as IO pins. I get that (we are using quad mode). I have been using the JLINK to program the device all along, and the data is there (even though it didn't boot). I just use the 'mem' command in JLINK to see the content at 0x60000000. So the device was being programmed. The rom bootloader is then supposed to read the configuration (as set up by xxx_flexspi_nor_config.c) and that is set up with .sflashPadType = kSerialFlash_4Pads, which I have to assume is what the bootloader uses to enable the QE bit.

So this is still a bit of a mystery, but its now vaguely pointing toward hardware. The board "seems" to be more consistent (that is... it boots) after it is warm. We've looked at pad size under the device and are hoping to get x-rays back from the manufacturer so that will be investigated. When/if we find the root cause I will certainly post the result; meanwhile, I think its safe to say that the flash configuration below does in-fact allow the iMXRT1062 to boot from a IS25LP01G (changes in bold). Note its quite possible that it would boot with the original settings (as applicable to the IS25LP064); but at this point I don't have the energy to bother trying it...

const flexspi_nor_config_t qspiflash_config = {

.memConfig = {

.tag = FLEXSPI_CFG_BLK_TAG,

.version = FLEXSPI_CFG_BLK_VERSION,

.readSampleClksrc=kFlexSPIReadSampleClk_LoopbackFromDqsPad,

.csHoldTime = 3u,

.csSetupTime = 3u,

.sflashPadType = kSerialFlash_4Pads,

.serialClkFreq = kFlexSpiSerialClk_100MHz,

.sflashA1Size = 128u * 1024u * 1024u,

.lookupTable = {

FLEXSPI_LUT_SEQ(CMD_SDR,FLEXSPI_1PAD,0xEC, RADDR_SDR,FLEXSPI_4PAD,0x20),

FLEXSPI_LUT_SEQ(DUMMY_SDR,FLEXSPI_4PAD,0x06,READ_SDR, FLEXSPI_4PAD,0x04),

},

},

.pageSize = 256u,

.sectorSize = 4u * 1024u,

.blockSize = 256u * 1024u,

.isUniformBlockSize = false,

};

Thanks for your input on this,

Ed

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi EdSutter,

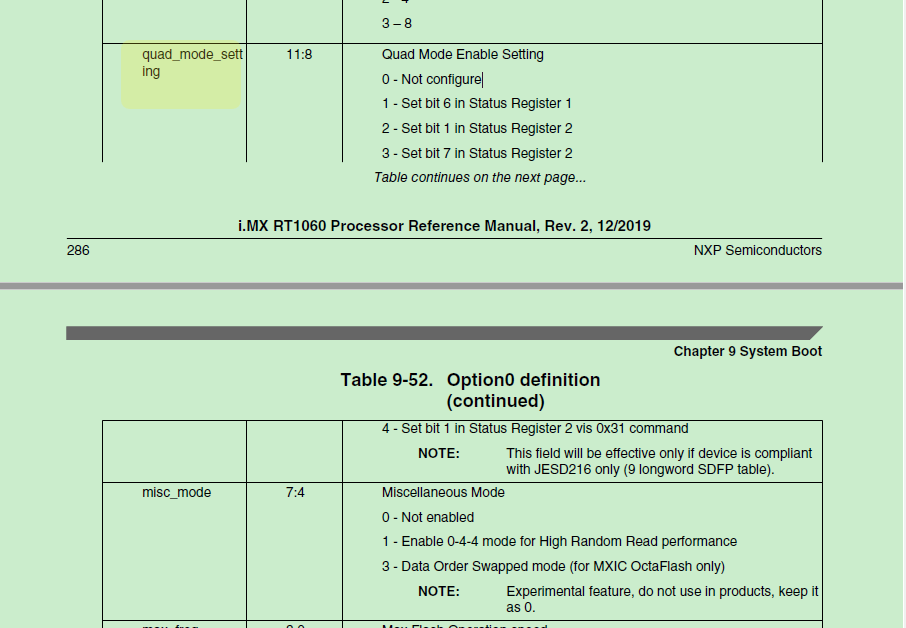

Enable the QE bit is not set up with .sflashPadType = kSerialFlash_4Pads,

It normally in the project related program flashloader files. The option defines it:

Or the polling code like this to enable it:

/* Enter quad mode. */

status = flexspi_nor_enable_quad_mode(EXAMPLE_FLEXSPI);

if (status != kStatus_Success)

{

return status;

}

status_t flexspi_nor_enable_quad_mode(FLEXSPI_Type *base)

{

flexspi_transfer_t flashXfer;

status_t status;

uint32_t writeValue = FLASH_QUAD_ENABLE;

/* Write enable */

status = flexspi_nor_write_enable(base, 0);

if (status != kStatus_Success)

{

return status;

}

/* Enable quad mode. */

flashXfer.deviceAddress = 0;

flashXfer.port = kFLEXSPI_PortA1;

flashXfer.cmdType = kFLEXSPI_Write;

flashXfer.SeqNumber = 1;

flashXfer.seqIndex = NOR_CMD_LUT_SEQ_IDX_WRITESTATUSREG;

flashXfer.data = &writeValue;

flashXfer.dataSize = 1;

status = FLEXSPI_TransferBlocking(base, &flashXfer);

if (status != kStatus_Success)

{

return status;

}

status = flexspi_nor_wait_bus_busy(base);

/* Do software reset. */

FLEXSPI_SoftwareReset(base);

return status;

}

BTW, do you use the MCUBootUtility to download the code? That tool will help you to generate the qspiflash_config directly.

About the hardware, you need to make sure the hardware design is correct, in fact, you also can test it in the MIMXRT1060-EVK board directly by replacing the QSPI chip.

Anyway, any updated information from your side just kindly let me know.

best Regards,

Kerry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Kerry,

the vendor ID (0x9D) comes back correct; and the whole-chip-erase succeeds; but functions after that are flakey at best. I've never seen everything succeed. Sometimes the whole-chip-erase succeeds other times not. I've never seen the page-program succeed.

Regarding the timing... skip that... Its only an issue when powered at 1.8V.

Ed

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Well go figure...

After sending the previous post to you, I ran it again and this time everything passed...

<11:59:39> FLEXSPI example started!

<11:59:39> Vendor ID: 0x9d

<11:59:39> Erasing whole chip over FlexSPI...

<12:00:51> Erase finished !

<12:00:51> Erasing Serial NOR over FlexSPI...

<12:00:51> Erase data - successfully.

<12:00:51> Program data - successfully.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kerry,

Ok, I see what you mean, yes I've tried several different attempts at LUT like that. To be sure, I rebuilt with your settings and the results are the same.

One thing I did find yesterday...

The clock input does change to the frequency that I specify in .serialClkFreq, so that tells me that the bootrom is able to read the device and adjust based on the configuration specified in flexspi_nor_config.c.

Ed