- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX RT

- :

- Re: FLEXRAM configuration

FLEXRAM configuration

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I modified Flexram according to https://community.nxp.com/t5/i-MX-RT-Knowledge-Base/Reallocating-the-FlexRAM/ta-p/1117649, 256KB DTCM, 128KB ITCM, 128KB OCRAM. I am using i.MXRT1064.

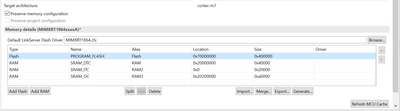

I have changed under MCU settings

/* Reallocating the FlexRAM */

__asm(

".syntax unified\n"

"LDR R0, =0x400ac044\n" // Address of register IOMUXC_GPR_GPR17

"LDR R1, =0xaaaaff55\n" // FlexRAM configuration DTC = 265KB, ITC =

// 128KB, OC = 128KB

"STR R1,[R0]\n"

"LDR R0,=0x400ac040\n" // Address of register IOMUXC_GPR_GPR16

"LDR R1,[R0]\n"

"ORR R1,R1,#4\n" // The 4 corresponds to setting the FLEXRAM_BANK_CFG_SEL

// bit in register IOMUXC_GPR_GPR16

"STR R1,[R0]\n"

#ifdef FLEXRAM_ITCM_ZERO_SIZE

"LDR R0,=0x400ac040\n" // Address of register IOMUXC_GPR_GPR16

"LDR R1,[R0]\n"

"AND R1,R1,#0xfffffffe\n" // Disabling SRAM_ITC in register

// IOMUXC_GPR_GPR16

"STR R1,[R0]\n"

#endif

#ifdef FLEXRAM_DTCM_ZERO_SIZE

"LDR R0,=0x400ac040\n" // Address of register IOMUXC_GPR_GPR16

"LDR R1,[R0]\n"

"AND R1,R1,#0xfffffffd\n" // Disabling SRAM_DTC in register

// IOMUXC_GPR_GPR16

"STR R1,[R0]\n"

#endif

"LDR R0, =0x400ac038\n" // Address of register IOMUXC_GPR_GPR14

"LDR R1, =0x980000\n" // New size configuration for the IOMUXC_GPR_GPR14

// register

"STR R1,[R0]\n"

".syntax divided\n");

also in fsl_flexspi_nor_boot.c

const ivt image_vector_table = {

IVT_HEADER, /* IVT Header */

(uint32_t)ResetISR, /* Image Entry Function */

when I observe stack usage ita overflowing even before entering main.

i have another question, why do we modify fsl_flexspi_nor_boot.c, I saw map file before and after, reset is at same location

also when I execute code I am seeing cases where variable values are getting overwritten as if stack is overrunning into data section

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

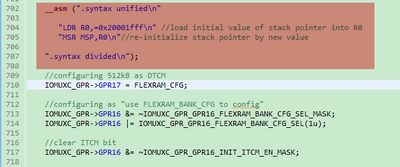

Thanks for providing the example code. I apologize, I forgot to mention that you need to place the stack at the beginning of the DTC. To do this you need to add the following code right before you start reallocating the FlexRAM.

Regards,

Victor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

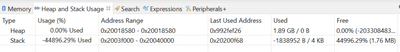

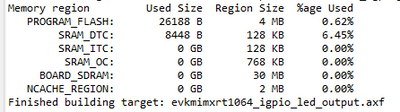

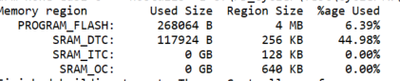

I've never seen this behavior before. The code that you are using looks fine. Did you modify the MPU as well? Why is your heap size is set to 0? When you compile your project, how does the memory usage looks? You can see this in the console after you build your application as shown below.

Regarding the changes on the fsl_flexspi_nor_boot.c. You are not changing the address of the reset handler, you are just changing the entry address of the application. As I mentioned in the document, there are lots of dangerous areas in reconfiguring the FlexRAM in code. It pretty much all boils down to the fact that any code/data/stack information written to the RAM can end up changing location during the reallocation. This change is to avoid that any problems with these things.

Regards,

Victor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I have heap zero as am not planning to use any dynamic allocation.

following is the usage as shown in the console

regarding MPU, yes I did changes to it too, am not using external SDRAM or flash connected at 0x60000000 so I disabled those sections.

/* Disable I cache and D cache */

if (SCB_CCR_IC_Msk == (SCB_CCR_IC_Msk & SCB->CCR)) {

SCB_DisableICache();

}

if (SCB_CCR_DC_Msk == (SCB_CCR_DC_Msk & SCB->CCR)) {

SCB_DisableDCache();

}

/* Disable MPU */

ARM_MPU_Disable();

/*

* Add default region to deny access to whole address space to workaround

* speculative prefetch. Refer to Arm errata 1013783-B for more details.

*

*/

/* Region 0 setting: Instruction access disabled, No data access permission.

*/

MPU->RBAR = ARM_MPU_RBAR(0, 0x00000000U);

MPU->RASR =

ARM_MPU_RASR(1, ARM_MPU_AP_NONE, 2, 0, 0, 0, 0, ARM_MPU_REGION_SIZE_4GB);

#if defined(XIP_EXTERNAL_FLASH) && (XIP_EXTERNAL_FLASH == 1)

/* Region 3 setting: Memory with Normal type, not shareable, outer/inner write

* back. */

MPU->RBAR = ARM_MPU_RBAR(1, 0x70000000U);

MPU->RASR =

ARM_MPU_RASR(0, ARM_MPU_AP_RO, 0, 0, 1, 1, 0, ARM_MPU_REGION_SIZE_4MB);

#endif

/* Region 4 setting: Memory with Device type, not shareable, non-cacheable. */

MPU->RBAR = ARM_MPU_RBAR(2, 0x00000000U);

MPU->RASR =

ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 2, 0, 0, 0, 0, ARM_MPU_REGION_SIZE_1GB);

// ITCM

MPU->RBAR = ARM_MPU_RBAR(3, 0x00000000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 0, 0, 1, 1, 0,

ARM_MPU_REGION_SIZE_128KB);

// DTCM

MPU->RBAR = ARM_MPU_RBAR(4, 0x20000000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 0, 0, 1, 1, 0,

ARM_MPU_REGION_SIZE_256KB);

// OC RAM from FLEXRAM Config

MPU->RBAR = ARM_MPU_RBAR(5, 0x20200000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 0, 0, 1, 1, 0,

ARM_MPU_REGION_SIZE_128KB);

MPU->RBAR = ARM_MPU_RBAR(6, 0x20220000U);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 0, 0, 1, 1, 0,

ARM_MPU_REGION_SIZE_512KB);

MPU->RBAR = ARM_MPU_RBAR(7, 0x40000000);

MPU->RASR =

ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 2, 0, 0, 0, 0, ARM_MPU_REGION_SIZE_4MB);

MPU->RBAR = ARM_MPU_RBAR(8, 0x42000000);

MPU->RASR =

ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 2, 0, 0, 0, 0, ARM_MPU_REGION_SIZE_1MB);

/* Enable MPU */

ARM_MPU_Enable(MPU_CTRL_PRIVDEFENA_Msk);

/* Enable I cache and D cache */

SCB_EnableDCache();

SCB_EnableICache();

I have a question regarding DTCM config in MPU, I have a few buffers which are specific for DMA & core, I am hoping to keep them in DTCM itself. will there be a problem?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I was able to replicate the behavior that you mentioned. I'm checking this internally. I'll give you an update as soon as possible.

Regarding the placement of the buffers, based on the information that you provided, you shouldn't have problems if you keep the buffers in the DTCM.

Regards,

Victor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

any updates?

just to be clear, were you able to see the stack overflow error or memory corruption issue?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

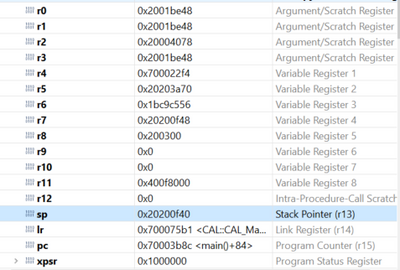

Thanks for your patience with this case. Yes, I was able to replicate the behavior that you mentioned. I investigated this internally and found out what was causing it. As I mentioned in the community document, there are lots of dangerous areas in reconfiguring the FlexRAM in code. It pretty much all boils down to the fact that any code/data/stack information written to the RAM can end up changing location during the reallocation. You've happened upon the other danger with pointing the stack into RAM locations that are moving. To overcome this you'll need to place the stack at the start of the DTCM memory and change the size. I will add this information to the community document.

Regards,

Victor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have made changes according to your suggestion, I think it is still a problem.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

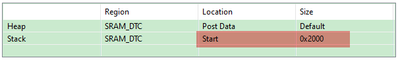

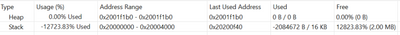

In the linker file, you will need to modify the stack as shown below.

Once you do this, you shouldn't have any problems.

As mentioned in the community document, all these changes are needed because you are reallocating the FlexRAM through software. When you reallocate it using the fuses, these changes in the linker file and the stack won't be needed.

Regards,

Victor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Sorry if I am missing the point, wont the linker file get automatically generated if we select "manage linker file" checkbox in project settings?

anycase, when I opened like file stack setting is showing exactly like how it is depicted by you.

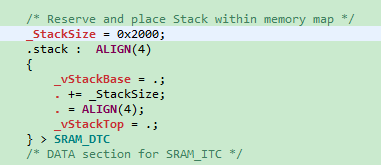

/* Reserve and place Stack within memory map */

_StackSize = 0x2000;

.stack : ALIGN(4)

{

_vStackBase = .;

. += _StackSize;

. = ALIGN(4);

_vStackTop = .;

} > SRAM_DTC

/* DATA section for SRAM_ITC */

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Thanks for providing the example code. I apologize, I forgot to mention that you need to place the stack at the beginning of the DTC. To do this you need to add the following code right before you start reallocating the FlexRAM.

Regards,

Victor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Victor,

Can you explain how you came up with 0x20001FFF as the value for the stack pointer location? I tried to match the linker settings in your community write up, and the stack got located at 0x20001000. The default code in ResetISR already contains code for initializing the SP:

__asm volatile ("MSR MSP, %0" : : "r" (&_vStackTop) : );

The line above would set SP to 0x20001000 rather than 0x20001FFF. Why should the SP be set differently when FlexRAM is configured dynamically (rather than from fuses)?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

MIMXRT1052_Project.axf section `.text' will not fit in region `SRAM_DTC'

c:/nxp/mcuxpressoide_11.5.0_7232/ide/plugins/com.nxp.mcuxpresso.tools.win32_11.5.0.202107051138/tools/bin/../lib/gcc/arm-none-eabi/10.3.1/../../../../arm-none-eabi/bin/ld.exe: region `SRAM_DTC' overflowed by 9607148 bytes

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Can some one upload any freeRTOS NXP project which uses External RAM.

I did try to follow this

MIMXRT1052_Project.axf section `.text' will not fit in region `SRAM_DTC'

c:/nxp/mcuxpressoide_11.5.0_7232/ide/plugins/com.nxp.mcuxpresso.tools.win32_11.5.0.202107051138/tool...

no luck.