- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX RT

- :

- Diffrent between pin configuration

Diffrent between pin configuration

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Diffrent between pin configuration

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I working with i.MX RT1166 .

But I am not sure about the GPIOs pin configuration. For example the pin GPIO_DISP_B2_11 :

If I want to configure it as GPIO5 pin 12 ,I understand that I should use this configuration :

IOMUXC_SetPinMux(IOMUXC_GPIO_DISP_B2_11_GPIO_MUX5_IO12, 0U);

But if I want to configure it as GPIO11 pin 12 I should use this configuration :

IOMUXC_SetPinMux(IOMUXC_GPIO_DISP_B2_11_GPIO11_IO12, 0U);

why GPIO5 configured as GPIO_MUX and not as GPIO like GPIO 11 ?

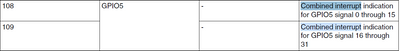

Can I get IRQ on this pin under CM7 core ? ( GPIO5_Combined_0_15_IRQHandler)

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

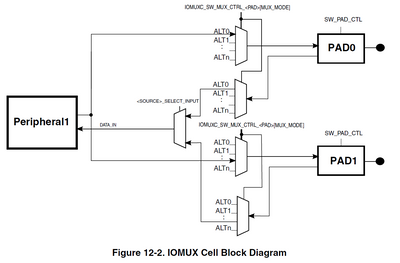

Hi @ronen , The best description of MUX is in this diagram on reference manual. The IOMUX cell is required whenever two or more functional modes are required for a specific pad or when one functional mode and the one test mode are required.

The manager for interrupts in CM7, these qualified outputs are OR'ed together to generate two one-bit interrupt lines:

• Combined interrupt indication for GPIOx signals 0 - 15

• Combined interrupt indication for GPIOx signals 16 - 31