- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX RT

- :

- DMA to FlexSPI TX

DMA to FlexSPI TX

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

DMA to FlexSPI TX

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

we use the DMA Controller to fill the transmit buffer. The data should then be transmitted by FlexSPI/Hyperbus. The Configuration of FlexSPI contains a free running clock because we communicate with an FPGA.

Our device is a RT1051.

We need to transfer more than 128 Byte (TX FIFO size). Hence, we rely on multiple minor or major loop executions.

The LUT is configured similar to AN12239 ("How to Enable HyperRAM with i.MX RT").

If we increase the transmission speed to a certain level, we experince the following behavior:

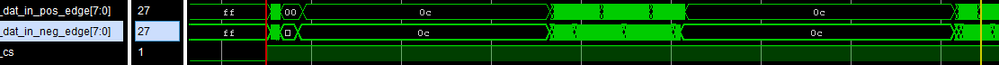

- the data transmission on data lines contains "breaks". It looks like the lines are not actively driven during this times

- CS/SS stays asserted

- Clock continues to run (as expected)

- the breaks seem to correlate with the times when the DMA refills the TX buffer

We can measure this by using chipscope. The picture shown is a high speed transfer (160MHz DDR -> 320MB/s). 0x0c is the value if the lines are not driven.

Is there a possibility to configure the chip select line of FlexSPI to be deasserted when there is no transmit data available but the transfer is not finished yet?

Thanks in advance and best regards,

Oliver

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Oliver He,

Thank you for your interest in NXP Semiconductor products and for the opportunity to serve you.

1) Is there a possibility to configure the chip select line of FlexSPI to be deasserted when there is no transmit data available but the transfer is not finished yet?

-- The FlexSPI doesn't support this feature that makes the CS be deserted automatically when without any data transaction, unless, control the Flex_SS pin manually.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Isn't that quite a limit on the achievable speed and realtime capabilities, if we are using DMA and Hyperbus? Considering the DMA performance according to: https://community.nxp.com/message/1238037

BR,

Oliver

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Oliver He,

Thanks for your reply.

1) Isn't that quite a limit on the achievable speed and realtime capabilities, if we are using DMA and Hyperbus?

-- No, I don't think. Actually, I'm curious about the testing result as the Memory to Memory DMA on i.MX Rt 1020 presents, however, I'm also cautious, as I don't know the exact testing code he used, so I can't provide an explanation or jump to some conclusion about it, and I wish he will provide some more detail information in next reply.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for the quick reply!

Best regards,

Oliver