- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX RT

- :

- Re: Capacitors request for NVCC_EMCx power source.

Capacitors request for NVCC_EMCx power source.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello community,

I have a question about supply capacitors request table.

In Table 1. Processor supply capacitors when on-chip DCDC regulators are used of document

Hardware Development Guide for the MIMXRT1160/1170 Processor , Rev. 2, 09/2021,

It say that

| Power rail | 0.1 μF | 0.22 μF | 1 μF | 2.2 μF | 4.7 μF | 22 μF | Notes |

| NVCC_EMC1_X | 1 | 1 | Place2.2 μF under balls F6, F7 | ||||

| NVCC_EMC2_X | 1 | 1 | Place 2.2 μF under balls H6, J6 |

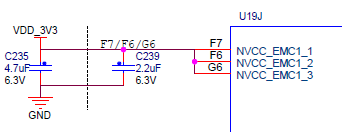

It is meaning that the three power lines(NVCC_EMC1_1, NVCC_EMC1_2, NVCC_EMC1_3) require one 2.2uF and one 4.7uF, one under the F6 ball and the other under the F7 ball.

Each of the three power lines does not individually require 2.2uF and 4.7uF.

Is this understanding is correct?

Best regards,

Ishii.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Please accept my apologies for the delay, I was out of the office a couple of days due a personal situation. I highly appreciate your patience.

Regarding your question, and after double-checking, the correct one is as you mentioned at the end, as it shown on the diagram, 1 x 2.2uF + 1 x 4.7uF for all those 3 lines (F7/F6/G6).

Hope it was helpful, please let me know if you have more questions.

Thank you.

Best Regards.

Pablo Avalos.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you so much for using our community. I am here to assist you. I really appreciate your patience.

In order to help you with your request, may you clarify to me what do you mean with your question about each of those three power lines does not individually require those capacitors? Because based on the table, it says that each power line needs both capacitors.

I will stay tuned to your reply, so please let me know if you have more questions.

Best Regards.

Pablo Avalos.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello @PabloAvalos

Thank you for your reply.

And sorry my wrong question.

| Power rail | 0.1uF | 0.22uF | 1uF | 2.2uF | 4.7uF | 22uF | Notes |

| NVCC_EMC1_X | 1 | 1 | Place under balls F7, G6 |

mean that

1)

| Power rail | 0.1uF | 0.22uF | 1.uF | 2.2uF | 4.7uF | 22uF | Notes |

NVCC_EMC1_1 NVCC_EMC1_2 NVCC_EMC1_3 | 1 | 1 | Place under balls F7->2.2uF G6->4.7uF |

or

2)

| Power rail | 0.1uF | 0.22uF | 1uF | 2.2uF | 4.7uF | 22uF | Notes |

| NVCC_EMC1_1 | 1 | 1 |

| ||||

| NVCC_EMC1_2 | 1 | 1 |

| ||||

| NVCC_EMC1_3 | 1 | 1 |

|

Which is correct answer?

From schematic of RT1170-EVK, it seems that 1x 2.2uF and 1x 4.7uF for 3 ball(NVCC_EMC1_1, NVCC_EMC1_2, NVCC_EMC1_3) is correct.

Is it OK?

Best regards,

Ishii.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Please accept my apologies for the delay, I was out of the office a couple of days due a personal situation. I highly appreciate your patience.

Regarding your question, and after double-checking, the correct one is as you mentioned at the end, as it shown on the diagram, 1 x 2.2uF + 1 x 4.7uF for all those 3 lines (F7/F6/G6).

Hope it was helpful, please let me know if you have more questions.

Thank you.

Best Regards.

Pablo Avalos.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello @PabloAvalos

Thank you for your reply.

Is the same rule applied to these two power lines?

| Power rail | 0.1uF | 0.22uF | 1uF | 2.2uF | 4.7uF | 22uF | Notes |

| VDD_SOC_IN_x | 2 | 3 | 1 | Place 0402 under balls H8, J8, J9,J10, K10 | |||

| NVCC_EMC2_X | 1 | 1 | Place under balls H6, J6 |

Best regards,

Ishii.