- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX RT

- :

- Re: Can I put Ethernet descriptors and buffers in OCRAM?

Can I put Ethernet descriptors and buffers in OCRAM?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

In the application examples from the SDK, it seems they all put Ethernet buffers/descriptors into DTCM.

I'm using a '1062, so I'd like to relocate these buffers to OCRAM2 (using MPU to mark the portion of OCRAM2 used as non-cacheable/unbuffered). This allows me to maximize the size of I/DTCM space.

I have not been able to get this to work. Whenever I put the Ethernet buffers in OCRAM2 (non-cacheable/unbuffered) my network connection is unreliable.

Am I just configuring something wrong, or do I have to keep Ethernet buffers in DTCM space?

Tx

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for the suggestions... I was doing that all along, the only change I made was to use OCRAM2 instead of DTCM. That caused my driver to malfunction (drop packets), and that led me to the incorrect conclusion that for some reason I could not use OCRAM2 for Ethernet buffer descriptors.

Anyway, I found the problem... I had omitted the call to __DSB() just prior to writing to ENET->TDAR.

While I don't have time to fully understand why, I can say that empirically this fixed my problem.

Sooner or later I'll read up on why the Data Synchronization Barrier was needed for OCRAM2 but not DTCM. I'm sure TCM has something to do with it, but I can't confirm that at this point.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for the suggestions... I was doing that all along, the only change I made was to use OCRAM2 instead of DTCM. That caused my driver to malfunction (drop packets), and that led me to the incorrect conclusion that for some reason I could not use OCRAM2 for Ethernet buffer descriptors.

Anyway, I found the problem... I had omitted the call to __DSB() just prior to writing to ENET->TDAR.

While I don't have time to fully understand why, I can say that empirically this fixed my problem.

Sooner or later I'll read up on why the Data Synchronization Barrier was needed for OCRAM2 but not DTCM. I'm sure TCM has something to do with it, but I can't confirm that at this point.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Any other thoughts on this? Seems to be a simple enough question...

Should I be able to locate the buffers and buffer-descriptors for ENET driver in OCRAM (0x20280000) or OCRAM2 (0x20200000)? If yes, are there any working examples of this?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ed:

OCRAM can be config as non-cache region. But I would suggest put critical code and data into TCM. Which is the fastest way for CPU to access the code and data.

Sorry there is not a demo for this.

You can refer to AN12042 for details.

Regards

Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ed:

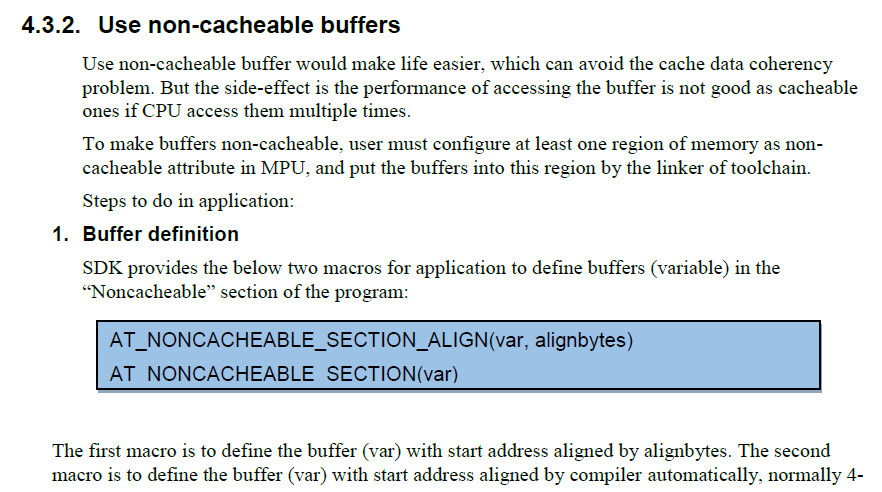

Please make below change to set ENET data buffer memory location and try it again.

Original definition:(enet_ethernetif_kinetis.c)

SDK_ALIGN(static rx_buffer_t rxDataBuff_0[ENET_RXBD_NUM], FSL_ENET_BUFF_ALIGNMENT);

SDK_ALIGN(static tx_buffer_t txDataBuff_0[ENET_TXBD_NUM], FSL_ENET_BUFF_ALIGNMENT);

Change to:

AT_NONCACHEABLE_SECTION_ALIGN(static rx_buffer_t rxDataBuff_0[ENET_RXBD_NUM], FSL_ENET_BUFF_ALIGNMENT);

AT_NONCACHEABLE_SECTION_ALIGN(static tx_buffer_t txDataBuff_0[ENET_TXBD_NUM], FSL_ENET_BUFF_ALIGNMENT);

Regards

Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for responding, but I'm using that now ...

The SDK_ALIGN macro doesn't force the buffers anywhere, so using AT_NONCACHEABLE_SECTION_ALIGN

puts them in the same "NonCacheable" area as the buffer descriptors. I made that change a while back.

But the linker file is what determines what memory space the NonCacheable section is placed in.

In the linker files under the lwip_examples directory, they put NonCacheable in either SDRAM or DTCM.

On my MIMX1060EVK eval board I've run with the same code but the linker file maps it to SDRAM and that works fine.

My custom hardware doesn't have SDRAM, and the Ethernet driver runs fine as long as I have NonCacheable mapped into DTCM. I'd like to have theses buffers in OCRAM2 if possible, so my question stands...

MEMORY

{

...

m_data (RW) : ORIGIN = 0x20000000, LENGTH = 0x00020000

...

}

SECTIONS

{

....

.ncache :

{

*(NonCacheable)

. = ALIGN(4);

__noncachedata_end__ = .;

} > m_data

...

}

All I'd like to be able to do is change the ORIGIN to 0x20200000 (OCRAM2), and use the MPU to make

that space non-cacheable. Should I be able to do that?