- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX RT

- :

- Cache handling on the iMXRT-Family

Cache handling on the iMXRT-Family

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Cache handling on the iMXRT-Family

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

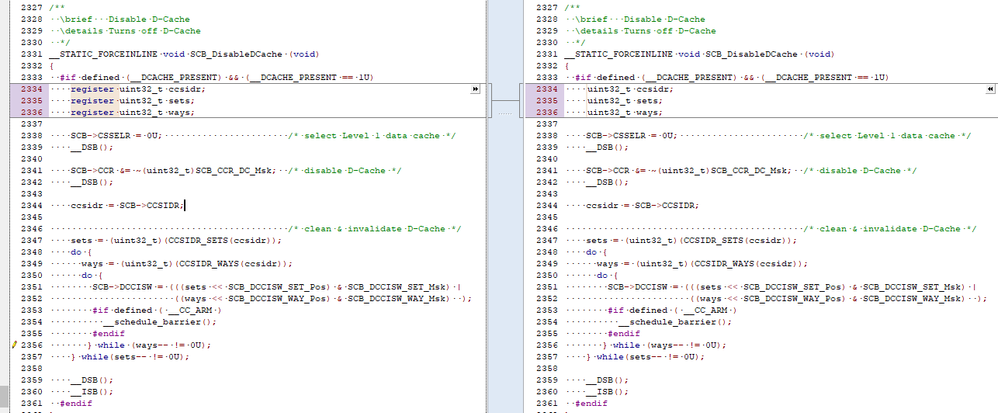

NXP has altered the CMSIS-Sources (from here https://github.com/ARM-software/CMSIS_5) and added an extra “register”-qualifier (see below-left the NXP Version – below-right, the one from the CMSIS-Library):

With the original code (https://github.com/ARM-software/CMSIS_5/blob/develop/CMSIS/Core/Include/core_cm7.h) the execution enters an endless loop when trying to disable the Data-Cache (--> calling the SCB_DisableDCache () function from the CMSIS Library)

This problem is only valid when using memory which is cached. When using the TCM only everything runs fine. Same with enabling the optimization – with optimization everything is fine.

I cross-checked with STM32F7 and Kinetis KV58. They work fine with the original code. Why is this change necessary? Is an errata for the cache handling for the iMXRT family available?

Thanks and best regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Markus,

Sorry for the late response. Could you please provide a more detailed explanation on how to reproduce the behavior you mentioned? I took one example from the SDK and removed the register qualifier from the variables on the function SCB_DisableDCache. Once I made this, I called the function and it ran successfully, I never finished in an endless loop as you stated.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Victor,

thanks for the feedback.

I was using Crossworks from Rowley (basically the same as Segger Embedded Studio) while I was facing this problem.

I´ve created a sample project for MCUexpresso and attached it. Just do a couple of Single-Step-Over to face the problem

Best regards

Markus

/Update: IAR seems to be OK without the register-qualifier. Looks like it is a gcc problem only

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Markus,

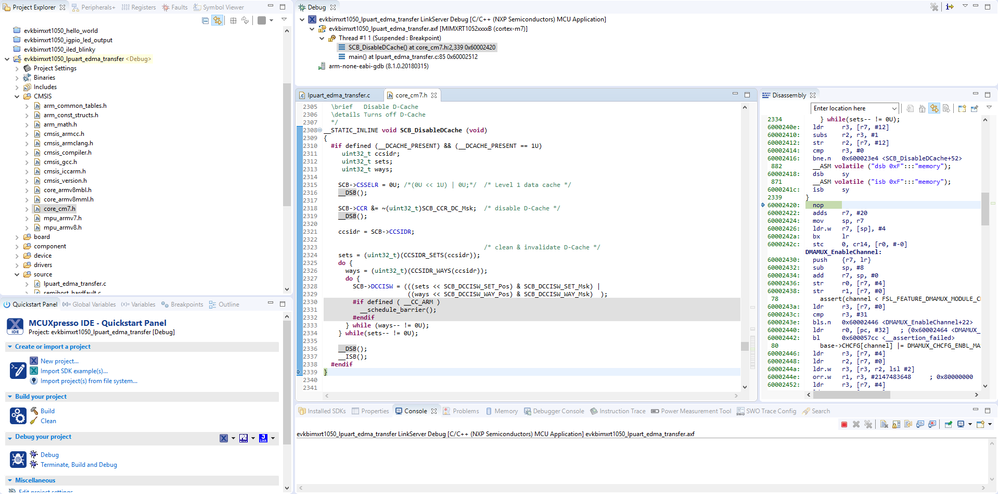

I made some tests with the project you attached. I was able to reproduce the behavior that you mentioned. I decided to make more tests so I imported the example lpuart_edma_transfer from the SDK to my workspace and I added the same instructions as you at the beginning.

SCB_DisableICache();

SCB_DisableDCache();I deleted the register modifier to the three variables inside the function SCB_DisableDCache. Once I made this I was able to run successfully the function SCB_DisableDCache. Se image below.

Did you modify anything else to the project that you attached before?

Regards,

Victor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Victor,

I haven´t removed only the “register”-qualifier. I have replaced the complete CMSIS-Code with the original one from here: https://github.com/ARM-software/CMSIS_5

Compare the content of the CMSIS Folder in the project.

The main question is: “Why has NXP changed the original CMSIS-Sources”? There must be a reason for doing so

Thanks and best regards

Markus

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Markus,

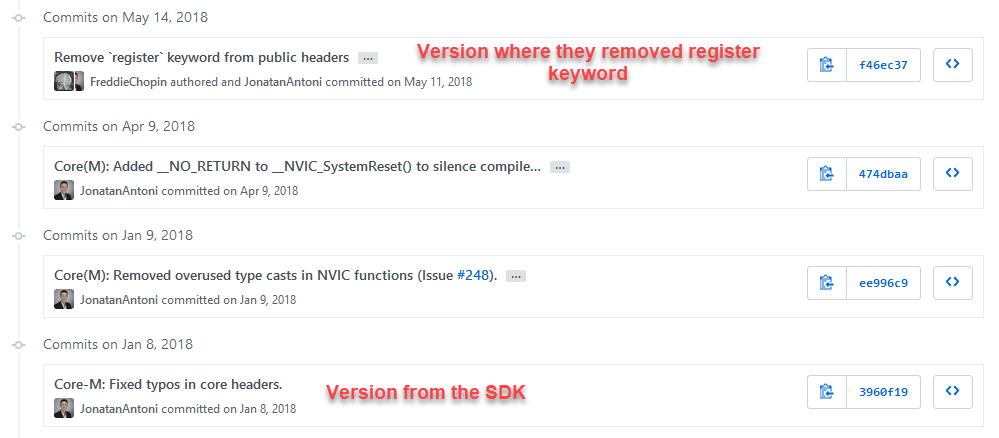

Actually, NXP didn't change anything. If you take a look at the revision history of the ARM repository, you will see that the changes like removing register qualifier were made by ARM.

The current version of the SDK supports an older version of the CMSIS libraries. If you change to the newest version, we cannot assure the correct functionality of the SDK.

Regards,

Victor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Victor,

Thanks for the information. I wasn´t aware of the CMSIS-History. Is there a release Plan for using newer Versions of CMSIS in the SDK?

The original question is still unanswered. Why has the iMXRT a different behavior then other Cortex M-7 controllers like the STM32F7 and Kinetis KV58? I´ve checked this two and they are working fine with the new CMSIS-Version, the iMXRT is entering an endless loop.

Best regards

Markus

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Markus,

Regarding your questions please see my comments below.

Is there a release Plan for using newer Versions of CMSIS in the SDK?

Unfortunately, for the moment I don't have any information on updating the CMSIS version. The new version of the SDK just released, but it still has the same version of CMSIS.

Why has the iMXRT a different behavior then other Cortex M-7 controllers like the STM32F7 and Kinetis KV58? I´ve checked this two and they are working fine with the new CMSIS-Version, the iMXRT is entering an endless loop.

The i.MXRT and the Kinetis are two completely different families of MCUs, so even if it works on the Kinetis, it doesn't mean that it would work on the i.MXRT. Even if the new version works on the Kinetis KV58, the official support that we give with the SDK is with an older revision, we cannot assure the functionality of the MCU if you change this.

Unfortunately, I cannot answer your question since the SDK comes with another version of the CMSIS libraries. Is out of our scope to modify the drivers provided.

Best regards,

Victor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Victor,

I agree that this are different controller families, but the core is identical as it is an IP of ARM. So every Cortex-M7 should behave basically the same way, regardless of the family and also regardless of the vendor.

The Kinetis KV58 behaves the same as the ST STM32F7 in terms of cache handling as this is part of the ARM IP. Moreover, I bet the Microchip SAM V70 would also behave the same way.

The only exception I´m aware of is the iMXRT-Family. I would like to know the reason for this, as I have to certify the product. It is hard to explain that an ARM-based controller is not working together with an official Library from ARM for this Core.

Best regards

Markus

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Markus,

As mentioned before, the official support that we give with the SDK is with an older revision of CMSIS libraries. Is out of our scope to make tests with newer CMSIS versions that are not supported by the SDK yet.

Victor