- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- i.MX Forums

- :

- i.MX RT Crossover MCUs

- :

- Re: Add 4-byte addressing to FLEXSPI flash driver

Add 4-byte addressing to FLEXSPI flash driver

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm using 256Mb external flash. That requires using 4-byte addressing. It's easy easy enough to see how to modify customLUT to use the 4-byte versions of the various commands, but how and where do I add the commands to enable and disable 4-byte addressing mode? The memory chip is a Macronix MX25L25645G, I'm using MCUXpresso SDK 2.6.2 (which I'm resistant to changing at this stage in the development cycle, unless it is unavoidable), the MCU is MIMXRT1062DVJ6A, and the IDE is MCUXpresso 11.2.0.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Nothing other than updating the customLUT is required to use 4-byte addressing mode for this flash chip.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Nothing other than updating the customLUT is required to use 4-byte addressing mode for this flash chip.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jeffery Thompson ,

Thanks for your updated information.

Do you already solve the issues but update the LUT table with 4Byte address mode?

Do you still have issues with this case?

If you still have questions about it, please kindly let me know.

Best Regards,

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

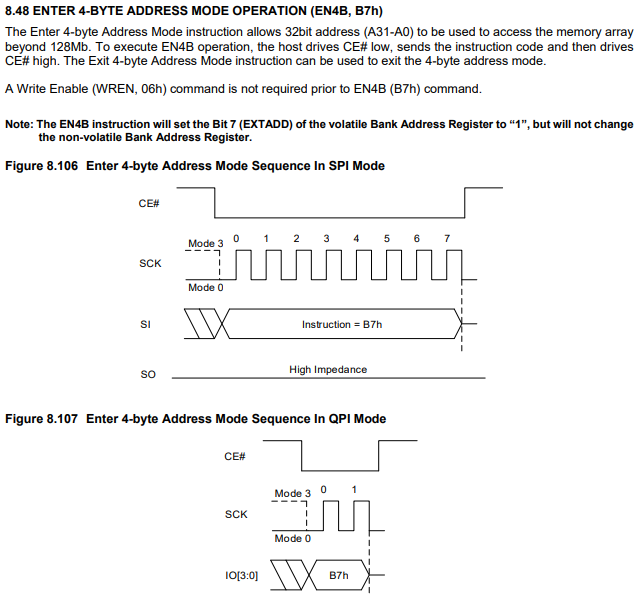

Hello, I need help for the same topic but for IS25LP512M QSPI Flash memory, and it looks that the solution is not as simple as modifying LUT entry for NOR_CMD_LUT_SEQ_IDX_READ_FAST_QUAD to support 32-bit address, because flash memory IC starts initialized in 3-bytes addressing mode and needs to Enter 4-byte Address Mode by 0xB7 instruction or by setting EXTADD bit in Volatile Bank Address Register.

How is it possible to perform such initialization in XIP header? Someone could help understanding how deviceModeSeq and configCmdSeqs are intended to be used, please?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I will try to answer to myself, and to other users like @adi2Intel who are still in trouble with this problem. In this answer I'll take IS25WP512M Quad Flash memory as reference (because this is the part number I'm interested to, but I think you may adapt this changes to another flash with little effort).

Datasheet link, for reference: https://www.issi.com/WW/pdf/25LP-WP512M.pdf

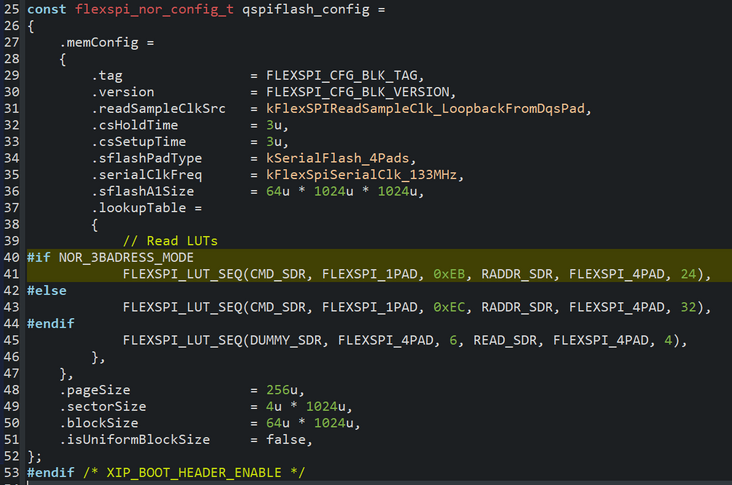

For what concerns eXecution In Place (XIP), I modified flexspi_nor_config_t structure as follows:

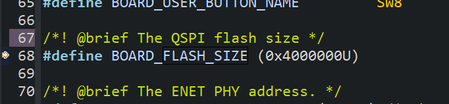

in particular I modified sflashA1Size to match my new 512Mb (64MB) flash size and I changed the first 32-bit word in commands LUT by substituting EBh command (24-bit addressing by default) with ECh command (32-bit addressing by default) and by specifing that 32-bits of address are following instead of 24-bits. After this, I also ensured BOARD_FLASH_SIZE in board.h matched my new flash size:

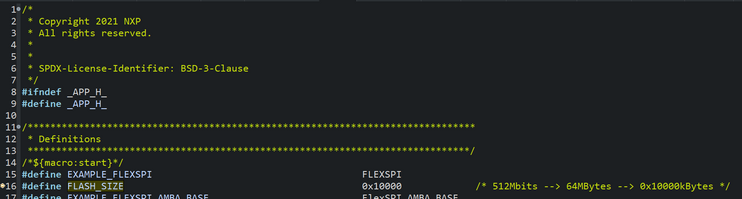

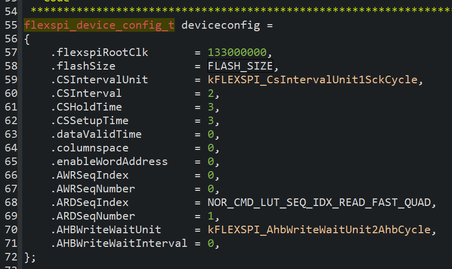

For what concerns the application (flexspi_nor_polling_transfer), I first adapted FLASH_SIZE definition in app.h to match my new flash size (notice that this macro will then be used to fill flashSize field in flexspi_device_config_t structure used in main.c to initialize FlexSPI peripheral, thus requiring flash size is in KBytes, not Bytes

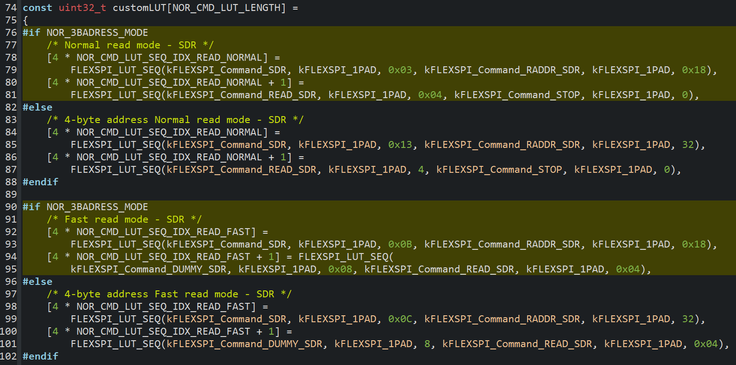

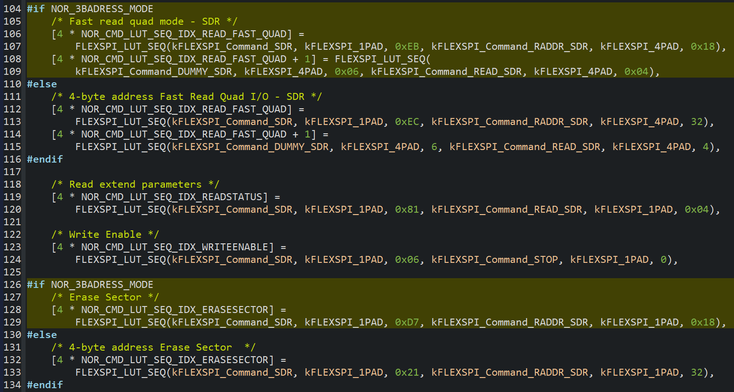

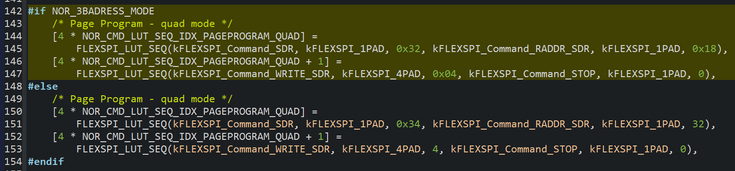

and last but not least, I modified all commands in customLUT to use the 32-bit addressing version of the command originally used by the demo example, e.g. I replaced 03h with 13h for Normal Read Single Data Rate, 0xD7 with 0x21 for Erase Sector, etc. and every time I also specified an ADDR length of 32 bits instead of 24:

I hope this post will help someone else, as with NXP technical support I am sadly forced to admit that... we are all swimming in a big **bleep**hole.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kerry,

we are having the same issue

I coulnd find how to solve this

on our flash the opcode to enter 4 byte mode ls 0xB7 and to exit is 0xE9