- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- imx8 ddr config

imx8 ddr config

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

imx8 ddr config

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello, All

TOOLS:

MX8QXP_C0_B0_LPDDR4_RPA_1.2GHz_v13.xlsx

mx8_ddr_stress_test_ER14_installation.zip

BOARD: Imx8qxp mek DDR stress test

LPDDR4 3G --->4G

test log:

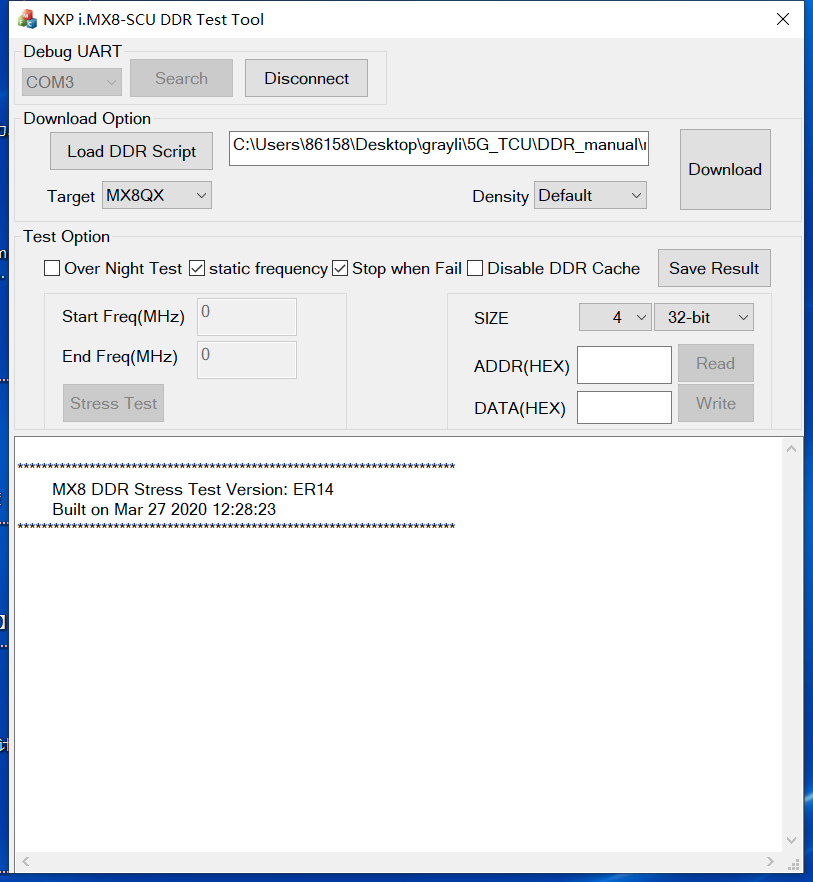

*************************************************************************

MX8 DDR Stress Test Version: ER14

Built on Mar 27 2020 12:28:23

*************************************************************************

-Set up the MMU and enable I and D cache-

- This is the Cortex-A35 core

- Check if I cache is enabled

- Enabling I cache since it was disabled

- Push base address of TTB to TTBR0_EL3

- Config TCR_EL3

- Config MAIR_EL3

- Enable MMU

- Data Cache has been enabled

- Check system memory register, only for debug

- VMCR Check:

- ttbr0_el3: 0x13d000

- tcr_el3: 0x2051c

- mair_el3: 0x774400

- sctlr_el3: 0xc01815

- id_aa64mmfr0_el1: 0x101122

- MMU and cache setup complete

*************************************************************************

ARM Clock(CA35): 1200MHz

DDR Clock: 1200MHz

============================================

DDR configuration

DDR type is LPDDR4

Data width: 32, bank num: 8

Row size: 16, col size: 10

Two chip selects are used

Number of DDR controllers used on the SoC: 1

Density per chip select: 2048MB

Density per controller is: 4096MB

Total density detected on the board is: 4096MB

No DDR data training errors detected for DDRC0

============================================

MX8QXP: Cortex-A35 is found

*************************************************************************

DDR Stress Test Iteration 1

--------------------------------

-Running DDR test on region 1-

--------------------------------

t0.1: data is addr test

....

t0.2: row hop read test

...

t1: memcpy SSN armv8_x32 test

....

t2: byte-wise SSN armv8_x32 test

..

t3: memcpy pseudo random pattern test

....................................................................

t4: IRAM_to_DDRv1 test

...

t5: IRAM_to_DDRv2 test

--------------------------------

-Running DDR test on region2-

--------------------------------

t0.1: data is addr

(Stuck here, didn't know it was wrong, stayed there for 20 minutes, restarted the test many times and still did the same thing)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Wang

one can recheck "BoardDataBusConfig" settings in RPA tool and

tweak drive strength settings.

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hello, igor

I don't know why I pressed the download button of the case. Now it is shown in the picture, and there is no other display

tks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hello, igor

can you tell me how to setting "BoardDataBusConfig"?

only modify

| Density per channel per chip select (Gb)1: | 6 | |

to 8.

tks