- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Re: imx6sx u-boot bootaux not present in custom build

imx6sx u-boot bootaux not present in custom build

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I was trying to load and run a hello_world example from FreeRTOS_BSP_1.0.1_iMX6SX/examples/imx6sx_sdb_m4/demo_apps/hello_world/armgcc (built with ./build_debug.sh) into Cortex M4 by putting the .bin file in the fat partition of the SD card, then booting the board from SD Card and stopping the u-boot before loading the kernel and giving these commands:

setenv m4image hello_world.bin

setenv m4runaddr 0x7f8000

setenv loadm4image 'fatload mmc ${mmcdev}:${mmcpart} ${m4runaddr} ${m4image}; dcache flush'

setenv m4boot 'run loadm4image; bootaux ${m4runaddr}'

saveenv

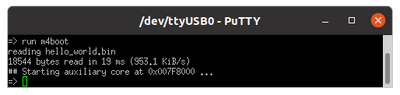

run m4boot

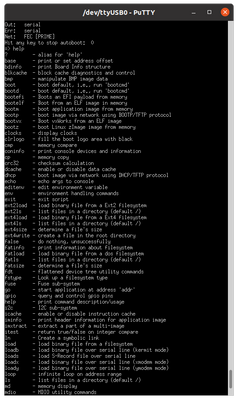

The problem is that the command bootaux is not present as you can see in the following image:

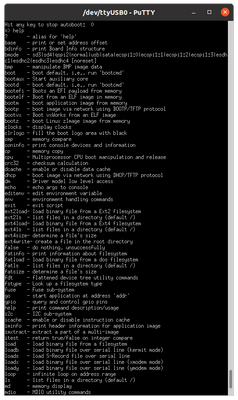

This command is available, instead, in the U-boot in the original SD Card provided with the SABRE iMX6sx:

How can I make this command available in my custom build too?

We built our custom core-image-minimal starting from https://github.com/Freescale/fsl-community-bsp-platform -b dunfell repository.

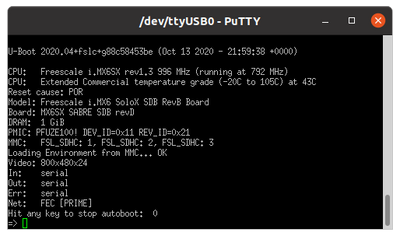

This is how our U-boot looks like:

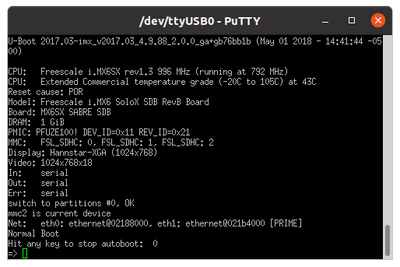

and this is the one in the Original SD Card:

By the way, I tried to accomplish the same task using the Original SD Card

but no output is coming out from the M4 uart. Have I to modify anything? Do you confirm that I have not to modify the .dtb files related to the kernel?

Thanks in advance.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I get the solution from this post. In this way there is no need to modify M4 uart clock rate in the dbg_uart_init.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Please try by adding the following to your defconfig:

CONFIG_IMX_BOOTAUX=y

As for the M4-UART not displaying anything it may not be loaded correctly, could you try with the following:

Load the application image from the SD card to DDR RAM:

fatload mmc 2:1 0x7F8000 <M4_example>.bin

Flush cached content to DDR RAM:

dcache flush

Copy Cortex-M4 image from DDR RAM to TCM:

cp.b 0x80000000 0x7F8000 0x8000

Flush cached content to TCM:

dcache flush

Start the Cortex-M4 core from the TCM:

bootaux 0x7F8000

Best regards,

Aldo.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

thank you very much for the advises. I tried to add intermediate copy to DDR memory before the TCM one and it works fine. I did it with the bootloader provided with original SD Card.

I'm not sure instead which defconfig file I have to modify in order to add the "CONFIG_IMX_BOOTAUX=y". I found different ones in the folder /sources/meta-freescale/recipes-kernel/linux/[...] but I do not know which is the one.

Thank you again

Massimo

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

For configuration changes you may refer to the following:

https://www.yoctoproject.org/docs/2.5/kernel-dev/kernel-dev.html#modifying-an-existing-recipe

https://community.nxp.com/t5/i-MX-Processors/Modify-u-boot-in-Yocto/td-p/229037

https://stackoverflow.com/questions/47047209/how-to-change-the-config-of-u-boot-in-yocto

Best regards,

Aldo.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Aldo and thank you for your reply, I will check the links you suggested for doing configuration changes.

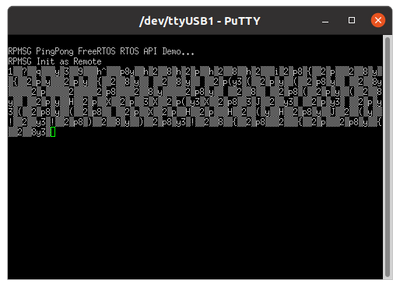

At the same time I was trying the freertos pingpong example provided in the FreeRTOS_BSP_1.0.1_iMX6SX/examples/imx6sx_sdb_m4/demo_apps/rpmsg/pingpong_freertos. After compiling and copying the rpmsg_pingpong_freertos_example.bin to the SD Card I Switch on the board and stop normal booting. After that I run the rpmsg_pingpong_freertos_example.bin and in the M4 core serial interface i see this output

RPMSG PingPong FreeRTOS API Demo...

RPMSG Init as Remote

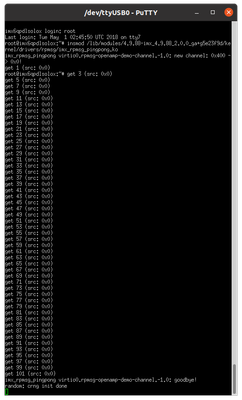

After that I boot the A9, log in and give the command:

insmod /lib/modules/4.9.88-imx_4.9.88_2.0.0_ga+g5e23f9d/kernel/drivers/rpmsg/imx_rpmsg_pingpong.ko

On the A9 side I see this:

and on the M4 side this:

Seeing the contents of the PingPongTask in the pingpong_freertos.c file

static void PingPongTask (void* param)

{

int result;

struct remote_device *rdev = NULL;

struct rpmsg_channel *app_chnl = NULL;

THE_MESSAGE msg = {0};

int len;

/* Print the initial banner */

PRINTF("\r\nRPMSG PingPong FreeRTOS RTOS API Demo...\r\n");

PRINTF("RPMSG Init as Remote\r\n");

result = rpmsg_rtos_init(0 /*REMOTE_CPU_ID*/, &rdev, RPMSG_MASTER, &app_chnl);

assert(0 == result);

PRINTF("Name service handshake is done, M4 has setup a rpmsg channel [%d ---> %d]\r\n", app_chnl->src, app_chnl->dst);

while (true)

{

/* receive/send data to channel default ept */

result = rpmsg_rtos_recv(app_chnl->rp_ept, &msg, &len, sizeof(THE_MESSAGE), NULL, 0xFFFFFFFF);

assert(0 == result);

PRINTF("Get Data From Master Side : %d\r\n", msg.DATA);

msg.DATA++;

result = rpmsg_rtos_send(app_chnl->rp_ept, &msg, sizeof(THE_MESSAGE), app_chnl->dst);

assert(0 == result);

}

/* If destruction required */

/*

PRINTF("\r\nMessage pingpong finished\r\n");

rpmsg_rtos_deinit(rdev);

*/

}

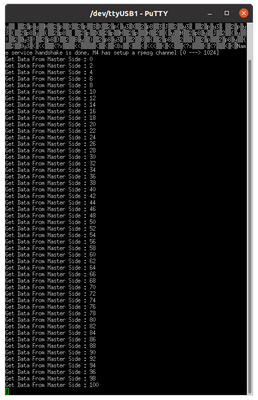

On the M4 side I expected to see the string "Name service handshake is done, M4 has setup a rpmsg channel [src ---> dst]" and then some strings "Get Data From Master Side: data", like this:

M4 has setup a rpmsg channel [0 ---> 1]

Get Data From Master Side: 1

Get Data From Master Side: 3

Get Data From Master Side: 5

Get Data From Master Side: 7

...but I only see a succession of incomprehensible characters.

Despite this, on the A9 side it would still seem that the data is correctly increased.

If then I modify the clock rate of the M4 uart from 24MHz to 80MHz in the dbg_uart_init function in board.c file,

// DbgConsole_Init(BOARD_DEBUG_UART_BASEADDR, 24000000, 115200);

DbgConsole_Init(BOARD_DEBUG_UART_BASEADDR, 80000000, 115200);I can see the correct string coming with the data from A9, but the first ones, just at the startup of the M4, are unreadable

How to fix this?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I get the solution from this post. In this way there is no need to modify M4 uart clock rate in the dbg_uart_init.