- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- i.MX フォーラム

- :

- i.MXプロセッサ

- :

- imx6 can support pcm codec

imx6 can support pcm codec

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi all,

I am working on PROGRAMMABLE VOICE DAA SI3050, It has SPI Interface for control as well as PCM highway data interface, which is to be interfaced with I.MX6UL. Can anybody tell whether I.MX6UL has SSI interface ?. If this interface is possible, Please share the information on this.

Regards

Mahesh

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

It is Synchronous Audio Interface (SAI) in i.MX6UL.

The synchronous audio interface (SAI) supports full-duplex serial interfaces with frame synchronization such as I2S, AC97, TDM, and codec/DSP interfaces

You can download i.MX6UL Reference Manual for more detail information.

It can be found in: i.MX 6UltraLite Applications Processor|NXP

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Liu King,

You can configure he SSI to network mode to support PCM data.

B.R

Jusin

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Yes, i.MX 6Solo can support I2S interface.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Qingrong,

So you mean i.MX6Solo can set audio format to PCM format and stream it with Bluetooth via I2S interface?

Thank you for your support!

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Shichin,

Did you get the IMX6Solo AUD3 interface to connect to BT PCM interface to work?

Thanks,

Gus

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Justin,

We have a custom Designed Board based on i.mx6D, Where the SLIC IC, LE9641 (Supporting PCM +SPI) is connected to the AUDMUX interface and the SPI interface of the i.mx6D respectively.

We are able to communicate with the SLIC IC trough SPI interface, but i m not getting CLOCK from the AUDMUX fro the PCM interface.

Could you please suggest anything on this?

Thanks

Sumit

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi

Sumit

You need to configure SSI in master mode than only you will get clock from AUDMUX interface.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Saurabh,

It is configured in Mater mode only. But still no clock comes on AUD5_TXC Pin :smileyplain:.

Thanks

Sumit

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi

Sumit

Can you shared the information for where the code modification done?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Saurabh patel,

Here are my code changes.

&audmux {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_audmux_3>;

status = "okay";

};

pinctrl_audmux_3: audmux-3 {

fsl,pins = <

MX6QDL_PAD_KEY_ROW1__AUD5_RXD 0x130b0

MX6QDL_PAD_KEY_COL0__AUD5_TXC 0x130b0

MX6QDL_PAD_KEY_ROW0__AUD5_TXD 0x110b0

MX6QDL_PAD_KEY_COL1__AUD5_TXFS 0x130b0

>;

};

&ssi1 {

fsl,mode = "i2s-master";

status = "okay";

};

mux-int-port = 5 mux-ext-port = 2 and we are setting dai format as SND_SOC_DAIFMT_I2S | SND_SOC_DAIFMT_NB_NF |SND_SOC_DAIFMT_CBS_CFS

and audmux configurations as

ret = imx_audmux_v2_configure_port(int_port,

IMX_AUDMUX_V2_PTCR_SYN |

IMX_AUDMUX_V2_PTCR_TFSEL(ext_port) |

IMX_AUDMUX_V2_PTCR_TCSEL(ext_port) |

IMX_AUDMUX_V2_PTCR_TFSDIR |

IMX_AUDMUX_V2_PTCR_TCLKDIR,

IMX_AUDMUX_V2_PDCR_RXDSEL(ext_port));

ret = imx_audmux_v2_configure_port(ext_port,

IMX_AUDMUX_V2_PTCR_SYN,

IMX_AUDMUX_V2_PDCR_RXDSEL(int_port));

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Sumit

Have you set "snd_soc_dai_set_sysclk" clock direction out.

It will solve your issue.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Saurabh Patel,

Our clock direction is OUT only.Here is our function call.

ret = snd_soc_dai_set_sysclk(cpu_dai, 0,

pll_out, SND_SOC_CLOCK_OUT);

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

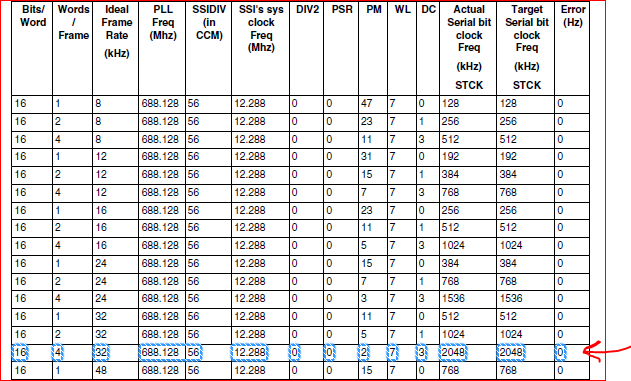

Hi Saurabh,

After using the SSI2 controller instead of SSI1, We are able to get the PCM Clock of 2.048Mhz and Frame Sync of 32Khz, But the SLIC IC supports PCM Clock rates of 1.024MHz, 1.536MHz, 2.048MHz. 3.073MHz, 4.096Mhz, 6.144MHz and 8.192Mhz with a Frame SYNC of 8KHz.

We have changed the "SSIx_SRCCR" register corresponding to SSI2 controller of i.MX6 processor with values of "0x00007F03" to make frame sync freq of 8Khz, But still no change, But we did not see any change in the Frame sync clock ,

Here in the below table we have used with marked configuration.

Do you have any idea, how we can get the frame Sync of 8Khz.

Thanks

Sumit

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Can Anybody reply on my last question posted.

Thanks

Sumit

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Qingrong

There are two modes mode A and mode B of pcm mode.

Which mode does the network mode of ssi support?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi

You can config the TSCKP and RSCKP to support both mode A&B.

TSCKP

Transmit Clock Polarity. This bit controls which bit clock edge is used to clock out data for the transmit

section. Note: TSCKP is 0 CLK_IST = 0; TSCKP is 1CLK_IST = 1

0 Data clocked out on rising edge of bit clock.

1 Data clocked out on falling edge of bit clock.

RSCKP

Receive Clock Polarity. This bit controls which bit clock edge is used to latch in data for the receive

section.

0 Data latched on falling edge of bit clock.

1 Data latched on rising edge of bit clock.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

hi Freescale,

can you please provide the steps to enable Network mode (PCM) to capture 6 channel audio ?

in dtsi file can i change the CPU_DAI configuration as below ?

&ssi2 {

fsl,mode = "pcm-slave";

status = "okay";

};

regards

Nagendra